一种FPGA加速板卡及其行情数据处理方法与流程

一种fpga加速板卡及其行情数据处理方法

技术领域

1.本技术涉及服务器硬件领域,特别涉及一种fpga加速板卡及其行情数据处理方法。

背景技术:

2.当前,针对金融市场行情通常采用传统的软件进行数据统计分析,或者以软件为核心的软硬件加速技术难以满足当前实时响应的要求。以深交所level-2行情为例,其中包含逐笔委托和逐笔成交两类数据,因此接收方可以利用逐笔数据和交易规则自行重构市场行情。目前主流方案仍然是软件重构,但处理能力远远不能满足当前市场实时数据要求,其市场行情的重构效率较为低下。

技术实现要素:

3.本技术的目的是提供一种fpga加速板卡及其行情数据处理方法,能够实现市场行情的高性能重构。

4.为解决上述技术问题,本技术提供一种fpga加速板卡,具体技术方案如下:

5.网络接口,用于接收交易所行情数据;

6.cam表,用于存储证券代码和行情存储地址的映射关系;

7.与所述网络接口和报文缓冲区均相连,并包含内置量化交易算法的risc-v处理器,用于解析所述交易所行情数据,得到行情信息、交易信息和包含所述证券代码的委托信息;当检测到交易时,根据所述委托信息中的委托信息记录号查询委托价格;并根据所述委托价格和所述行情存储地址计算最新市场行情信息,并输出最新市场行情信息;

8.与所述cam表相连的所述报文缓冲区,用于存储所述行情存储地址和所述行情信息。

9.可选的,还包括:

10.与所述cam表和所述报文缓冲区均相连,用于缓存所述行情存储地址、所述委托信息和所述交易信息的fifo队列。

11.可选的,还包括:

12.与所述cam表相连,用于配置关键信息的可配置寄存器;所述关键信息包括所述fpga加速板卡的ip地址和所述交易所行情数据的交易所ip地址。

13.可选的,还包括:

14.与所述fifo队列相连的片外内存,用于存储所述委托信息。

15.可选的,还包括:

16.与所述risc-v处理器相连的mac接口和/或pcie接口,用于传输所述最新市场行情信息。

17.本技术还提供一种行情数据处理方法,基于上文所述fpga加速板卡,包括:

18.获取交易所行情数据;

19.解析所述交易所行情数据,得到行情信息、交易信息和委托信息;所述委托信息包括委托信息记录号和证券代码;

20.根据所述委托信息记录号查询委托价格,并根据所述证券代码检索cam表确定对应的行情存储地址;

21.将所述委托价格和所述行情存储地址发送至risc-v处理器,以便所述risc-v处理器应用内置量化交易算法对所述委托价格和所述行情存储地址进行行情计算,得到最新市场行情信息。

22.可选的,解析所述交易所行情数据,得到行情信息、交易信息和委托信息之后,还包括:

23.将所述委托信息存储至片外内存;

24.在检测到交易信息时,读取所述片外内存中的委托信息。

25.可选的,还包括:

26.配置交易所行情数据的交易所ip地址;

27.则所述获取交易所行情数据时,还包括;

28.判断所述交易所行情数据对应的ip地址是否属于所述交易所ip地址;

29.若否,拒绝接收所述交易所行情数据。

30.可选的,当检测到交易信息时,还包括:

31.判断报文缓冲区中的行情队列是否包含交易对应的委托价格和所述行情存储地址;

32.若是,反馈所述委托价格在所述行情队列的位置及对应行情信息;

33.若否,按照所述委托价格将对应行情信息插入至所述行情队列。

34.可选的,得到最新市场行情信息之后,还包括:

35.获取目标设备的封装格式要求;

36.根据所述封装格式要求中包含的封装格式封装当前行情队列,并通过mac接口或pcie接口传至所述目标设备。

37.本技术提供一种fpga加速板卡,包括:网络接口,用于接收交易所行情数据;cam表,用于存储证券代码和行情存储地址的映射关系;与所述网络接口和报文缓冲区均相连,并包含内置量化交易算法的risc-v处理器,用于解析所述交易所行情数据,得到行情信息、交易信息和包含所述证券代码的委托信息;当检测到交易时,根据所述委托信息中的委托信息记录号查询委托价格;并根据所述委托价格和所述行情存储地址计算最新市场行情信息,并输出最新市场行情信息;与所述cam表相连的所述报文缓冲区,用于存储所述行情存储地址和所述行情信息。

38.本技术通过利用cam表存储证券代码和行情存储地址的映射关系,在交易时,内置量化交易算法的risc-v处理器直接进行交易的行情重构,利用fpga低延迟特性及risc-v开源、指令集可扩展等特性,构建高性能、低延迟以及灵活可扩展的金融加速处理设备,提高了金融交易行情的重构效率。

39.本技术还提供一种行情数据处理方法,具有上述有益效果,此处不再赘述。

附图说明

40.为了更清楚地说明本技术实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

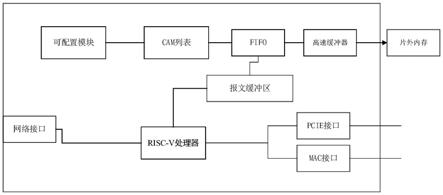

41.图1为本技术实施例所提供的一种fpga加速板卡的结构示意图;

42.图2为本技术实施例所提供的一种行情数据处理方法的流程图。

具体实施方式

43.为使本技术实施例的目的、技术方案和优点更加清楚,下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

44.图1为本技术实施例所提供的一种fpga加速板卡的结构示意图,该板卡包括:

45.网络接口,用于接收交易所行情数据;

46.cam表,用于存储证券代码和行情存储地址的映射关系;

47.与所述网络接口和报文缓冲区均相连,并包含内置量化交易算法的risc-v处理器,用于解析所述交易所行情数据,得到行情信息、交易信息和包含所述证券代码的委托信息;当检测到交易时,根据所述委托信息中的委托信息记录号查询委托价格;并根据所述委托价格和所述行情存储地址计算最新市场行情信息,并输出最新市场行情信息;

48.与所述cam表相连的所述报文缓冲区,用于存储所述行情存储地址和所述行情信息。

49.在此对于该网络接口不作具体限定,可以采用mac接口,当然也可以采用其他接口,其用于接收交易所行情数据。以mac接口为例,接收到交易所行情数据,即可将交易所行情数据转化为相应的mac帧。而对于不同协议类型的交易所行情数据,例如深交所和上交所交易所行情数据,其对应的mac的帧头数据存在差异,据此可以进行交易所行情数据对应协议类型的区分。

50.cam表,用于存储证券代码和行情存储地址的映射关系,则可以根据委托信息或者交易信息中的证券代码查询相应的行情存储地址。对于交易所行情数据解析得到的行情信息,需要在报文缓冲区中建立相应的行情队列。

51.如图1所示,该板卡还可以包括与cam表和报文缓冲区均相连,用于缓存行情存储地址、委托信息和交易信息的fifo队列。通过fifo队列可以实现数据缓存。而解析得到的委托信息,可以存于与fifo队列相连的片外内存。

52.则在交易来临时,通过片外内存获取相应的委托信息。

53.进一步,该板卡还可以包括与cam表相连,用于配置关键信息的可配置寄存器。关键信息包括fpga加速板卡的ip地址和交易所行情数据的交易所ip地址。即配置fpga加速板卡自身的ip地址,还可以限定fpga加速板卡可处理的交易所行情数据的来源ip地址,以限制可处理的交易所行情数据的协议类型。此外,可配置寄存器还可以存储不同类型的证券信息。

54.如图1所示,fpga加速板卡还可以包括一个与risc-v处理器相连的mac接口和/或pcie接口,用于传输所述最新市场行情信息。当然,可以选择mac接口和pcie接口中的任一种,也可以同时支持两种接口,以实现面向不同类型设备的最新市场行情信息输出。

55.参见图2,图2为本技术实施例所提供的一种行情数据处理方法的流程图。本技术还提供一种行情数据处理方法,基于上文所述fpga加速板卡所实现,该方法包括:

56.s101:获取交易所行情数据;

57.本步骤旨在通过网络接口获取交易所行情数据。在获取交易所行情数据之前,可以通过对可配置模块进行交易所行情数据的ip限制,以确保接收到的交易所行情数据为本fpga加速板卡可加速处理的数据。

58.若配置交易所行情数据的交易所ip地址,在执行本步骤时,可以判断交易所行情数据对应的ip地址是否属于交易所ip地址。若不属于交易所ip地址,可以拒绝接收交易所行情数据。

59.当然也可以不针对交易所行情数据进行ip限制,可以对于可处理协议交由risc-v处理器解析处理,而对于证券binary/step协议、或者上期所期货协议可以由现有协议解析ip处理,即对于输入的其他金融协议类报文,可采用标准指令集进行处理。

60.s102:解析所述交易所行情数据,得到行情信息、交易信息和委托信息;

61.本步骤需要解析交易所行情数据,得到行情信息、交易信息和委托信息;而委托信息包括委托信息记录号和证券代码。需要注意的是,该交易信息和委托信息通常包含若干条交易和委托。以深交所level-2行情为例,解析后包含逐笔委托、逐笔交易、指数行情及市场行情四类数据。指数行情和市场旱情对应本步骤中的行情信息。

62.对于解析得到的行情信息,可以存于报文缓冲区形成行情队列。而对于委托信息,由于仅在交易时使用,可以存于片外内存。但为了提高交易时委托信息的数据读取效率,可以通过配置高速缓冲存储器与片外内存相连,从而快速读取片外内存中的委托信息。

63.s103:根据所述委托信息记录号查询委托价格,并根据所述证券代码检索cam表确定对应的行情存储地址;

64.s104:将所述委托价格和所述行情存储地址发送至risc-v处理器,以便所述risc-v处理器应用内置量化交易算法对所述委托价格和所述行情存储地址进行行情计算,得到最新市场行情信息。

65.本步骤需要确定委托价格和行情存储地址。当逐笔交易信息到来时,需要根据委托消息记录号查询委托价格,同时根据证券代码通过cam表获取行情存储地址,最终将委托价格及行情存储地址发送至risc-v处理器。

66.risc-v处理器可以内置量化交易算法,在此对于内置何种量化交易算法不作具体限定,包括不限于程序化t+0策略、alpha策略、期现套利等。容易理解的是,为了提高处理效率,可同时配置多种量化交易算法。还可以针对risc-v处理器设计专用自定义扩展指令,配合金融加速单元,快速完成千档行情重构,并在此基础上完成量化交易算法实现。

67.当检测到交易信息时,可以判断报文缓冲区中的行情队列是否包含交易对应的委托价格和行情存储地址。若行情队列已经存在该行情信息,反馈所述委托价格在所述行情队列的位置及对应行情信息。相反,若行情队列未包含该行情信息,按照委托价格将对应行情信息插入至行情队列。通常按照委托价格进行排序。

68.由fpga架构图可看出,所有行情信息存储于报文缓冲区中,外部fpga模块根据证券代码通过cam表查询可得到本队列在buffer中的偏移地址,随后根据委托价格,在现有行情队列中查找,若查找成功,则并反馈委托价格在现有行情队列中的位置及对应行情信息;若无此委托价格,则反馈插入位置。

69.在得到最新市场行情信息之后,还可以获取目标设备的封装格式要求,从而根据封装格式要求中包含的封装格式封装当前行情队列,并通过mac接口或pcie接口传至目标设备。需要注意的是,在封装时,可以针对全部行情队列进行封装,也可以选择部分行情队列进行封装。可以看出,通过本实施例,可以对报文缓冲区中的行情队列根据委托和交易进行实时更新,实现行情重构。

70.本技术实施例通过利用cam表存储证券代码和行情存储地址的映射关系,在交易时,利用内置量化交易算法的risc-v处理器进行交易的行情重构,利用fpga低延迟特性及risc-v开源、指令集可扩展等特性,构建高性能、低延迟以及灵活可扩展的金融加速处理设备,提高了金融交易行情的重构效率。

71.说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。对于实施例提供的系统而言,由于其与实施例提供的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

72.本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想。应当指出,对于本技术领域的普通技术人员来说,在不脱离本技术原理的前提下,还可以对本技术进行若干改进和修饰,这些改进和修饰也落入本技术权利要求的保护范围内。

73.还需要说明的是,在本说明书中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1