基于三模冗余的外设控制方法及系统与流程

1.本发明涉及宇航计算机技术领域,尤其涉及一种基于三模冗余的外设控制方法及系统。

背景技术:

2.宇航计算机硬件架构通常由cpu、cpu外设(flash、ram、fpga等)和系统外设(总线设备,指令执行机构或者数据采集终端)组成。在宇航计算机系统中,为了增加系统的可靠性,通常采用双备份系统或三备份系统。

3.双备份系统包括两份计算系统,一般情况下一份加电运行,一份断电不运行,由于系统数据无法开展一致性比对,使得输出结果可信度不高。此外,在冷备份情况下,当加电运行部分异常后,系统通常自动切换到备份机运行,而系统切换过程需要一定时间。

4.为了提高系统数据输出的可信度,降低系统切换对执行任务的影响,通常情况使用三备份方式搭建系统计算机架构。三备份系统由计算系统、分发器/表决器和系统外设组成,计算系统由系统时钟和三个cpu系统组成。计算系统同数据的关系是:当计算系统输出数据时,表决器工作;当计算系统接收数据时,分发器工作。分发器/表决器连接外设端口通过控制通道控制外部关联设备。三备份系统引入了三套cpu系统,并由分发器/表决器同外设端口建立连接,并可以控制外设端口的冗余备份关系,使得外设端口设计上易于实现。

技术实现要素:

5.针对上述问题,本发明提供了一种基于三模冗余的外设控制方法及系统,在无单点的情况下,实现计算系统对外设的控制,满足系统连续不间断工作的要求。

6.第一方面,本发明提供一种基于三模冗余的外设控制方法,应用于基于三模冗余的外设控制系统,所述系统包括:相同的三个计算机子系统和一个或多个系统外设,所述三个计算机子系统之间通过通信总线两两相连,所述三个计算机子系统中包括一个当班机和两个非当班机,每个计算机子系统包括cpu系统以及冗余控制端口;所述方法包括:

7.所述三个计算机子系统通过所述系统外设同时获取来自外部关联设备相同线路的外部数据;

8.所述三个计算机子系统的cpu系统根据获取的外部数据分别进行计算得到三份计算后的数据,并对所述三份计算后的数据进行两两比对确定所述三个计算机子系统计算后的数据是否一致;

9.若是,则所述当班机的cpu系统通过冗余控制端口将控制数据传输至目标系统外设,并利用所述目标系统外设将所述控制数据通过控制通道传输至目标外部关联设备,以对所述目标外部关联设备进行控制。

10.进一步地,所述当班机的cpu系统通过冗余控制端口将控制数据传输至目标系统外设,包括:

11.所述当班机的cpu系统根据需要控制的目标外部关联设备确定目标外部关联设备

对应的目标系统外设;

12.所述当班机的cpu系统控制冗余控制端口将控制数据传输至所述目标系统外设。

13.进一步地,所述方法还包括:

14.若所述当班机计算后的数据与所述两个非当班机计算后的数据不一致,则确定所述当班机发生异常;

15.对所述当班机进行停止处理,并从所述两个非当班机中确定一个新的当班机。

16.第二方面,本发明提供一种基于三模冗余的外设控制系统,所述系统包括:相同的三个计算机子系统和一个或多个系统外设,所述三个计算机子系统之间通过通信总线两两相连,所述三个计算机子系统中包括一个当班机和两个非当班机,每个计算机子系统包括cpu系统以及冗余控制端口;

17.所述三个计算机子系统,用于通过所述系统外设同时获取来自外部关联设备相同线路的外部数据,根据获取的外部数据分别进行计算得到三份计算后的数据,并对所述三份计算后的数据进行两两比对确定所述三个计算机子系统计算后的数据是否一致,若是,则所述当班机的cpu系统通过冗余控制端口将控制数据传输至目标系统外设,并利用所述目标系统外设将所述控制数据通过控制通道传输至目标外部关联设备,以对所述目标外部关联设备进行控制。

18.进一步地,所述cpu系统包括cpu和cpu外设,所述cpu外设包括ram、flash、fpga。

19.进一步地,所述冗余控制端口包括多个数据缓冲器。

20.本发明提供了一种基于三模冗余的外设控制方法及系统,该系统包括:相同的三个计算机子系统和一个或多个系统外设,本发明采用三个计算机子系统获取外部关联设备的外部数据,三个计算机子系统根据获取的外部数据分别进行计算得到三份计算后的数据,并对三份计算后的数据进行两两比对确定三个计算机子系统计算后的数据是一致的,三个计算机子系统中的当班机通过冗余控制端口将控制数据传输至目标系统外设,并通过目标系统外设将控制数据传输至目标外部关联设备,以对所述目标外部关联设备进行控制,与现有技术相比,本系统中不存在单点,三个计算机子系统与两个系统外设具有等价的连接关系,且三个计算机子系统获取的数据保持一致,方便三个计算机子系统随时切换,以保持系统对外设的控制,避免了现有系统中单点设备发生异常导致系统无法工作的问题,满足系统连续不间断工作的要求。

21.应当理解,上述发明内容部分中所描述的内容并非旨在限定本发明的实施例的关键或重要特征,亦非用于限制本发明的范围。本发明的其它特征将通过以下的描述变得容易理解。

附图说明

22.为了更清楚地说明本发明或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作一简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

23.图1为现有双备份系统的结构示意图;

24.图2为现有三备份系统的结构示意图;

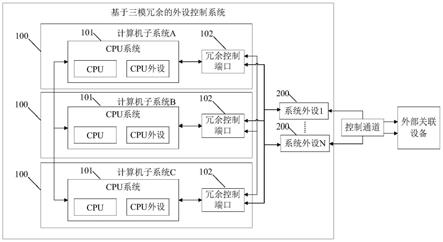

25.图3为本公开实施例提供的一种基于三模冗余的外设控制系统的结构示意图;

26.图4为本公开实施例提供的一种基于三模冗余的外设控制方法的流程示意图;

27.图5为一种基于三模冗余的外设控制系统的实际结构图。

28.通过上述附图,已示出本公开明确的实施例,后文中将有更详细的描述。这些附图和文字描述并不是为了通过任何方式限制本公开构思的范围,而是通过参考特定实施例为本领域技术人员说明本公开的概念。

具体实施方式

29.下面将参照附图更详细地描述本发明的实施例。虽然附图中显示了本发明的某些实施例,然而应当理解的是,本发明可以通过各种形式来实现,而且不应该被解释为限于这里阐述的实施例,相反提供这些实施例是为了更加透彻和完整地理解本发明。应当理解的是,本发明的附图及实施例仅用于示例性作用,并非用于限制本发明的保护范围。

30.宇航计算机系统硬件架构通常由cpu、cpu外设(flash、ram、fpga等)和系统外设(总线设备,指令执行机构或者数据采集终端)组成,由于宇宙空间环境的影响,容易造成计算机系统异常,为了增加计算机系统的可靠性,通常采用双备份系统或三备份系统,以保证整个计算机系统的正常运行。

31.双备份系统架构中设有两份相同的计算机子系统,如图1所示,双备份系统通常为冷备份系统(一份加电运行,一份断电不运行),在上述系统中,a机和b机均通过控制通道连接外部关联设备,a机和b机在同一时刻只有单份输出数据,且认为当前输出数据可信。当前输出数据的系统称之为当班机;不输出数据的系统为非当班机。由于系统数据无法开展一致性比对,使得输出结果可信度不高。此外,在冷备份情况下,当加电运行部分异常后,系统通常自动切换到备份机运行,而系统切换过程需要一定时间,因此双备份系统通常应用在外部环境变化较慢,对时间前后的参数关联度不高,且对工作时隙要求不高的场合。

32.为了提高系统数据输出的可信度,降低系统切换对执行任务的影响,使用三备份方式搭建计算机系统架构,如图2所示,三备份系统由计算系统、分发器/表决器和两个系统外设组成,计算系统由系统时钟和三个cpu系统组成,三个cpu系统共用系统时钟,计算系统同数据的关系是:当计算系统输出数据时,表决器工作;当计算系统接收数据时,分发器工作。分发器/表决器连接外设端口通过控制通道控制关联的外设。三备份系统引入了三套cpu系统,并由分发器/表决器同外设端口建立连接,并可以控制外设端口的冗余备份关系,使得外设端口设计上易于实现。但上述三备份系统中,系统时钟和分发器/表决器均为单点,是系统中的薄弱环节,当系统时钟异常时,计算系统将无法正常工作;当分发器/表决器异常时,系统数据输入输出出现异常。而且系统时钟通常由时钟电路或芯片组成,表决器通常由大规模现场可编程单元组成,如fpga或cpld电路,其可靠性随着逻辑门的增加会大幅度降低,即使采取了提高等级标准等可靠性措施,系统在轨运行中仍会出现异常,例如单粒子翻转引起数据异常,辐照环境引起芯片电流增大等,异常发生后只能通过整机断电重启的方式解决,难以满足系统连续不间断工作的要求。

33.针对这些问题,发明人研究发现,在采用三备份系统架构的基础上,可取消分发器/表决器,通过计算机子系统间进行计算数据比对的方式保持各计算机子系统的一致性,通过冗余控制端口控制系统外设,再通过控制通道连接外部关联设备,能够解决现有系统

中的单点设备发生异常导致系统无法工作的问题,满足系统连续不间断工作的要求。

34.下面以具体地实施例对本发明的技术方案进行详细说明。下面这几个具体的实施例可以相互结合,对于相同或相似的概念或过程可能在某些实施例不再赘述。

35.图3为本公开实施例提供的一种基于三模冗余的外设控制系统的结构示意图。如图3所示,所述系统包括:相同的三个计算机子系统100和一个或多个系统外设200,所述三个计算机子系统之间通过通信总线两两相连,所述三个计算机子系统中包括一个当班机和两个非当班机,每个计算机子系统包括cpu系统101以及冗余控制端口102,在图3中,为了清楚地表示三个计算机子系统和多个系统外设,将三个计算机子系统分别表示为计算机子系统a、计算机子系统b和计算机子系统c,将多个系统外设分别表示为系统外设1~系统外设n。

36.其中,所述cpu系统可包括cpu和cpu外设,所述cpu外设包括ram、flash、fpga,所述冗余控制端口由多个数据缓冲器组成。

37.基于三模冗余的外设控制系统用于执行基于三模冗余的外设控制方法,如图4所示,所述方法包括:

38.s101、所述三个计算机子系统通过所述系统外设同时获取来自外部关联设备相同线路的外部数据;

39.s102、所述三个计算机子系统的cpu系统根据获取的外部数据分别进行计算得到三份计算后的数据,并对所述三份计算后的数据进行两两比对确定所述三个计算机子系统计算后的数据是否一致;

40.s103、若是,则所述当班机的cpu系统通过冗余控制端口将控制数据传输至目标系统外设,并利用所述目标系统外设将所述控制数据通过控制通道传输至目标外部关联设备,以对所述目标外部关联设备进行控制。

41.由于不同的外部关联设备是通过不同系统外设与控制系统进行数据交互的,冗余控制端口是作为cpu一个系统外设存在的,控制系统需要先通过冗余控制端口将控制数据通过目标系统外设上的端口发送至目标外部关联设备,具体包括:所述当班机的cpu系统根据需要控制的目标外部关联设备确定目标外部关联设备对应的目标系统外设;所述当班机的cpu系统控制冗余控制端口将控制数据传输至所述目标系统外设。

42.s104、若所述当班机计算后的数据与所述两个非当班机计算后的数据不一致,则确定所述当班机发生异常;

43.s105、对所述当班机进行停止处理,并从所述两个非当班机中确定一个新的当班机。

44.本实施例中,三个计算机子系统中预设了一个当班机和两个非当班机,首先三个计算机子系统同时获取外部关联设备相同线路的外部数据,然后当班机和两个非当班机分别进行计算得到三份计算后的数据,最后对三份计算后的数据进行两两比对,当三个计算机子系统计算后的数据一致,说明三个计算机子系统工作正常,当班机可向外部关联设备发送控制指令,以对目标外部关联设备进行控制;当三个计算机子系统计算后的数据不一致,说明三个计算机子系统中存在异常,进一步来说,若当班机计算后的数据与两个非当班机计算后的数据不一致,说明当班机发生异常,需要进行系统切换,将一个非当班机切换为新的当班机后,新的当班机可向外部关联设备发送控制指令,以对目标外部关联设备进行

控制。

45.举例来说,如图5所示,在实际应用中,系统中的每一个计算机子系统都可以通过三总线控制系统外设,且同一时刻只有当班机可向外部关联设备写入数据,为了保证系统中cpu获取数据的一致性,要求在同一个时刻,三个cpu可同时获取外部三总线上的外设数据,上述功能通过冗余控制端口来实现。在图5中,cpu、fpga和冗余控制端口组成单份计算机子系统,三模冗余控制系统通过冗余控制端口控制了两个三总线类型的系统外设,表1为冗余控制端口需要的信号及其功能,具体如下:

46.1)fpga和cpu输出控制信号至冗余控制端口的a端口;

47.2)三个计算机子系统分别控制各自的冗余控制端口,且冗余控制端口相同;

48.3)三个计算机子系统对应的冗余控制端口控制相同外部关联设备时,冗余控制端口的b端口定义相同;

49.4)对外控制时,三个计算机子系统需要输出信号以表明其是否为当班机;

50.5)系统带有断电重启功能的,第一种情况,冗余控制端口的b端口具有断电高阻特性,以防止端口漏电流增加引起端口异常;第二种情况,冗余控制端口的b端口不具有断电高阻特性,该端口需要做常加电设计,并通过其所在的计算机子系统进行供电控制冗余控制端口的使能端,即系统断电时,保证冗余控制端口的b端口具有高阻特性。

51.表1

[0052][0053]

[0054]

冗余控制端口主要由数据缓冲器组成,具备如下特点:

[0055]

1)当数据缓冲的数据为双向时,数据缓冲器需要具备双向特性,且方向可控制;

[0056]

2)信号host_cpu_out和ctl_en通过数据缓冲器控制数据总线,该数据缓冲器不使能时,冗余控制端口的a端口和b端口处于高阻状态;

[0057]

3)当数据缓冲的数据为双向时,当班机控制信号host_cpu_out和ctl_en、phy_dir参与控制数据缓冲器的方向信号和使能信号,以保证当班机对外写数据时,只有当班机对应的数据缓冲器使能,且方向正确(a端口

→

b端口),非当班机b端口为高阻状态;

[0058]

4)当数据缓冲的数据类型为单向时,对数据缓冲无方向性要求;

[0059]

5)当数据缓冲的数据类型为单向时,当班机的控制信号host_cpu_out、ctl_en参与了控制数据缓冲器的使能信号,以保证当班机对外写数据时,只有当班机对应的数据缓冲器使能,且方向正确(a端口

→

b端口),非当班机b端口为高阻状态;

[0060]

6)当cpu系统和系统外设之间的电平不匹配时,数据缓冲器两侧应具有电压转换的功能;

[0061]

设计数据缓冲器时,需要通过host_cpu_out,phy_wr和phy_cs*信号生成ctl_en信号,表2为数据缓冲器的控制真值表:

[0062]

表2

[0063]

host_cpu_outphy_wrphy_cs*ctl_en00000011010001111001101111001111

[0064]

上述信号中,host_cpu_out=0代表当班机,host_cpu_out=1代表非当班机;phy_wr=0代表对外写数据,phy_wr=1代表读外部数据;phy_cs*=0表示使能外设,phy_cs*=1表示外设不使能;phy_dir信号同phy_wr,即当phy_wr=0时,phy_dir控制数据方向为a端口

←

b端口;当phy_wr=1时,phy_dir控制数据方向为a端口

→

b端口,表3为信号host_cpu_out、ctl_en和phy_dir信号真值表:

[0065]

表3

[0066][0067]

三模冗余控制系统中,a系统作为当班机,b系统和c系统作为非当班机,表4为各个单机定义的信号点:

[0068]

表4

[0069][0070][0071]

当a系统输出信号a_host_cpu_out信号为0时,表示a系统为当班机,系统b和c的*_host_cpu_out为1,表示b系统和c系统为非当班机。

[0072]

三模冗余控制系统对外写数据时(a端口

→

b端口),表5为对外写数据控制信号:

[0073]

表5

[0074][0075]

三模冗余控制系统同时读外部数据时(b端口

→

a端口),表6为读外部数据控制信号:

[0076]

表6

[0077][0078]

本技术实施例通过采用上述方式,在系统中取消单点设备,三个计算机子系统与一个或多个系统外设具有等价的连接关系,且三个计算机子系统保持同步,方便三个计算机子系统随时切换,以保持系统对外部关联设备的控制,避免了现有系统中的单点设备发生异常导致系统无法工作的问题,满足系统连续不间断工作的要求。

[0079]

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1