NandFlash脱机裸片烧程设备的制作方法

nand flash脱机裸片烧程设备

技术领域

1.本技术涉及芯片烧录技术领域,特别是涉及一种nand flash脱机裸片烧程设备。

背景技术:

2.电力集中计量采集终端方案逐步采用arm9内核,该方案运行速率快,功能强,需要程序存储空间大,因此需要容量大、稳定性强、读写快等特点的存储芯片,nand flash就成为主流搭配存储芯片。

3.传统的nand flash烧录方法一般是使用带机烧程设备进行带机烧录。首先usb烧写boot loader和内核,初始化各个通讯口和建立文件系统,进一步在整机上电烧写应用程序,应用程序烧写完成后系统启动。

4.然而,传统的带机烧程设备,在投入烧录过程中,需要工人至少两名,一人操作电脑,一人负责轮换待烧程产品。该种方法需要员工之间操作熟练、配合默契,且占用生产设备多(例如电脑、周转车、场地等),需要整机流转烧程,生产效率低且成本高。

技术实现要素:

5.基于此,有必要针对传统nand flash烧程设备由于是带机烧录,导致生产效率低且成本高的问题,提供一种nand flash脱机裸片烧程设备。

6.本技术提供一种nand flash脱机裸片烧程设备,所述nand flash脱机裸片烧程设备包括:

7.pcb板;

8.电源供给装置,设置于pcb板上;

9.多个烧录单元,并列的设置于pcb板上,且每一个烧录单元均与电源供给装置电连接;

10.烧录单元包括:

11.主芯片,焊接于pcb板上;

12.nand flash烧写座,焊接于pcb板上,且与主芯片连接;

13.拨码开关,焊接于pcb板上,与主芯片连接;

14.nor flash存储器,焊接于pcb板上,与主芯片连接;nor flash存储器包括第一存储器、第二存储器和第三存储器。

15.进一步地,所述电源供给装置包括:

16.电源输出装置,用于输出12v直流电压;

17.电源电路,一端与电源输出装置连接,另一端与多个烧录单元连接。

18.电源电路包括电压转换器,用于将电压输出装置输出的12v直流电压转换为低于12v的直流电压输出至多个烧录单元。

19.进一步地,所述电压转换器包括:

20.dc/dc变换器,与电源输出装置连接,用于将电源输出装置输出的12v直流电压转

换为5v直流电压;

21.至少一个ldo稳压器,与dc/dc变换器电连接,用于将dc/dc变换器输出的5v直流电压转换为3.3v直流电压、1.8v直流电压和1.2v直流电压中的一种或多种输出至多个烧录单元。

22.进一步地,所述电源供给装置还包括:

23.电源开关装置,电连接于电源输出装置和电源电路之间。

24.进一步地,所述烧录单元还包括:

25.指示灯,设置于pcb板上,与主芯片连接。

26.进一步地,所述主芯片包括:

27.指示灯io口,指示灯通过指示灯io口与主芯片连接;

28.spi接口,第一存储器、第二存储器和第三存储器均通过spi接口与主芯片连接;

29.拨码开关io口,拨码开关通过拨码开关io口和主芯片连接。

30.进一步地,指示灯包括电源指示灯、内核指示灯和应用程序指示灯。

31.进一步地,指示灯io口包括:

32.电源指示灯io口,电源指示灯通过电源指示灯io口与主芯片连接;

33.内核指示灯io口,内核指示灯通过内核指示灯io口与主芯片连接;

34.应用程序指示灯io口,应用程序指示灯通过应用程序指示灯io口与主芯片连接。

35.进一步地,所述烧录单元还包括:

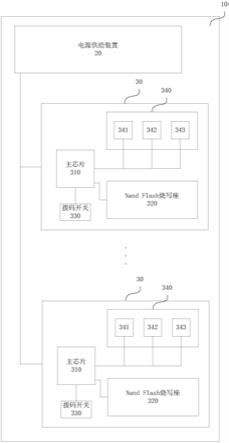

36.第一带机烧录口,用于烧录应用程序;

37.第二带机烧录口,用于烧录boot程序和内核程序。

38.进一步地,主芯片和nand flash烧写座之间通过nand flash总线连接。

39.本技术涉及一种nand flash脱机裸片烧程设备,本技术提供的nand flash脱机裸片烧程设备可以实现脱机下的nand flash裸片烧录,大大提高了生产效率,节省了人工成本,减少占用生产资源。该nand flash脱机裸片烧程设备便携,不占用特定工位,便于维护,自主开发,降低公司易耗品采购成本。

附图说明

40.图1为本技术一实施例提供的nand flash脱机裸片烧程设备的结构示意图;

41.图2为本技术一实施例提供的nand flash脱机裸片烧程设备中,电源供给装置和多个烧录单元的连接关系示意图;

42.图3为本技术一实施例提供的nand flash脱机裸片烧程设备中,电源供给装置和多个烧录单元的连接关系示意图;

43.图4为本技术一实施例提供的nand flash脱机裸片烧程设备中,电源供给装置和多个烧录单元的连接关系示意图;

44.图5为本技术一实施例提供的nand flash脱机裸片烧程设备中,烧录单元的结构示意图;

45.图6为本技术一实施例提供的nand flash脱机裸片烧程设备中,烧录单元的结构示意图。

46.附图标记:

47.10

‑

pcb板;20

‑

电源供给装置;210

‑

电源输出装置;220

‑

电源电路;

48.221

‑

电压转换器;221a

‑

dc/dc变换器;221b

‑

ldo稳压器;

49.230

‑

电源开关装置;30

‑

烧录单元;310

‑

主芯片;311

‑

指示灯io口;

50.311a

‑

电源指示灯io口;311b

‑

内核指示灯io口;

51.311c

‑

应用程序指示灯io口;312

‑

spi接口;313

‑

拨码开关io口;

52.320

‑

nand flash烧写座;330

‑

拨码开关;340

‑

nor flash存储器;

53.341

‑

第一存储器;342

‑

第二存储器;343

‑

第三存储器;350

‑

指示灯;

54.351

‑

电源指示灯;352

‑

内核指示灯;353

‑

应用程序指示灯;

55.361

‑

第一带机烧录口;362

‑

第二带机烧录口;370

‑

nand flash总线;

56.380

‑

spi总线;391

‑

第一usb总线;392

‑

第二usb总线

具体实施方式

57.为了使本技术的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

58.本技术提供一种nand flash脱机裸片烧程设备。需要说明的是,本技术提供的nand flash脱机裸片烧程设备不但可以应用于nand flash芯片,还可以应用于其他任意种类的具有容量大、稳定性强、读写快特点的存储芯片的脱机烧录烧程中。

59.如图1所示,在本技术的一实施例中,所述nand flash脱机裸片烧程设备包括pcb板10、电源供给装置20和多个烧录单元30。所述电源供给装置20设置于pcb板10上,多个烧录单元30并列的设置于pcb板10上。每一个烧录单元30均与电源供给装置20电连接。

60.每一个烧录单元30包括主芯片310、nand flash烧写座320、拨码开关330和nor flash存储器340。所述主芯片310焊接于pcb板10上。所述nand flash烧写座320,焊接于pcb板10上,且与主芯片310连接。所述拨码开关330焊接于pcb板10上,且与主芯片310连接。所述nor flash存储器340,焊接于pcb板10上,且与主芯片310连接。nor flash存储器340包括第一存储器341、第二存储器342和第三存储器343。

61.具体地,本技术涉及的所有设备和元件都可以通过焊接的方式布设在一块pcb板10上。主芯片310的型号可以为nuc975dk61y。nand flash烧写座320为用于安装固定nand flash裸片的夹具。将nand flash裸片装配于nand flash烧写座320之后,等效于将nand flash裸片直接贴装于pcb板10上。

62.nor flash存储器340的型号可以为mx25l51245g。nor flash存储器340可以包括第一存储器341、第二存储器342和第三存储器343。可选地,第一存储器341、第二存储器342和第三存储器343的型号相同,可以都为mx25l51245g,且存储容量相同,均为64mb。

63.具体地,第一存储器341可以存储烧程工装专用程序,烧程工装专用程序用于控制整个脱机烧录过程。第二存储器342和第三存储器343可以存储boot程序,内核程序和应用程序。在脱机烧录时,主芯片可以运行第一存储器341中的烧录工装专用程序,再将第二存储器342和第三存储器343中存储的boot程序,内核程序和应用程序移植至nand flash裸片中,以完成烧程。

64.本实施例提供的nand flash脱机裸片烧程设备可以实现脱机下的nand flash裸

片烧录,大大提高了生产效率,节省了人工成本,减少占用生产资源。该nand flash脱机裸片烧程设备便携,不占用特定工位,便于维护,自主开发,降低公司易耗品采购成本。

65.此外,烧录单元30可以为多个,优选的为4个,可以满足同时烧录4个nand flash裸片的工作量,大大提高了生产效率。

66.如图2所示,在本技术的一实施例中,所述电源供给装置20包括电源输出装置210和电源电路220。所述电源输出装置210用于输出12v直流电压。所述电源电路220的一端与电源输出装置210连接,另一端与多个烧录单元30连接。

67.所述电源电路220包括电压转换器221。所述电压转换器221用于将电压输出装置输出的12v直流电压转换为低于12v的直流电压输出至多个烧录单元30。

68.具体地,电压转换器221可以将电源装置提供的12v电压转换为5v、3.3v、1.8v、1.2v等给电源电路220中的各个功能电路供电,当然主要是为了给每一个烧录单元30供电。电源电路220还包括多个功能电路,布设在pcb板10上,包括各种用于实现供电功能的导线和元器件。

69.如图3所示,在本技术的一实施例中,所述电压转换器221包括一个dc/dc变换器221a和至少一个ldo稳压器221b。所述dc/dc变换器221a与电源输出装置210连接。所述dc/dc变换器221a用于将电源输出装置210输出的12v直流电压转换为5v直流电压。所述ldo稳压器221b与dc/dc变换器221a电连接。所述ldo稳压器221b用于将dc/dc变换器221a输出的5v直流电压转换为3.3v直流电压、1.8v直流电压和1.2v直流电压中的一种或多种输出至多个烧录单元30。

70.具体地,所述dc/dc变换器221a用于将电源输出装置210输出的12v直流电压转换为5v直流电压。5v直流电压可以为后文中提及的第一带机烧录口361和第二带机烧录口362供电。

71.所述ldo稳压器221b用于将dc/dc变换器221a输出的5v直流电压转换为3.3v直流电压、1.8v直流电压和1.2v直流电压中的一种。

72.所述ldo稳压器221b的数量可以为3个,每一个所述ldo稳压器221b转换一个电压值的直流电压,这样就可以将12v直流电压转化为3.3v直流电压、1.8v直流电压和1.2v直流电压三种不同的直流电压。

73.主芯片310中的元器件复杂,对直流电压的大小有特殊要求,同时需要3.3v直流电压、1.8v直流电压和1.2v直流电压三种不同大小的直流电压的输入。3.3v直流电压还可以满足nand flash烧写座320、第一存储器341、第二存储器342和第三存储器343的电压需求。

74.如图4所示,在本技术的一实施例中,所述电源供给装置20还包括电源开关装置230。所述电源开关装置230电连接于电源输出装置210和电源电路220之间。

75.具体地,所述电源开关装置230可以为船型开关。

76.在本技术的一实施例中,所述烧录单元30还包括指示灯350。所述指示灯350设置于pcb板10上。所述指示灯350与主芯片310连接。

77.如图5所示,在本技术的一实施例中,所述主芯片310包括指示灯io口311、spi接口312和拨码开关io口313。指示灯350通过指示灯io口311与主芯片310连接。第一存储器341、第二存储器342和第三存储器343均通过spi接口312与主芯片310连接。拨码开关330通过拨码开关io口313和主芯片310连接。

78.具体地,拨码开关330可以有多个,每一个拨码开关330通过一个拨码开关io口313与主芯片310连接。拨码开关330可以调整自己的电平,有“0”和“1”两种高低不同的电平,以向主芯片310发送不同的电压信号,从而使得主芯片310后续启动不同的烧录模式。不同的烧录模式代表烧录进入不同的进程步骤。例如,拨码开关330有2个的话,电平组合就有“00”,“01”,“11”,“10”四种不同的组合方式,就可以向主芯片310发送四种不同的电压信号。

79.第一存储器341、第二存储器342和第三存储器343共用一个主芯片310上的spi接口312。第一存储器341、第二存储器342和第三存储器343中,每个存储器上均有一个片选信号(cs0、cs1和cs2)与主芯片310相连接(低电平选中),主芯片310想与哪个存储器交互数据,就输出相应片选信号为低电平。第一存储器341、第二存储器342和第三存储器343是通过一根spi总线380与主芯片310连接的。spi总线380与spi接口312连接。spi总线380上同一时间只能有一个存储器与主芯片310交互数据。具体主芯片310与与哪个存储器交互数据,就是通过主芯片310输出的片选信号控制的。

80.如图6所示,在本技术的一实施例中,指示灯350包括电源指示灯351、内核指示灯352和应用程序指示灯353。

81.具体地,电源指示灯351、内核指示灯352和应用程序指示灯353分别实现不同的提示功能。当电源指示灯351亮时,表明整块pcb板10已上电,即每一个烧录单元30均已上电,可以开始工作。当内核指示灯352亮时,表明内核程序已烧录完毕。当应用程序指示灯353亮时,表明应用程序已烧录完毕。

82.如图6所示,在本技术的一实施例中,指示灯io口311包括电源指示灯io口311a、内核指示灯io口311b和应用程序指示灯io口311c。电源指示灯351通过电源指示灯io口311a与主芯片310连接。内核指示灯352通过内核指示灯io口311b与主芯片310连接。应用程序指示灯353通过应用程序指示灯io口311c与主芯片310连接。

83.如图6所示,在本技术的一实施例中,所述烧录单元30还包括第一带机烧录口361和第二带机烧录口362。所述第一带机烧录口361用于烧录应用程序。所述第二带机烧录口362用于烧录boot程序和内核程序。

84.具体地,本技术提供的nand flash脱机裸片烧程设备,不但可以脱机烧录,而且可以带机烧录。第一带机烧录口361和第二带机烧录口362是在带机烧录模式下采用的。带机烧程时,第一带机烧录口361用于裸片烧写应用程序。带机烧程时,第二带机烧录口362用于裸片烧录boot程序和内核程序。

85.本实施例中,通过设置第一带机烧录口361和第二带机烧录口362,使得nand flash脱机裸片烧程设备既可以满足脱机烧录的要求,又可以满足带机烧录的要求。

86.如图6所示,在本技术的一实施例中,主芯片310和nand flash烧写座320之间通过一条nand flash总线370连接。

87.具体地,第一存储器341、第二存储器342和第三存储器343均通过一条spi总线380与主芯片310连接,如图6所示。

88.第一带机烧录口361通过第一usb总线391与主芯片310连接。第二带机烧录口362通过第二usb总线392与主芯片310连接。

89.以上所述实施例的各技术特征可以进行任意的组合,各方法步骤也并不做执行顺

序的限制,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

90.以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本技术专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术的保护范围应以所附权利要求为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1