中央处理器、处理器模块以及电子设备的制作方法

1.本公开属于电子技术领域,特别涉及一种中央处理器、处理器模块以及电子设备。

背景技术:

2.中央处理器是电子计算机的运算和控制核心,为电子计算机的重要组成部分。

3.在相关技术中,中央处理器的整体功耗,为计算单元和接口单元等功能单元的总和。为了保证中央处理器的正常工作,通常会将中央处理器的整体功耗限制在散热设计功耗(thermal design power,tdp)以内。

4.然而,由于中央处理器在设计时,就会给各接口单元预留需要的功耗,所以即使是接口单元闲置,这部分的功耗也无法分配给计算单元使用,导致计算单元所分配到的功耗较低,计算单元只能以较低的频率和工作核心数运行,无法进一步提升运算能力。

技术实现要素:

5.本公开实施例提供了一种中央处理器、处理器模块以及电子设备,能够保证中央处理器的运算能力。所述技术方案如下:

6.第一方面,本公开实施例提供了一种中央处理器,所述中央处理器包括控制单元、开关单元和n个接口单元,n≥2,且n为整数;

7.n个所述接口单元均通过所述开关单元与所述控制单元相连;

8.所述控制单元和所述开关单元被配置为,通过所述控制单元控制所述开关单元,使得m个所述接口单元得电,m≤n,且m为正整数。

9.在本公开的一种实现方式中,所述开关单元包括n个开关子单元;

10.第a个所述开关子单元分别与所述控制单元和第a个所述接口单元相连,a≤n,且a为正整数。

11.在本公开的一种实现方式中,所述开关子单元包括电源输入端、信号输入端和电源输出端;

12.所述电源输入端与所述中央处理器的供电端相连;

13.所述信号输入端与所述控制单元的信号输出端相连;

14.所述电源输出端与所述接口单元的电源输入端相连。

15.在本公开的一种实现方式中,所述开关子单元为逻辑门电路。

16.在本公开的一种实现方式中,所述开关子单元为一次性可编程存储器。

17.在本公开的一种实现方式中,所述接口单元为内存接口单元、超速通道互联upi接口单元和高速串行计算机扩展总线pcie接口单元中的至少一种。

18.在本公开的一种实现方式中,所述控制单元具有至少两种控制规格;

19.每一种所述控制规格所对应的所述接口单元的总功耗不相同。

20.在本公开的一种实现方式中,所述控制单元具有第一种控制规格、第二种控制规格和第三种控制规格;

21.所述第一种控制规格所对应的所述接口单元的总功耗,小于所述第二种控制规格所对应的所述接口单元的总功耗;

22.所述第二种控制规格所对应的所述接口单元的总功耗,小于所述第三种控制规格所对应的所述接口单元的总功耗。

23.在本公开的一种实现方式中,当所述控制单元为所述第一种控制规格时,3个所述内存接口单元得电,4个所述pcie接口单元得电,3个所述upi接口单元得电。

24.在本公开的一种实现方式中,当所述控制单元为所述第二种控制规格时,3个所述内存接口单元得电,1个所述pcie接口单元得电,3个所述upi接口单元得电。

25.在本公开的一种实现方式中,当所述控制单元为所述第三种控制规格时,2个所述内存接口单元得电,1个所述pcie接口单元得电,3个所述upi接口单元得电。

26.第二方面,本公开实施例提供了一种处理器模块,所述处理器模块包括主板和第一方面所述的中央处理器;

27.所述主板具有处理器插座、内存接口、超速通道互联upi接口、高速串行计算机扩展总线pcie接口和电源接口,所述内存接口、所述upi接口、所述pcie接口和所述电源接口均与所述处理器插座相连;

28.所述中央处理器插接在所述处理器插座内。

29.第三方面,本公开实施例提供了一种电子设备,所述电子设备包括内存条、网卡、电源和第二方面所述的处理器模块;

30.所述内存条插接在所述内存接口内;

31.所述网卡插接在所述pcie接口内;

32.所述电源与所述电源接口相连。

33.本公开实施例提供的技术方案带来的有益效果至少包括:

34.中央处理器在工作时,根据接口单元的使用情况,控制不同数量的接口单元得电。当需要使用m个接口单元时,通过所述控制单元控制所述开关单元,使得m个所述接口单元得电,即保证了m个接口单元能够正常工作。相应的,此时有n-m个接口单元失电,即不消耗中央处理器的整体功耗。

35.也就是说,本公开实施例提供的中央处理器,能够根据需求,调整得电的接口单元数量,使得需要使用的接口单元得电,而闲置的接口单元则失电,避免了闲置的接口单元浪费中央处理器的整体功耗,使得中央处理器的计算单元能够分配到更多的功耗,从而保证了计算单元的频率和工作核心数,进而保证了计算单元的运算能力。

附图说明

36.为了更清楚地说明本公开实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本公开的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

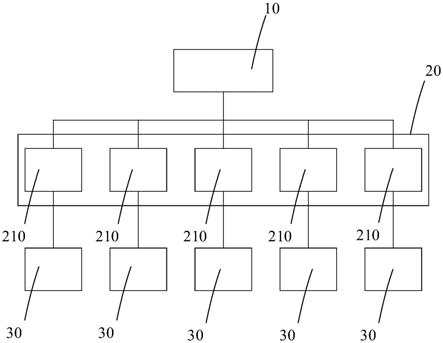

37.图1是本公开实施例提供的中央处理器的结构示意图;

38.图2是本公开实施例提供的开关子单元的结构示意图;

39.图3是本公开实施例提供的处理器模块的结构示意图;

40.图4是本公开实施例提供的电子设备的结构示意图。

41.图中各符号表示含义如下:

42.10、控制单元;

43.20、开关单元;

44.210、开关子单元;211、电源输入端;212、信号输入端;213、电源输出端;

45.30、接口单元;

46.40、供电端;

47.100、主板;

48.1010、处理器插座;1020、内存接口;1030、upi接口;1040、pcie接口;1050、电源接口;

49.200、中央处理器;

50.1000、内存条;2000、网卡;3000、电源;4000、处理器模块。

具体实施方式

51.为使本公开的目的、技术方案和优点更加清楚,下面将结合附图对本公开实施方式作进一步地详细描述。

52.中央处理器是电子计算机的运算和控制核心,为电子计算机的重要组成部分。

53.在相关技术中,中央处理器的整体功耗,为计算单元和接口单元等功能单元的总和。为了保证中央处理器的正常工作,通常会将中央处理器的整体功耗限制在散热设计功耗以内。

54.然而,闲置状态下的接口单元会浪费中央处理器的整体功耗,导致计算单元所分配到的功耗较低,影响计算单元的运算能力。

55.为了解决上述技术问题,本公开实施例提供了一种中央处理器,图1为中央处理器的结构示意图,结合图1,在本实施例中,该中央处理器包括控制单元10、开关单元20和n个接口单元30,n≥2,且n为整数。n个接口单元30均通过开关单元20与控制单元10相连。

56.控制单元10和开关单元20被配置为,通过控制单元10控制开关单元20,使得m个接口单元30得电,m≤n,且m为正整数。

57.中央处理器在工作时,根据接口单元30的使用情况,控制不同数量的接口单元30得电。当需要使用m个接口单元30时,通过控制单元10控制开关单元20,使得m个接口单元30得电,即保证了m个接口单元30能够正常工作。相应的,此时有n-m个接口单元30失电,即不消耗中央处理器的整体功耗。

58.也就是说,本公开实施例提供的中央处理器,能够根据需求,调整得电的接口单元30数量,使得需要使用的接口单元30得电,而闲置的接口单元30则失电,避免了闲置的接口单元30浪费中央处理器的整体功耗,使得中央处理器的计算单元能够分配到更多的功耗。在计算单元分配到更多的功耗后,就能够使得计算单元具有足够的功耗配额来提升自身的频率,或者是增加工作核心数,从而保证了计算单元的运算能力。

59.需要说明的是,计算单元的频率和工作核心数,既能够一同调整,也能够择一调整,本公开对此不作限制。

60.容易理解的是,当m=n时,相当于所有的接口单元30均需要使用,无闲置的接口单

元30。在此情况下,开关单元20控制所有的接口单元30均得电。也就是说,即使是在所有的接口单元30均需要使用的情况下,也能够保证所有的接口单元30正常使用。

61.在本实施例中,中央处理器为x86指令集处理器、arm指令集处理器、无内部互锁流水级的微处理器(microprocessor without interlocked pipelined stages,mips)中的任一种。

62.由前文可知,控制单元10和开关电路为控制接口单元30得电或者失电的关键,下面对控制单元10和开关电路进行介绍。

63.继续参见图1,在本实施例中,开关单元20包括n个开关子单元210,第a个开关子单元210分别与控制单元10和第a个接口单元30相连,a≤n,且a为正整数。

64.开关子单元210的数量和接口单元30的数量相同,且开关子单元210与接口单元30一一对应,各接口单元30通过各自对应的开关子单元210与控制单元10相连。如此设计,能够通过各开关子单元210对各自对应的接口单元30的得电或者失电进行控制,提高了开关单元20的控制精准度。

65.图2为开关子单元210的结构示意图,结合图2,在本实施例中,开关子单元210包括电源输入端211、信号输入端212和电源输出端213。电源输入端211与中央处理器的供电端40相连,信号输入端212与控制单元10的信号输出端相连,电源输出端213与接口单元30的电源输入端相连。

66.在上述实现方式中,电源输入端211用于接收中央处理器的供电端40传输来的电流,在开关子单元210导通的情况下,能够将电流通过电源输出端213传输至接口单元30,使得接口单元30得电。信号输入端212用于接收使能信号,通过该使能信号控制开关子单元210导通或者关闭。

67.可选的,开关子单元210为逻辑门电路,或者一次性可编程存储器。逻辑门电路和一次性可编程存储器所达到的效果基本相同,当开关子电路的电源输入端211通电,信号输入端212接收到高电平使能信号时,开关子单元210导通,使得接口单元30得电。

68.在本实施例中,控制单元10为gpio(general purpose input and output,通用输入输出)控制单元10,其包括gpio引脚和寄存器,gpio引脚与开关子单元210的信号输入端212相连,寄存器中写有控制程序。控制单元10对于开关单元20的控制方式有两种,下面分别进行介绍。

69.第一种控制方式,在控制单元10内记录有多种规格,不同规格对应不同的得电的接口单元30数量,以及相应的计算单元的频率和工作核心数。在中央处理器第一次启动时,采用默认的模式运行。操作者通过命令行或者工具调整规格,从而调整相应的得电的接口单元30数量,以及相应的计算单元的频率和工作核心数。

70.第二种控制方式,在控制单元10内记录有多种规格,不同规格对应不同的得电的接口单元30数量,以及相应的计算单元的频率和工作核心数。在中央处理器启动时,自动识别外围设备(与接口单元30对应的设备)的连接情况,将识别到的连接情况与记录的规格进行对比匹配,选择并应用最为合适的规格。举例来说,控制单元10内记录有三种规格,分别为三个接口单元30得电,四个接口单元30得电,五个接口单元30得电。若识别到连接有三个外围设备,则在三种规格中,选择应用三个接口单元30得电的规格。

71.也就是说,在本实施例中,上述控制方式为弹性调整方式,方式可以是命令行、

bios(basic input output system,基本输入输出系统)选项、手动设置相关寄存器等。

72.在本实施例中,接口单元30为内存接口单元、超速通道互联upi(ultra path interconnect)接口单元、高速串行计算机扩展总线pcie(peripheral component interconnect express)接口单元中的至少一种。

73.在上述实现方式中,内存接口用于连接内存条,upi接口单元用于连接其他的中央处理器,pcie接口单元用于连接具有pcie接口的设备,例如网卡等。

74.示例性的,pcie接口单元为pcie x16接口单元。

75.在其他实施例中,接口单元30还可以是直接媒体dmi(direct media interface)接口,dmi接口用于连接南北桥。

76.可选的,当接口单元30为pcie接口单元时,利用pcie协议规定,能够将pcie接口单元调整为l1.2节能模式,处于该节能模式下的pcie接口单元的功耗极低。如此一来,能够通过将闲置的pcie接口单元调整为l1.2节能模式,以此降低能耗,使得中央处理器的计算单元能够分配到更多的功耗,从而保证了计算单元的频率和工作核心数,进而保证了计算单元的运算能力。并且,当接口单元30为内存接口单元和upi接口单元时,同样能够通过类似的节能功能,来使得中央处理器的计算单元能够分配到更多的功耗,从而保证了计算单元的频率和工作核心数,进而保证了计算单元的运算能力。另外,针对upi接口单元来说,其还支持降带宽、降速等容错机制。

77.在本实施例中,控制单元10具有至少两种控制规格,每一种控制规格所对应的接口单元30的总功耗不相同。

78.在上述实现方式中,通过使控制单元10处于不同的控制规格,能够调整接口单元30的总功耗。由于中央处理器的整体功耗一定,所以通过调整接口单元30的总功耗,即能够调整计算单元所能够分配到的功耗,从而调整计算单元的频率和工作核心数。

79.可选的,控制单元具有第一种控制规格、第二种控制规格和第三种控制规格。第一种控制规格所对应的接口单元的总功耗,小于第二种控制规格所对应的接口单元的总功耗,第二种控制规格所对应的接口单元的总功耗,小于第三种控制规格所对应的接口单元的总功耗。

80.也就是说,第一种控制规格、第二种控制规格、第三种控制规格下的接口单元的总功耗依次增大。如此一来,能够便于控制逻辑的设计,保证了中央处理器的可靠性。

81.表一为中央处理器的整体功耗计算表,参见表一。

82.a规格即为第一种控制规格,b规格即为第二种控制规格,c规格即为第三种控制规格。三种规格中,计算单元的工作核心数均为28个,而频率则分别为3.0ghz、3.1ghz和3.2ghz。也就是说,这三种规格采取了工作核心数保持不表,调整频率的方式。

83.当控制单元为第一种控制规格时,3个内存接口单元得电,4个pcie接口单元得电,3个upi接口单元得电。在第一种控制规格下,3个内存接口单元的总功耗为15w,4个pcie接口单元的总功耗为16w,3个upi接口单元的总功耗为12w,即第一种控制规格所对应的接口单元的总功耗为43w。另外,缓存单元的数量为28个,总功耗为28w,其他单元(dmi接口单元)的数量为1个,总功耗为12w。因此,剩余给计算单元的功耗为270w-83w=187w。由于计算单元的工作核心为28个,所以单个工作核心所需的功耗不得超过6.678w,因此选择频率为3.0ghz的计算单元。

84.当控制单元为第二种控制规格时,3个内存接口单元得电,1个pcie接口单元得电,3个upi接口单元得电。相较于第一种控制规格来说,第二种控制规格仅有1个pcie接口单元得电,如此一来,节省的功耗就能够分配给计算单元,从而选择频率为3.1ghz的计算单元。

85.当控制单元为第三种控制规格时,2个内存接口单元得电,1个pcie接口单元得电,3个upi接口单元得电。相较于第一种控制规格来说,第三种控制规格仅有2个内存单元得电,1个pcie接口单元得电,如此一来,就能够进一步的节省功耗并分配给计算单元,从而选择频率为3.2ghz的计算单元。

86.表一

[0087][0088]

表二为中央处理器的整体功耗计算表,参见表二。

[0089]

在表二中,控制单元10内记录有a、b两种规格。两种规格中,计算单元的频率和工作核心数均不相同。也就是说,这两种规格采取了同时调整频率和工作核心数的方式。

[0090]

表二

[0091][0092]

下面以规格a为例进行说明,在规格a中,缓存单元的数量为26个,总功耗为26w,内存接口单元的数量为3个,总功耗为15w,pcie接口单元的数量为4个,总功耗为16w,upi接口单元的数量为3个,总功耗为12w,其他单元的数量为1个,总功耗为12w。因此,剩余给计算单元的功耗为270w-83w=187w。综合频率和工作核心数,选择频率为3.1ghz,工作核心为26个的计算单元。

[0093]

而对于规格b来说,其需要使用的pcie接口单元仅为1个,upi接口单元仅为2个,所以仅需要将1个pcie接口单元得电,2个upi接口单元得电,如此一来,就能够节省功耗并分配给计算单元,从而选择频率为3.2ghz,工作核心为28个的计算单元。

[0094]

图3为本公开实施例提供的一种处理器模块的结构示意图,结合图3,在本实施例中,该处理器模块包括主板100和图1和2所示的中央处理器200。主板100具有处理器插座1010、内存接口1020、超速通道互联upi接口1030、高速串行计算机扩展总线pcie接口1040和电源接口1050,内存接口1020、upi接口1030、pcie接口1040和电源接口1050均与处理器插座1010相连。中央处理器200插接在处理器插座1010内。

[0095]

内存接口1020用于插接内存条,upi接口1030用于连接其他的中央处理器200,pcie接口1040用于连接网卡,电源接口1050用于连接电源。在中央处理器200插接到处理器插座1010后,内存接口单元与内存接口1020相连,upi接口单元与upi接口1030相连,pcie接口单元与pcie接口1040相连,供电端与电源接口1050相连。也就是说,通过主板100,实现了对于中央处理器200的承载安装,并实现了中央处理器200的各接口单元与各外部设备之间的连接。

[0096]

在处理器模块工作时,处理器模块内的中央处理器工作。中央处理器根据接口单元的使用情况,控制不同数量的接口单元得电。当需要使用m个接口单元时,通过控制单元

控制开关单元,使得m个接口单元得电,即保证了m个接口单元能够正常工作。相应的,此时有n-m个接口单元失电,即不消耗中央处理器的整体功耗。

[0097]

也就是说,本公开实施例提供的中央处理器,能够根据需求,调整得电的接口单元数量,使得需要使用的接口单元得电,而闲置的接口单元则失电,避免了闲置的接口单元浪费中央处理器的整体功耗,使得中央处理器的计算单元能够分配到更多的功耗,从而保证了计算单元的频率和工作核心数,进而保证了计算单元的运算能力。

[0098]

图4为本公开实施例提供的一种电子设备的结构示意图,结合图4,在本实施例中,该电子设备包括内存条1000、网卡2000、电源3000和图4的处理器模块4000。内存条1000插接在内存接口1020内,网卡2000插接在pcie接口1040内,电源3000与电源接口1050相连。

[0099]

在电子设备工作时,处理器模块内的中央处理器工作。中央处理器根据接口单元的使用情况,控制不同数量的接口单元得电。当需要使用m个接口单元时,通过控制单元控制开关单元,使得m个接口单元得电,即保证了m个接口单元能够正常工作。相应的,此时有n-m个接口单元失电,即不消耗中央处理器的整体功耗。

[0100]

也就是说,本公开实施例提供的中央处理器,能够根据需求,调整得电的接口单元数量,使得需要使用的接口单元得电,而闲置的接口单元则失电,避免了闲置的接口单元浪费中央处理器的整体功耗,使得中央处理器的计算单元能够分配到更多的功耗,从而保证了计算单元的频率和工作核心数,进而保证了计算单元的运算能力。

[0101]

在本实施例中,电子设备为手机、电脑、工作站和服务器中的任一种。

[0102]

以上所述仅为本公开的可选实施例,并不用以限制本公开,凡在本公开的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1