从装置、主装置的制作方法

本公开涉及具备闪速存储器等作为后端模块的从装置、以及用于控制所述从装置的主装置。

背景技术:

1、近年来,作为后端模块而具备闪速存储器等大容量的非易失性存储元件,能够进行高速的数据访问(读以及写)处理的sd卡、存储棒这种从装置在市面中普及。这样的从装置通过规定的接口(以后简记为i/f)而与个人计算机、智能手机、数码相机、音频播放器以及汽车导航仪系统等的主装置连接,被用作为外部记录介质。

2、此外,作为后端模块,也存在安装有可与外部无线通信的无线通信模块的从装置,通过与主装置连接,也能够对主装置附加该无线通信功能。

3、上述从装置在主装置的电源为接通的状态时,能够从主装置接受电源的供给,向以后端模块为代表的部件分配所述电源并进行数据访问。

4、在现有的从装置中,主装置的电源为接通的状态时,一直向后端模块供给电源。因此,即使在没有从主装置经由i/f数据访问的情况下,也向后端模块供给电源,导致电力的浪费。关于这一点,例如在通过小型蓄电池等电源容量较小的电源供给器进行驱动的主装置中,短时间内电源枯竭,难以进行主装置以及从装置的长时间的连续动作。

5、为了解决上述问题,作为用于在不实施数据访问的情况下抑制电力消耗的技术,专利文献1中公开了暂停模式(suspend mode),非专利文献1中公开了掉电模式(powerdown mode)。

6、以下,将非专利文献1中所述的掉电模式作为现有的实施方式,使用图1至图5来进行说明。

7、图1是对非专利文献1所述的由具备现有的掉电模式的从装置以及对所述从装置进行控制的主装置构成的主-从系统进行说明的框图。如图1所示,主装置100至少具备电源供给部101、主装置控制器102。并且,主装置控制器102至少具有主装置i/f部103、cpu104、作为易失性存储元件的ram105。

8、主装置100与从装置120被机械地连接。此外,主装置100经由3.3v电源线即vdd线110,与从装置120电连接。

9、从装置120至少具备:从装置控制器121、后端模块122、对向后端模块122的电源供给的接通(on)和断开(off)进行切换的sw123、在从装置控制器121与后端模块122之间进行数据通信的后端总线124。后端模块122是指闪速存储器这样的记录介质、无线通信模块这样的设备,但这里说明为记录介质。

10、从装置控制器121至少具有从装置i/f部125、寄存器126、cpu127、易失性存储元件即ram128。

11、经由vdd线110向从装置120供给的3.3v电源被供给至从装置控制器121,此外,只要在sw123接通的情况下也向后端模块122供给。

12、主装置i/f部103与从装置i/f部125之间经由clk线111、cmd线112、dat线113而连接,两者之间进行基于单端方式的双向的信号通信。另外,dat线113由4根信号线构成,在时钟信号的1采样期间能够收发4比特的信号。

13、图2是说明为了主装置100对从装置120进行指示而发送的指令的格式的图。

14、指令200至少包含指令索引201以及自变量202。指令索引201通过数值来表现主装置100对从装置120指示的操作的内容。在该现有的实施方式中,使用用于访问从装置控制器121内的寄存器126的通用写指令以及通用读指令,实现向掉电模式的转移以及恢复。

15、自变量202的结构根据指令索引201而变化。在指令索引201表示通用写指令或者通用读指令时,自变量202至少包含寄存器地址203以及访问尺寸204。

16、图3是说明寄存器126内的寄存器映射图的图。图的纵轴表示寄存器地址,横轴表示规定的寄存器地址所指的寄存器空间中包含的各寄存器变量的比特位置。图3中,仅记载与掉电模式有关的寄存器变量,在寄存器地址pd_addr301所示的寄存器空间的第x个比特,定义了能够进行读以及写的r/w型寄存器变量pdmn302,同样地在第y个比特定义了仅能够进行读的ro型寄存器变量pdmr303。

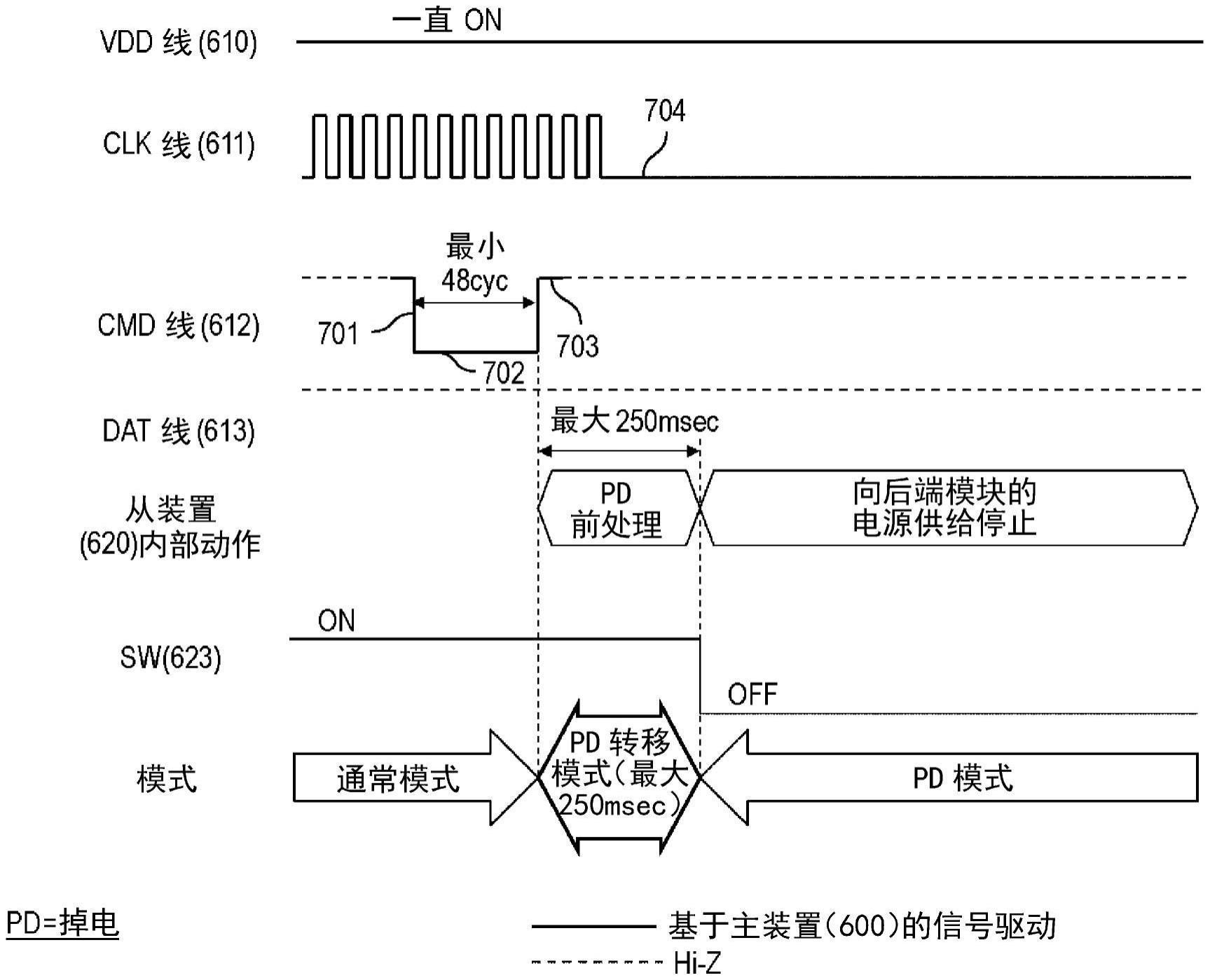

17、图4是由具备现有的掉电模式的从装置以及连接的主装置构成的主-从系统从通常模式向掉电模式转移时的时序图,图5是上述主-从系统从掉电模式恢复为通常模式时的时序图。另外,图4以后的图中,可能将掉电简记为pd。

18、首先,使用图1至图4来说明主-从系统从通常模式向掉电模式转移的情况。

19、在通常模式中,主装置100经由vdd线110,向从装置120供给3.3v电源,经由clk线111供给规定的频率的单端方式的时钟信号。时钟信号的高电平的电压任意,但在非文献资料1中,规定为3.3v或1.8v。另外,低电平是0v。在通常模式中,从装置120将sw123设为接通(on),向后端模块122供给3.3v电源。

20、主装置100为了避免在未装配从装置120的状态下各信号线成为浮动状态,通过未图示的上拉电阻,将cmd线112以及dat线113的全部信号线上拉为与经由clk线111而供给的单端方式的时钟信号的高电平相同的电压。

21、此外,主装置100以及从装置120在双方之间不进行信号通信时,不将cmd线112以及dat线113的各端子驱动为低电平、高电平任一者,而设为输入状态、即高阻抗(hi-z)状态。因此,在从主装置100以及从装置任一者都不进行信号发送时,这些信号线为高电平。

22、在主装置100希望使主-从系统向掉电模式转移时,通过基于主装置控制器102内的ram105中展开的软件程序而驱动的cpu104的指示,主装置i/f部103对从装置i/f部125经由cmd线112发送通用写指令401a。主装置100能够根据在ram105上展开的软件的编程,发送按照图2所述的指令格式的任意的指令。

23、一般在主装置i/f部103对从装置i/f部125发送指令的期间以及其前后的规定的期间,cmd线112被主装置100驱动。

24、通用写指令401a对指令索引201设定用于识别是通用写指令的数值。对寄存器地址203设定包含pdmn302的寄存器地址即pd_addr301,对访问尺寸204设定1以上的值。

25、在从装置i/f部125经由cmd线112接收到通用写指令401a时,从装置i/f部125经由cmd线112向主装置i/f部103发送响应401b,该响应401b是正确地接收到通用写指令401a的意思。一般在从装置i/f部125对主装置i/f部103发送响应的期间以及其前后的规定的期间,cmd线112被从装置120驱动。

26、进一步地,从装置i/f部125针对cpu127,发生通用写指令401a接收的中断。该中断被通知给cpu127,cpu127开始接收到在ram128上展开的软件程序中安装的通用写指令401a时的处理。

27、若主装置i/f部103接收响应401b,则主装置i/f部103经由dat线113向从装置i/f部125发送数据401c。一般在主装置i/f部103对从装置i/f部125发送数据的期间以及其前后的规定的期间,由4根信号线构成的dat线113被主装置100驱动。

28、从装置i/f部125从通用写指令401a的寄存器地址203中指定的寄存器126的寄存器地址pd_addr301,与访问尺寸204中指定的尺寸(字节)相应地,将数据401c的内容写入到寄存器126。这里,设定数据401c上的值,以使得对pdmn302写入“1”。在对pdmn302写入“1”时,主-从系统从通常模式移至掉电转移模式。主装置i/f部103从开始发送通用写指令401a到结束发送数据401c,需要最小1142cyc(时钟循环)期间。

29、若对pdmn302写入“1”,则寄存器126针对cpu127使其发生掉电模式转移指示的中断。此时,cpu127开始为了向不对后端模块122供给电源的掉电模式转移所需的处理即掉电前处理。

30、作为掉电前处理的例子,存在如下处理:为了当前ram128中保持的最新的文件管理表和后端模块122中记录的文件管理表取得匹配,cpu127经由后端总线124,向后端模块122写入ram128上的该数据。若不实施该掉电前处理,则万一在掉电模式中从装置120从主装置100拔出等的现象导致停止对从装置120的3.3v电源的供给时,ram128上保持的最新的文件管理表消失。其结果,下次从装置120启动时,后端模块122中记录的文件管理表与实际的文件数据之间产生不一致,产生不能正确读取后端模块122中记录的文件数据的故障。

31、主装置100通过检测寄存器126的pdmr303,能够确认从装置120是否为掉电模式。为此,主装置i/f部103经由cmd线112对从装置120发送通用读指令402a。

32、通用读指令402a对指令索引201设定用于识别是通用读指令的数值。对寄存器地址203设定包含pdmr303的寄存器地址即pd_addr301,对访问尺寸204设定1以上的值。

33、在从装置i/f部125经由cmd线112接收到通用读指令402a时,从装置i/f部125经由cmd线112向主装置i/f部103发送响应402b,该响应402b是正确地接收到通用读指令402a的意思。

34、响应402b发送后,从装置i/f部125从通用读指令402a的寄存器地址203中指定的寄存器126的寄存器地址pd_addr301,对数据402c设定相当于由访问尺寸204指定的尺寸(字节)的寄存器126的值。此时,从装置120在执行掉电前处理中,寄存器pdmr303的值是“0”。因此,对相当于数据402c内的pdmr303的比特的值设定“0”。

35、并且,从装置i/f部125经由dat线113,向主装置i/f部103发送数据402c。一般在从装置i/f部125对主装置i/f部103发送数据的期间以及其前后的规定的期间,由4根信号线的dat线113被从装置120驱动。

36、接收到数据402c的主装置i/f部103根据pdmr303的值是“0”,检测是掉电转移模式,继续经由clk线111的时钟信号的发送。

37、在从装置120内掉电前处理结束时,寄存器126使pdmr303的值从“0”变化为“1”。

38、然后,主装置i/f部103经由cmd线112对从装置120发送通用读指令403a,从装置i/f部125发送响应403b。通用读指令403a的内容与通用读指令402a同样。

39、在从装置i/f部125接收到通用读指令403a时,掉电前处理结束,pdmr303的值是“1”。因此,从装置i/f部125在对相当于随着通用读指令403a接收而从装置i/f部125发送的数据403c内的pdmr303的比特的值设定“1”后,发送数据403c。并且,cpu127将sw123从接通切换为断开(off),停止向后端模块122的电源供给。另外,若是从装置控制器121内的结构要素,则sw123的切换操作也可以是cpu127以外。

40、接收到数据403c的主装置i/f部103由于pdmr303的值是“1”,检测从掉电转移模式移至掉电模式。然后,主装置i/f部103停止经由clk线111的时钟信号的供给(404)。另外,主装置i/f部103也可以在掉电模式时不停止时钟信号的供给。

41、接着,使用图1至图3以及图5来说明从掉电模式恢复为通常模式的情况。

42、在主装置100使主-从系统从掉电模式恢复为通常模式时,若时钟信号停止,则经由clk线111重新开始时钟信号的发送(500),然后,通过基于主装置控制器102内的ram105中展开的软件程序而驱动的cpu104的指示,主装置i/f部103经由cmd线112对从装置120发送通用写指令501a。

43、通用写指令501a与通用写指令401a同样。

44、在从装置i/f部125经由cmd线112接收到通用写指令501a时,从装置i/f部125经由cmd线112向主装置i/f部103发送响应501b,该响应501b是正确地接收到通用写指令501a的意思。进一步地,从装置i/f部125针对cpu127使其发生通用写指令401a接收的中断。由此,cpu127开始接收到通用写指令501a时的处理。

45、若主装置i/f部103接收响应501b,则主装置i/f部103经由dat线113,将数据501c发送给从装置i/f部125。在此,设定数据501c的值,以使得对pdmn302写入“0”。在对pdmn302写入“1”时,主-从系统从掉电模式移至掉电恢复模式。

46、与图4同样地,从主装置i/f部103开始发送通用写指令501a起到结束发送数据501c为止,需要最小1142cyc期间。

47、寄存器126若对pdmn302写入“0”,则针对cpu127使其发生掉电模式恢复指示的中断。此时,cpu127将sw123从断开切换为接通。由此,再次向后端模块122供给3.3v电源。同时,cpu127开始为了从掉电模式恢复为通常模式所需的处理即掉电后处理。作为掉电后处理的例子,存在伴随着向后端模块122的电源供给重新开始的、基于从装置控制器121的初始设定处理等。

48、主装置100通过检测寄存器126的pdmr303,能够确认从装置120是否恢复为通常模式。为此,主装置i/f部103经由cmd线112对从装置120发送通用读指令502a。通用读指令502a与通用读指令402a同样。

49、在从装置i/f部125经由cmd线112接收到通用读指令502a时,从装置i/f部125经由cmd线112向主装置i/f部103发送响应502b,该响应502b是正确地接收到通用读指令502a的意思。

50、在从装置i/f部125接收到通用读指令502a时,掉电后处理在执行中,pdmr303的值是“1”,因此随着通用读指令502a接收,对相当于从装置i/f部125发送的数据502c内的pdmr303的比特的值设定“1”。并且,从装置i/f部125经由dat线113,将数据502c发送给主装置i/f部103。

51、接收到数据502c的主装置i/f部103根据pdmr303的值是“1”,检测出是掉电恢复模式而不是通常模式。

52、在从装置120内掉电后处理结束时,寄存器126使pdmr303的值从“1”变化为“0”。

53、然后,主装置i/f部103经由cmd线112对从装置120发送通用读指令503a,从装置i/f部125发送响应503b。通用读指令503a的内容与通用读指令502a同样。

54、在从装置i/f部125接收到通用读指令503a时,掉电后处理结束,pdmr303的值是“0”。因此,从装置i/f部125随着通用读指令503a接收,对相当于从装置i/f部125发送的数据503c内的pdmr303的比特的值设定“1”之后,发送数据503c。

55、接收到数据503c的主装置i/f部103根据pdmr303的值是“0”,检测出从掉电恢复模式移至通常模式。由此,主装置100能够对从装置120,发出伴随向后端模块122的数据读写的通常指令504a。从装置i/f部125接收到通常指令504a之后,将对应的响应504b发送给主装置i/f部103。

56、在到此为止说明的现有的实施方式所涉及的主-从系统中,执行从通常模式向掉电模式的转移以及从掉电模式向通常模式的恢复时,存在以下的问题。

57、在主装置对从装置120指示向掉电模式的转移或从掉电模式的恢复时,通过通用写指令(图4的401a,图5的501a)对寄存器变量pdmn写入规定的值来执行。通用写指令除了现有的实施方式中说明的针对掉电模式的转移/恢复以外,也能够应用于包含从装置内部的处理需要时间的各种控制,因此从通用写指令发送到对应的处理的结束的最大时间一律被定义为1sec。由此,主装置能够不根据基于通用写指令的控制的种类地,如果待机最大1sec则判断为从装置内的处理结束,因此具有主装置中的待机时间处理变得简便的优点。

58、另一方面,在使用现有的实施方式中说明的通用写指令的方法中,在从通常模式向掉电模式转移的中途的掉电转移模式、以及从掉电模式向通常模式恢复的中途的掉电恢复模式各自中,最大1sec期间后端模块徒劳地消耗伴随3.3v电源供给的电力。此时,在通过小型蓄电池等电源容量较小的电源供给器所驱动的主装置中,短时间内电源枯竭,甚至情况更差。

59、此外,关于从掉电模式向通常模式的恢复需要最大1sec,即使掉电模式期间中主装置重新开始向后端模块的数据访问,实际上恢复为通常模式并进行向后端模块的访问为止至少需要待机1sec期间,主装置中需要保持1sec期间的数据的缓冲器,因此带来主装置的成本提升。

60、现有技术文献

61、专利文献

62、专利文献1:日本特开2015-232772号公报

63、非专利文献

64、非专利文献1:sd card association,“sd specifications part 1 physicallayer simplified specification version 4.10”,2013年1月22日,p.142-147

技术实现思路

1、本公开提供一种实现从通常模式向掉电模式转移为止的时间的缩短的从装置以及主装置。

2、本公开的一个例子中的从装置涉及经由多个信号线来与主装置连接的从装置。所述从装置具备控制器和后端模块。进一步地,在经由第1信号线接收从所述主装置供给的时钟信号、并且将从所述主装置供给的电源向所述控制器以及所述后端模块双方进行供给的第1模式(mode)时,进行以下的动作。所谓该动作是指,在通过所述控制器经由所述第2信号线而接收第1规定的信号样式(signal pattern)、并且在所述第1信号线中无法接收到所述时钟信号时,转移至停止向所述后端模块的电源供给的第2模式。在所述第2模式时,在所述第1信号线中成功接收到所述时钟信号时,转移至所述第1模式,并且经由所述第2信号线来发送第2规定的信号样式。

3、本公开的一个例子中的主装置经由多个信号线与从装置连接。

4、所述主装置具备:控制器、和向所述从装置供给电源的电源供给部。进一步地,由于对所述从装置进行数据收发,由所述电源供给部经由电源线向所述从装置供给电源,由所述控制器经由第1信号线供给时钟信号。在所述主装置对所述从装置不需要信号的收发时,在由所述控制器经由第2信号线发送了第1规定的信号样式之后,停止经由所述第1信号线的时钟信号的供给。所述主装置对所述从装置需要信号的收发时,由所述控制器经由所述第1信号线供给时钟信号。在所述控制器经由所述第2信号线接收到第2规定的信号样式之后,从所述主装置对所述从装置实施信号的收发。

5、根据本公开,能够缩短向掉电模式的转移所需的时间。

- 还没有人留言评论。精彩留言会获得点赞!