用于片上系统的实时时钟模块的装置和方法与流程

1.本公开总体而言涉及集成电路领域,具体而言涉及一种用于片上系统的实时时钟模块的装置和方法。

背景技术:

2.片上系统(system on chip,soc)可以包括实时时钟(real time clock,rtc)模块,从而为soc提供精确的时钟基准。独立于soc的电源的电池可以用于rtc模块的供电,这样可以在整个soc掉电的情况下仍然保持rtc模块的运行,从而向soc提供实时且准确的时钟信号和时间信息。

3.具体而言,纽扣电池可以用于rtc模块的供电。纽扣电池的容量相对较小,常用于rtc模块的纽扣电池的标称容量一般在200mah左右,但要维持rtc模块运行超过1年,因此该rtc模块的耗电电流一般在微安(μa)级别。纽扣电池的标称输出电压多为3v或1.5v,但是随着电池电量的减少,纽扣电池的实际输出电压会缓慢下降。尤其是在低温情况下,纽扣电池的稳态输出电压会比常温下的输出电压低不少。

4.集成在rtc模块外部的晶振(crystal oscillator)单元常常作为时钟源用于为rtc模块提供基础频率的时钟,该晶振单元通常包括32768 hz的无源晶体或者有源晶体,由晶振i/o单元以及晶振单元组成振荡环路,从而生成32768 hz的晶振时钟。需要向耦合到晶振单元的晶振i/o单元提供两个电源电压,即i/o电源电压(vdd_io)和内核电源电压(vdd_core),通常情况下vdd_io高于vdd_core。并且,rtc模块的内部逻辑也可以采用该内核电源电压(vdd_core)来供电。使用附加的外部电源模块来为rtc模块提供vdd_io和vdd_core这两个电源电压可能会造成成本提高。因此,可以考虑基于从纽扣电池输出的电压(vdd_bat)来生成vdd_io和vdd_core。

技术实现要素:

5.为了解决上述问题,本公开提供了一种用于soc的rtc模块的装置和方法,该装置可以包括调节器,并且被配置为基于电池输出电压(vdd_bat)提供i/o电源电压(vdd_io)和内核电源电压(vdd_core)。

6.根据本公开的第一方面,提供了一种用于片上系统soc的实时时钟rtc模块的供电的装置,其中,所述rtc模块由电池供电,所述装置被集成在rtc模块中,并且包括:第一调节器级,包含一个或多个调节器,其中,所述第一调节器级被配置为基于电池输出电压vdd_bat提供内核电源电压vdd_core;以及晶振i/o单元,所述晶振i/o单元由所述内核电源电压vdd_core和i/o电源电压vdd_io供电;其中,所述装置将电池输出电压vdd_bat直接提供为i/o电源电压vdd_io。

7.根据本公开的第二方面,提供了一种用于实现片上系统soc的实时时钟rtc模块,其中,所述rtc模块包括:根据本公开的第一方面所述的装置;以及电压检测模块,所述电压检测模块被配置为检测所述soc的主控模块的电源电压,并且在主控模块的电源电压低于

主控电源电压阈值的情况下,输出隔离使能信号,以从所述rtc模块隔离来自所述主控模块的信号。

8.根据本公开的第三方面,提供了一种用于片上系统soc的实时时钟rtc模块的供电的方法,其中,所述rtc模块由电池供电,所述方法包括:在电池输出电压vdd_bat的范围在i/o电源电压vdd_io的范围内的情况下,将电池输出电压vdd_bat直接提供为i/o电源电压vdd_io,并且利用所述rtc模块内的包含一个或多个调节器的第一调节器级将电池输出电压vdd_bat转换为内核电源电压vdd_core;以及在电池输出电压vdd_bat的范围不在i/o电源电压vdd_io的范围内的情况下:利用所述rtc模块内的与所述第一调节器级串联耦合并且包含一个或多个调节器的第二调节器级将电池输出电压vdd_bat转换为i/o电源电压vdd_io,并且利用所述第一调节器级将由所述第二调节器级提供的i/o电源电压vdd_io转换为内核电源电压vdd_core,或者利用所述rtc模块内的与所述第一调节器级并联耦合并且包含一个或多个调节器的第二调节器级将电池输出电压vdd_bat转换为i/o电源电压vdd_io,并且利用所述第一调节器级将电池输出电压vdd_bat转换为内核电源电压vdd_core;其中,所述内核电源电压vdd_core和所述i/o电源电压vdd_io用于向晶振i/o单元供电。

9.根据本公开的第四方面,提供了一种用于片上系统soc的实时时钟rtc模块的方法,其中,所述方法包括:根据本公开的第三方面所述的方法;以及利用所述rtc模块内的电压检测模块检测所述soc的主控模块的电源电压,并且在主控模块的电源电压低于主控电源电压阈值的情况下,输出隔离使能信号,以从所述rtc模块隔离来自所述主控模块的信号。

10.通过以下参照附图对本公开的示例性实施例的详细描述,本公开的其它特征及其优点将会变得清楚。

附图说明

11.构成说明书的一部分的附图描述了本公开的实施例,并且连同说明书一起用于解释本公开的原理。

12.参照附图,根据下面的详细描述,可以更加清楚地理解本公开,其中:图1是图示根据本公开的实施例的系统的至少一部分的示意图;图2是图示根据本公开的实施例的系统的至少一部分的示意图;图3是图示根据本公开的实施例的系统的至少一部分的示意图;图4是图示根据本公开的实施例的系统的至少一部分的示意图;图5是图示根据本公开的实施例的系统的至少一部分的示意图;图6是图示根据本公开的实施例的系统的至少一部分的示意图;图7是图示根据本公开的实施例的系统的至少一部分的示意图;图8是图示根据本公开的实施例的soc中的电压检测模块的波形图;图9是图示根据本公开的实施例的用于soc的方法的流程图;图10是图示根据本公开的实施例的用于soc的方法的流程图。

13.为了便于理解,在附图等中所示的各结构的位置、尺寸及范围等有时不表示实际的位置、尺寸及范围等。因此,公开并不限于附图等所公开的位置、尺寸及范围等。此外,附

图不必按比例绘制,一些特征可能被放大以示出具体组件的细节。

具体实施方式

14.现在将参照附图来详细描述本公开的各种示例性实施例。应注意到:除非另外具体说明,否则在这些实施例中阐述的部件和步骤的相对布置、数字表达式和数值不限制本公开的范围。

15.以下对至少一个示例性实施例的描述实际上仅仅是说明性的,决不作为对本公开及其应用或使用的任何限制。也就是说,本文中的电路和方法是以示例性的方式示出,来说明本公开中的电路或方法的不同实施例,而并非意图限制。本领域的技术人员将会理解,它们仅仅说明可以用来实施本公开的示例性方式,而不是穷尽的方式。

16.对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为授权说明书的一部分。

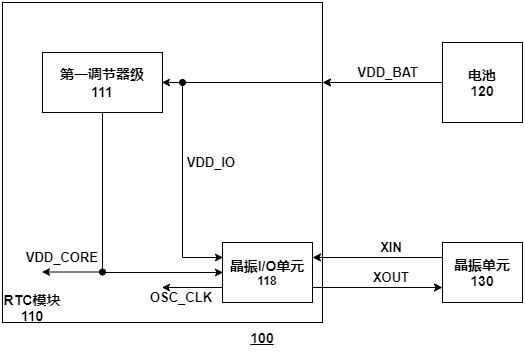

17.图1是图示根据本公开的实施例的系统的至少一部分的示意图。如图1所示,装置100可以是该系统的一部分,其包括soc的rtc模块110、电池120和晶振单元130。

18.电池120可以被配置为在soc掉电的情况下向rtc模块110提供电池输出电压vdd_bat。在本公开的实施例中,电池120可以是纽扣电池。但应注意的是,本公开中可以用于rtc模块的供电的电源不限于此,也可以使用其他类型的电池或超级电容器等。在本公开中,vdd_bat可能相对于标称输出电压有所变化。例如,由于低温或由于电池的电量减少之类的原因,vdd_bat可能会降低。

19.在本公开的实施例中,在soc未掉电的情况下,可以由soc的主电源而非电池120为rtc模块110供电。在本公开的实施例中,在soc未掉电的情况下,也可以仍仅由电池120为rtc模块110供电。

20.晶振单元130可以包括32768 hz的无源晶体,被配置为通过xin和xout端口耦合到rtc模块110内的晶振i/o单元118以形成振荡环路,从而生成32768 hz晶振时钟osc_clk,并且晶振i/o单元118可以将生成的osc_clk提供给rtc模块110。应注意的是,本公开中可以用于生成晶振时钟osc_clk的晶体不限于无源晶体,并且生成的晶振时钟osc_clk的频率不限于32768 hz。

21.在根据本公开的实施例中,晶振单元130也可以是有源晶振,并且可以将i/o电源电压vdd_io输出到晶振单元130从而为有源晶振供电。

22.在本公开中,后文将提及的电池220、320、420、520、620、720等可以类似于电池120,并且后文将提及的晶振单元230、330、430、530、630、730等可以类似于晶振单元130,因此将不在后文详述。

23.图1中所示的rtc模块110可以适用于i/o电源电压vdd_io的范围能够覆盖电池120的输出电压vdd_bat的变化范围的情况,即,vdd_bat保持在vdd_io的范围内。作为非限制性示例,图1中所示的vdd_io可以在从1.8v至3.3v的范围内,而vdd_bat的标称值可以为3.0v,欠压阈值可以被设置为vdd_bat_th = 2.2v,即,可以认为vdd_bat的正常工作范围为从2.2v至3.0v。由于i/o电源电压的范围1.8v≤vdd_io≤3.3v能够覆盖电池输出电压的范围2.2v≤vdd_bat≤3.0v,因此可以通过直接将vdd_bat提供为vdd_io来为rtc模块供电。但是,用于为rtc模块供电的内核电源电压vdd_core不能直接由vdd_bat提供。

24.如图1所示,rtc模块110可以包括第一调节器级111,该第一调节器级111可以包括一个或多个调节器并且被配置为直接地基于vdd_bat生成vdd_core。例如,第一调节器级111可以包括能够将vdd_bat转换为vdd_core的任意调节器,诸如,低压差线性稳压器、开关稳压器等。具体而言,vdd_bat可以经由rtc模块110的模拟端口avdd提供到集成在rtc模块110内的第一调节器级111,由第一调节器级111转换得到的vdd_core可以提供到晶振i/o单元118,并且vdd_bat还可以直接走线或者直接在rtc模块110内提供给晶振i/o单元118。此外,晶振时钟osc_clk可以由晶振i/o单元118提供到rtc模块110。这里,i/o电源电压vdd_io可以是指用于rtc模块的输入/输出端口的电源电压,该电压vdd_io可以被提供到rtc模块110的外围;内核电源电压vdd_core可以是指用于rtc模块的内部逻辑的电源电压,该电压可以被提供到rtc模块110的内部逻辑,也可以被提供到rtc模块110的外围。

25.rtc模块110还可以包括晶振i/o单元118,该晶振i/o单元118可以被配置为由电源电压(诸如,i/o电源电压vdd_io和内核电源电压vdd_core)供电。

26.虽然未在图1中示出,但是rtc模块110还可以包括分频器、计数器、寄存器、控制逻辑等模块,这些模块在本领域是公知的,因此在本文中未详述。

27.图1所示的电路可以在soc掉电的情况下利用电池120有利地保持rtc模块110的稳定供电。

28.应理解的是,图1中的第一调节器级111被示出为集成在rtc模块110内,但第一调节器级111也可以在rtc模块110之外并且耦合到rtc模块110和电池120以基于vdd_bat来为rtc模块供电。

29.图2是图示根据本公开的实施例的系统的至少一部分的示意图。如图2所示,装置200可以是该系统的一部分,其包括soc的rtc模块210、电池220和晶振单元230。

30.rtc模块210不同于图1中所示的rtc模块110,rtc模块210可以适用于i/o电源电压vdd_io的范围不能覆盖电池输出电压vdd_bat的变化范围的情况,即,vdd_bat不在vdd_io的范围内的情况。作为非限制性示例,vdd_io的范围不能覆盖vdd_bat的变化范围的情况包括:vdd_io的范围与vdd_bat的范围相比过窄,甚至被vdd_bat的范围覆盖,诸如,vdd_io的范围为1.8v

±

10%,而vdd_bat的正常工作范围为从1.8v至3.0v;vdd_io的范围与vdd_bat的范围相互错位,即,仅部分重合,甚至完全不重合,诸如,vdd_bat的正常工作范围为从1.8v至3.0v,而vdd_io的范围为从1.2v至1.8v。在此类情况下,无法如图1中的rtc模块110一样直接将vdd_bat提供为vdd_io,因此,rtc模块可以包括两个调节器级,以提供vdd_io和vdd_core两者。

31.如图2所示,rtc模块210可以包括串联耦合的第一调节器级211和第二调节器级212,该第一调节器级211和第二调节器级212可以各自包括一个或多个调节器并且被配置为基于电池输出电压vdd_bat分别提供内核电源电压vdd_core和i/o电源电压vdd_io。第二调节器级212可以被配置为将vdd_bat转换为vdd_io,串联耦合到第二调节器级212的第一调节器级211可以被配置为将由第二调节器级212转换得到的vdd_io转换为vdd_core,从而间接地基于vdd_bat生成vdd_core。第一调节器级211和第二调节器级212可以包括能够进行上述电压转换的任意调节器,诸如,低压差线性稳压器、开关稳压器等。对于包括诸如低压差线性稳压器之类的降压调节器的rtc模块,图2的配置适用于vdd_io》vdd_core的情况。具体而言,vdd_bat可以经由rtc模块210的模拟端口avdd提供到集成在rtc模块210内的第

二调节器级212,由第二调节器级212转换得到的vdd_io可以直接走线在rtc模块内提供到晶振i/o单元218,并且由第一调节器级211转换得到的vdd_core可以提供到晶振i/o单元218。此外,晶振时钟osc_clk可以由晶振i/o单元218提供到rtc模块210。

32.图3是图示根据本公开的实施例的系统的至少一部分的示意图。如图3所示,装置300可以是该系统的一部分,其包括soc的rtc模块310、电池320和晶振单元330。

33.rtc模块310类似于前文参照图2描述的rtc模块210,区别之处在于,rtc模块310中包括并联耦合并且各自包含一个或多个调节器的第一调节器级311和第二调节器级312,其中,第一调节器级311可以被配置为将vdd_bat转换为vdd_core,第二调节器级312可以被配置为将vdd_bat转换为vdd_io。第一调节器级311和第二调节器级312可以包括能够进行上述电压转换的任意调节器,诸如,低压差线性稳压器、开关稳压器等。具体而言,vdd_bat可以经由rtc模块310的模拟端口avdd提供到集成在rtc模块310内的第一调节器级311和第二调节器级312,由第一调节器级311转换得到的vdd_core可以提供到晶振i/o单元318,并且由第二调节器级312转换得到的vdd_io可以直接走线在rtc模块内提供给晶振i/o单元318。此外,晶振时钟osc_clk可以由晶振i/o单元318提供到rtc模块310。

34.图4是图示根据本公开的实施例的系统的至少一部分的示意图。如图4所示,装置400可以是该系统的一部分,其包括soc的rtc模块410、电池420和晶振单元430。

35.rtc模块410类似于前文参照图2描述的rtc模块210,区别之处在于,rtc模块410中包括串联耦合并且各自包含一个或多个调节器的第一调节器级411、第二调节器级412和第三调节器级413,其中,第二调节器级412可以被配置为将vdd_bat转换为vdd_io,串联耦合的第一调节器级411和第三调节器级413可以被配置为将由第二调节器级412转换得到的vdd_io转换为vdd_core。第一调节器级411、第二调节器级412和第三调节器级413可以包括能够进行上述电压转换的任意调节器,诸如,低压差线性稳压器、开关稳压器等。具体而言,vdd_bat可以经由rtc模块410的模拟端口avdd提供到集成在rtc模块410内的第二调节器级412,由串联耦合的两个调节器级413和411转换得到的vdd_core可以提供到晶振i/o单元418,并且由第二调节器级412转换得到的vdd_io可以直接走线在rtc模块内提供到晶振i/o单元418。此外,晶振时钟osc_clk可以由晶振i/o单元318提供到rtc模块410。

36.图4中示出的rtc模块410的配置与图2所示的rtc模块210的配置类似,即类似地,rtc模块410中包括的多个调节器级串联耦合。与图2的配置相比,图4中所示的配置可以有利地应用于单个第一调节器级411无法基于vdd_io提供所需的vdd_core的情况,例如,单个第一调节器级411无法提供足够大的电压幅度范围的vdd_core的情况。但应理解的是,rtc模块中包括的多个调节器级可以根据需要采取其他配置。例如,在rtc模块的数字端口dvdd需要更大的电流的情况下,第一调节器级411和第三调节器级413可以并联耦合,以提供更大的电流。应理解的是,第三调节器级413也可以与第二调节器级412串联或并联耦合之后串联耦合到第一调节器级411,以提供所需的电力供应。类似地,应理解的是,也可以对图3中所示的rtc模块310增加第三调节器级,该第三调节器级可以与第一调节器级和第二调节器级中的一个调节器级串联或并联耦合之后耦合到第一调节器级和第二调节器级中的另一个调节器级,以提供所需的电力供应。此外,应理解的是,rtc模块不限于包括提供vdd_io和vdd_core两个电源电压的2个或3个调节器级,而是可以根据需要包括更多的调节器级。

37.图5是图示根据本公开的实施例的系统的至少一部分的示意图。如图5所示,装置

500可以是该系统的一部分,其包括soc的rtc模块510、电池520和晶振单元530。

38.rtc模块510类似于前文参照图2描述的rtc模块210。具体而言,rtc模块510可以包括第一调节器级512、第二调节器级511和晶振i/o单元518,分别类似于前文所述的第一调节器级212、第二调节器级211和晶振i/o单元218。区别之处在于,rtc模块510被示出为在内部还集成有带隙(bandgap)电路514,该带隙电路514可以被配置为生成提供给rtc模块510中包括的调节器级511、512的共同的参考电压v_ref。对于图3和图4中示出的rtc模块310、410,也可以类似地包括带隙电路以提供rtc模块内的调节器级共用的参考电压v_ref,以提供多个调节器级之间的相对校准。应理解的是,本公开中的rtc模块均可以类似地包括提供参考电压v_ref的带隙电路。

39.图6是图示根据本公开的实施例的系统的至少一部分的示意图。如图6所示,装置600可以是该系统的一部分,其包括soc的rtc模块610、电池620、晶振单元630和soc的主控模块640。

40.图6中所示的rtc模块610类似于前文参照图1描述的rtc模块110。具体而言,rtc模块610可以包括第一调节器级611和晶振i/o单元618,分别类似于前文所述的第一调节器级112和晶振i/o单元118。区别之处在于,rtc模块610被示出为还包括欠压检测模块615。欠压检测模块615被配置为对电池620的电池输出电压vdd_bat进行欠压检测,并且在检测到电池输出电压vdd_bat低于电池输出电压阈值(诸如,欠压阈值vdd_bat_th)的情况下生成欠压指示信号。该欠压指示信号可以被保存在rtc模块内并输出到soc的主控模块640,以触发工作状态中的soc主控模块640内的关于电池的欠压报警。

41.在根据本公开的实施例中,集成在rtc模块610内的欠压检测模块615可以与rtc模块610内的调节器级(诸如,第一调节器级611)共用参考电压(诸如,前文所述的由带隙电路生成的参考电压v_ref)。电池输出电压阈值可以被设定为由带隙电路生成的参考电压v_ref的倍数,诸如整数倍。

42.作为非限制性示例,v_ref=0.75v,电池标称的输出电压为3v,则电池输出电压阈值(诸如,欠压阈值vdd_bat_th)可以被设定为3*v_ref=2.25v。在vdd_bat刚下降到3*v_ref时,此时rtc模块610虽然工作在欠压情况下,但电池620的供电仍能支持rtc模块610正常工作达一段时间。在这种情况下,欠压检测模块615可以输出有效的欠压指示,该欠压指示可以被寄存器锁存在rtc模块610内,并输出给soc的主控模块。从而,之后在soc的主控模块上电工作时,就可以收到电池欠压报警,指导用户更换纽扣电池。如若纽扣电池供电电压下降到rtc模块完全无法正常工作的程度,则rtc模块的计时会失效,但不会对soc的功能造成影响。

43.图7是图示根据本公开的实施例的系统的至少一部分的示意图。如图7所示,装置700可以是该系统的一部分,其包括soc的rtc模块710、电池720、晶振单元730和soc的主控模块740。

44.由于rtc模块是集成在soc上的专用电路,因此需要接受soc上的主控模块的控制和访问。但是,rtc模块有自己的独立供电,并且在soc的其他模块掉电的情况下,rtc模块仍然维持运行。因此,对于要传输到rtc模块的来自soc的主控模块的控制和访问信号,需要在rtc模块内进行隔离处理,从而防止在soc的主控模块掉电的情况下将未知状态引入rtc模块。

45.图7中所示的rtc模块710类似于前文参照图1描述的rtc模块110。具体而言,rtc模块710可以包括第一调节器级711和晶振i/o单元718,分别类似于前文所述的第一调节器级112和晶振i/o单元118。区别之处在于,rtc模块710被示出为还包括电压检测模块716和逻辑门717。电压检测模块716可以被配置为耦合到soc的主控模块740,以检测主控模块740的电源电压vdd_main。在检测到电源电压vdd_main低于阈值的情况下,可以判断为soc的主控模块740处于掉电状态,此时电压检测模块716输出隔离使能信号en_iso,该隔离使能信号en_iso可以在主控模块740被判断为处于掉电状态的情况下处于有效电平,以隔离来自主控模块740的信号ctl_main,使得该信号ctl_main不通过逻辑门717。在检测到电源电压vdd_main不低于阈值的情况下,可以判断为soc的主控模块740处于正常状态,此时电压检测模块716输出的隔离使能信号en_iso处于无效电平,从而不会隔离来自主控模块740的信号ctl_main,该信号ctl_main通过逻辑门717以供rtc模块710内的模块使用。在根据本公开的实施例中,对来自主控模块740的信号ctl_main的隔离可以通过集成在rtc模块710内的逻辑门717来实现。图7中示出的逻辑门717仅仅是示例,可以根据隔离使能信号en_iso的有效电平的极性以及其他需要改变为其他逻辑门。

46.在根据本公开的实施例中,主控模块740可以与rtc模块710内的其他模块(诸如,第一调节器级711、逻辑门717等)共用由同一带隙电路生成的参考电压v_ref。

47.在根据本公开的实施例中,rtc模块710可以接收来自soc的多个电源域的控制和访问信号。在这种情况下,rtc模块710可以包括与这些电源域对应的多个电压检测模块,其中每个电压检测模块可以被配置为检测对应的一个电源域的电源电压,并且在该电源域的电源电压低于阈值的情况下输出隔离使能信号以从rtc模块隔离来自该掉电的电源域的控制和访问信号。相应地,rtc模块710可以包括与这些电源域对应的多个逻辑门,其中每个逻辑门被配置为基于相应的隔离使能信号来隔离或通过对应的电源域的控制和访问信号。

48.图8是图示根据本公开的实施例的soc中的电压检测模块的波形图。如图8所示,响应于soc的主控模块的电源电压vdd_main增大到高于阈值vdd_main_th,即主控模块从掉电状态恢复到正常状态(换言之,上电过程),隔离使能信号en_iso相应地从有效电平变为无效电平,以指示主控模块的电压达到正常值。在该实施例中,隔离使能信号en_iso的有效电平为高电平,无效电平为低电平。响应于主控模块从掉电状态到正常状态的改变而发生的隔离使能信号的改变可以具有时延dly1,该时延dly1可以被设置为微秒级别,诸如,小于2μs,并且适当增大该dly1是有利的,例如能够更好地确保隔离的可靠性。响应于vdd_main减小到低于阈值vdd_main_th,即主控模块从正常状态改变为掉电状态(换言之,下电过程),隔离使能信号en_iso相应地从无效电平变为有效电平,以指示主控模块的下电。响应于主控模块从正常状态到掉电状态的改变而发生的隔离使能信号的改变可以具有时延dly2,该时延dly2可以被设置为微秒级别,诸如,小于2μs,并且适当减小该dly2是有利的,例如能够避免vdd_main降低到失效电压时,延迟后的隔离使能信号en_iso还没有响应于下电过程而改变其电平,从而更好地确保隔离的可靠性。

49.应理解的是,图8中示出的有效电平为高电平并且无效电平为低电平的实施例仅仅是示例性的,也可以将隔离使能信号en_iso的有效电平设置为低电平,无效电平设置为高电平。

50.在本公开中,主控模块的电源电压的阈值vdd_main_th应被设置为高于主控模块

的失效电压,并且与下电过程中隔离使能信号en_iso的电平翻转的时延dly2相关联。在根据本公开的实施例中,vdd_main_th可以基于主控模块在上电之后的稳定电源电压vdd_main_high来设置,例如如图8所示,将阈值vdd_main_th设置为vdd_main_th=95%*vdd_main_high。

51.图9是图示根据本公开的实施例的用于soc的方法的流程图,该方法900适用于vdd_bat在vdd_io的范围内的情况。如图9所示,在s91处,可以将vdd_bat直接提供为vdd_io;接着,在s92处,可以利用rtc模块内的第一调节器级将vdd_bat转换为vdd_core。

52.图10是图示根据本公开的实施例的用于soc的方法的流程图,该方法1000适用于vdd_bat不在vdd_io的范围内的情况。如图10所示,在s101处,可以利用rtc模块内的与第一调节器级串联或并联耦合的第二调节器级将vdd_bat转换为vdd_io;接着,在s102处,可以利用第一调节器级将vdd_bat或由第二调节器级提供的vdd_io转换为vdd_core。

53.在这里示出和讨论的所有示例中,任何具体值应被解释为仅仅是示例性的,而不是作为限制。因此,示例性实施例的其它示例可以具有不同的值。

54.如在此所使用的,词语“示例性的”意指“用作示例、实例或说明”,而不是作为将被精确复制的“模型”。在此示例性描述的任意实现方式并不一定要被解释为比其它实现方式优选的或有利的。而且,本公开不受在上述技术领域、背景技术、发明内容或具体实施方式中所给出的任何所表述的或所暗示的理论所限定。

55.还应理解,“包括/包含”一词在本文中使用时,说明存在所指出的特征、整体、步骤、操作、单元和/或组件,但是并不排除存在或增加一个或多个其它特征、整体、步骤、操作、单元和/或组件以及/或者它们的组合。

56.另外,在本公开的描述中,术语“第一”、“第二”、“第三”等仅用于描述目的,而不能理解为指示或暗示相对重要性和顺序。

57.本领域技术人员应当意识到,在上述操作之间的边界仅仅是说明性的。多个操作可以结合成单个操作,单个操作可以分布于附加的操作中,并且操作可以在时间上至少部分重叠地执行。而且,另选的实施例可以包括特定操作的多个实例,并且在其他各种实施例中可以改变操作顺序。但是,其它的修改、变化和替换同样是可能的。因此,本说明书和附图应当被看作是说明性的,而非限制性的。

58.虽然已经通过示例对本公开的一些特定实施例进行了详细说明,但是本领域的技术人员应该理解,以上示例仅是为了进行说明,而不是为了限制本公开的范围。在此公开的各实施例可以任意组合,而不脱离本公开的精神和范围。本领域的技术人员还应理解,可以对实施例进行多种修改而不脱离本公开的范围和精神。本公开的范围由所附权利要求来限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1