延迟电路单元的版图、延迟电路的版图和半导体存储器的制作方法

1.本公开涉及集成电路技术领域,尤其涉及一种延迟电路单元的版图、延迟电路的版图和半导体存储器。

背景技术:

2.半导体器件(例如半导体存储器或者用于控制半导体存储器的控制器等)利用与输出数据同步的时钟信号(例如,数据选通信号dqs)来传送输出数据。

3.半导体器件可以将时钟信号的相位调节为期望值,并且与时钟信号同步地输出数据。例如,在延迟锁相环(delay locked loop,dll)中,延迟锁相环通过延迟时间调整操作来输出具有期望相位的时钟信号,并与时钟信号同步地输出数据。其中,延迟锁相环中的粗延迟调整电路(coarse delay adjustment circuit,cdl)则是通过多个延迟级延迟参考时钟信号,以输出具有延迟级相位差的两个相位信号。

技术实现要素:

4.本公开提供了一种延迟电路单元的版图、延迟电路的版图和半导体存储器,能够实现不同相位信号的延时一致性。

5.本公开的技术方案是这样实现的:

6.第一方面,本公开实施例提供了一种延迟电路单元的版图,该版图包括多个版图单元,所述版图单元用于形成与非门电路,且所述版图单元呈阵列排布;其中,

7.在所述阵列的第一行中,顺序排布有若干个符合第一布局方式的所述版图单元;

8.在所述阵列的第二行中,顺序排布有若干个符合第二布局方式的所述版图单元;

9.其中,所述第一布局方式与所述第二布局方式不同,而且所述第一布局方式和所述第二布局方式使得所述第一行与所述第二行呈中心对称结构。

10.在一些实施例中,所述版图单元至少包括第一输入信号线、第二输入信号线和输出信号线;其中,

11.在所述第一布局方式下,所述版图单元的信号线沿从右至左方向的排布顺序均为:所述第二输入信号线,所述输出信号线,所述第一输入信号线;

12.在所述第二布局方式中,所述版图单元的信号线沿从右至左方向的排布顺序均为:所述第一输入信号线,所述输出信号线,所述第二输入信号线。

13.在一些实施例中,所述版图至少划分为第一金属层和第二金属层,所述第二金属层位于所述第一金属层上层;其中,

14.所述第一金属层,用于布局所述第一输入信号线、所述第二输入信号线、所述输出信号线以及第一层信号线;

15.所述第二金属层,用于布局第二层信号线;

16.其中,所述第一输入信号线、所述第二输入信号线、所述输出信号线以及所述第一层信号线均沿第一方向布线,所述第二层信号线沿第二方向布线,所述第一方向与所述第

二方向的夹角为90度。

17.在一些实施例中,所述第一层信号线至少包括:第一信号线、第二信号线、第三信号线、第四信号线、第五信号线和第六信号线;

18.所述第二层信号线至少包括:第一输入接口信号线、第一输出接口信号线、第二输入接口信号线、第二输出接口信号线、第三输入接口信号线和第三输出接口信号线。

19.在一些实施例中,所述第一层信号线排布于每一个所述版图单元的两侧;其中,

20.所述第一层信号线沿从右至左方向的排布顺序为:所述第一信号线、所述第二信号线、所述第三信号线、所述第四信号线、所述第五信号线和所述第六信号线。

21.在一些实施例中,所述第一层信号线还包括若干个冗余信号线,其中,

22.所述第一层信号线沿从右至左方向的排布顺序为:所述第一信号线、所述第二信号线、所述第三信号线、所述第四信号线、所述第五信号线、所述第六信号线和所述若干个冗余信号线。

23.在一些实施例中,在所述第一金属层中,若干所述第一层信号线的宽度相同,而且每相邻两个信号线之间的间距相同。

24.在一些实施例中,所述第二层信号线还包括若干个中间连接线,且每一个所述中间连接线上设置有连接点;其中,

25.所述若干个中间连接线,用于将所述第一金属层中设置有连接点的信号线进行连接,以实现将目标信号传输至对应的所述与非门电路。

26.在一些实施例中,所述多个版图单元包括第一版图单元、第二版图单元、第三版图单元、第四版图单元、第五版图单元、第六版图单元、第七版图单元和第八版图单元,且在所述第一金属层呈2

×

4阵列排布;其中,

27.在所述阵列的第一行中,沿从右至左方向顺序排布所述第四版图单元、所述第二版图单元、所述第三版图单元和所述第一版图单元;其中,所述第四版图单元用于形成第四与非门电路,所述第二版图单元用于形成第二与非门电路,所述第三版图单元用于形成第三与非门电路,所述第一版图单元用于形成第一与非门电路;

28.在所述阵列的第二行中,沿从右至左方向顺序排布所述第八版图单元、所述第六版图单元、所述第七版图单元和所述第五版图单元;其中,所述第八版图单元用于形成第八与非门电路,所述第六版图单元用于形成第六与非门电路,所述第七版图单元用于形成第七与非门电路;所述第五版图单元用于形成第五与非门电路。

29.在一些实施例中,在所述第一版图单元和所述第五版图单元的左侧和右侧均排布冗余信号线;

30.在所述第三版图单元和所述第七版图单元的左侧和右侧依次排布所述第六信号线和所述第五信号线;

31.在所述第二版图单元和所述第六版图单元的左侧和右侧依次排布所述第四信号线和所述第三信号线;

32.在所述第四版图单元和所述第八版图单元的左侧和右侧依次排布所述第二信号线和所述第一信号线。

33.在一些实施例中,所述若干个中间连接线划分为第一组中间连接线和第二组中间连接线;其中,

34.在所述第二金属层中,对应于所述第四版图单元、所述第二版图单元、所述第三版图单元和所述第一版图单元的位置,排列有所述第一组中间连接线以及所述第一输入接口信号线和所述第一输出接口信号线;

35.在所述第二金属层中,对应于所述第八版图单元、所述第六版图单元、所述第七版图单元和所述第五版图单元的位置,排列有所述第二组中间连接线以及所述第二输入接口信号线、所述第二输出接口信号线、所述第三输入接口信号线和所述第三输出接口信号线。

36.在一些实施例中,其特征在于,所述第一组中间连接线,用于将所述第四版图单元、所述第二版图单元、所述第三版图单元和所述第一版图单元中的部分信号线在所述第一金属层对应连接;

37.所述第二组中间连接线,用于将所述第八版图单元、所述第六版图单元、所述第七版图单元和所述第五版图单元中的部分信号线在所述第一金属层对应连接。

38.在一些实施例中,所述与非门电路包括第一pmos管、第二pmos管、第一nmos管和第二nmos管;所述第二金属层还包括电源线和接地线;其中,

39.所述电源线分别与所述第一pmos管和所述第二pmos管的源极连接;

40.所述接地线与所述第一nmos管的源极连接;

41.所述第一输入信号线分别与所述第二pmos管的栅极和所述第二nmos管的栅极连接;

42.所述第二输入信号线分别与所述第一pmos管的栅极和所述第一nmos管的栅极连接;

43.所述输出信号线分别与所述第一pmos管的漏极、所述第二pmos管的漏极以及所述第二nmos管的漏极连接。

44.第二方面,本公开实施例提供了一种延迟电路的版图,该延迟电路包括n个延迟电路单元,每一个延迟电路单元对应于如第一方面任一项所述的版图;其中,n为大于零的整数。

45.在一些实施例中,所述延迟电路的版图是由n个所述延迟电路单元的版图级联组成的;其中,

46.第一版图输入的第一输入接口信号为第二版图输出的第一输出接口信号;

47.所述第二版图输入的第二输入接口信号为所述第一版图输出的第二输出接口信号;

48.所述第二版图输入的第三输入接口信号为所述第一版图输出的第三输出接口信号;

49.其中,所述第一版图和所述第二版图表示所述延迟电路的版图中两个相邻的所述延迟电路单元的版图。

50.第三方面,本公开实施例提供了一种半导体存储器,包括如第二方面任一项所述延迟电路的版图对应的延迟电路。

51.本公开实施例所提供的一种延迟电路单元的版图、延迟电路的版图和半导体存储器,该延迟电路单元的版图包括多个版图单元,版图单元用于形成与非门电路,且版图单元呈阵列排布;其中,在阵列的第一行中,顺序排布有若干个符合第一布局方式的版图单元;在阵列的第二行中,顺序排布有若干个符合第二布局方式的版图单元;其中,第一布局方式

与第二布局方式不同,而且第一布局方式和第二布局方式使得第一行与第二行呈中心对称结构。这样,该版图中的多个版图单元呈阵列排布,不仅有利于实现不同相位信号之间的延时一致性,而且延迟电路单元的版图整体排布紧促,还能够节省版图面积。

附图说明

52.图1为本公开实施例提供的一种延迟电路的组成结构示意图;

53.图2为本公开实施例提供的一种延迟电路单元的电路结构示意图;

54.图3为本公开实施例提供的一种延迟电路单元的版图的组成结构示意图;

55.图4为本公开实施例提供的一种与非门电路的电路结构示意图;

56.图5为本公开实施例提供的一种延迟电路单元的版图的详细结构示意图;

57.图6为本公开实施例提供的另一种延迟电路单元的版图的详细结构示意图;

58.图7本公开实施例提供的一种栅源层的版图结构示意图;

59.图8为本公开实施例提供的一种版图单元的组成结构示意图;

60.图9为本公开实施例提供的一种延迟电路单元的版图的局部放大示意图;

61.图10为本公开实施例提供的一种延迟电路单元的版图的简化结构示意图;

62.图11为本公开实施例提供的另一种延迟电路单元的版图的局部放大示意图;

63.图12为本公开实施例提供的再一种延迟电路单元的版图的详细结构示意图;

64.图13为本公开实施例提供的另一种延迟电路单元的版图的简化结构示意图;

65.图14为本公开实施例提供的再一种延迟电路单元的版图的简化结构示意图;

66.图15为本公开实施例提供的一种延迟电路的版图结构示意图;

67.图16为本公开实施例提供的另一种延迟电路的版图结构示意图;

68.图17为本公开实施例提供的一种半导体存储器的组成结构示意图。

具体实施方式

69.下面将结合本公开实施例中的附图,对本公开实施例中的技术方案进行清楚、完整地描述。可以理解的是,此处所描述的具体实施例仅用于解释相关公开,而非对该公开的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与有关公开相关的部分。

70.除非另有定义,本文所使用的所有的技术和科学术语与属于本公开的技术领域的技术人员通常理解的含义相同。本文中所使用的术语只是为了描述本公开实施例的目的,不是旨在限制本公开。

71.在以下的描述中,涉及到“一些实施例”,其描述了所有可能实施例的子集,但是可以理解,“一些实施例”可以是所有可能实施例的相同子集或不同子集,并且可以在不冲突的情况下相互结合。

72.需要指出,本公开实施例所涉及的术语“第一\第二\第三”仅仅是区别类似的对象,不代表针对对象的特定排序,可以理解地,“第一\第二\第三”在允许的情况下可以互换特定的顺序或先后次序,以使这里描述的本公开实施例能够以除了在这里图示或描述的以外的顺序实施。

73.半导体器件利用与输出数据同步的时钟信号来传送输出数据,半导体器件可以将时钟信号的相位调节为期望值,并且与时钟信号同步地输出数据。例如,在延迟锁相环中,

延迟锁相环通过延迟时间调整操作来输出具有期望相位的时钟信号,并与时钟信号同步地输出数据。其中,延迟锁相环中的粗延迟调整电路(简称粗延迟电路)通过多个延迟级延迟参考时钟信号,以输出具有延迟级相位差的两个相位信号。

74.本公开实施例提供了一种延迟电路单元的版图,该版图包括多个版图单元,版图单元用于形成与非门电路,且版图单元呈阵列排布;其中,在阵列的第一行中,顺序排布有若干个符合第一布局方式的版图单元;在阵列的第二行中,顺序排布有若干个符合第二布局方式的版图单元;其中,第一布局方式与第二布局方式不同,而且第一布局方式和第二布局方式使得第一行与第二行呈中心对称结构。这样,不仅有利于实现不同相位信号之间的延时一致性,而且延迟电路单元的版图整体排布紧促,还能够节省版图面积。

75.下面将结合附图对本公开各实施例进行详细说明。

76.参见图1,其示出了本公开实施例提供的一种延迟电路的组成结构示意图,该延迟电路可以为dll中的粗延迟电路。如图1所示,在该延迟电路中,包括若干个延迟电路单元(对于粗延迟电路而言,延迟电路单元即cdl单元),对于每一个cdl单元,第一输入接口信号(inf信号)从cdl单元的左侧输入,第二输入接口信号(ine信号)和第三输入接口信号(ino信号)从cdl单元的右侧输入,经过cdl单元的延迟处理,得到第一输出接口信号(outf信号),从cdl单元的右侧输出,并得到第二输出接口信号(oute信号)和第三输出接口信号(outo)信号,从cdl单元的左侧输出。

77.也就是说,在图1所示的延迟电路中,对于每一个cdl单元而言,在从右至左的方向,ine信号和ino信号为输入信号,经过延迟处理后得到的oute信号和outo信号为输出信号;对于相邻的两个cdl单元,右侧的cdl单元输出的oute信号为左侧的cdl单元输入的ine信号,右侧的cdl单元输出的outo信号为左侧的cdl单元输入的ino信号。在从左至右的方向,inf信号为输入信号,经过延迟处理后得到的outf为输出信号,对于相邻的两个cdl单元,左侧的cdl单元输出的outf信号为右侧的cdl单元输入的inf信号;这样,若干个cdl单元级联形成延迟电路,该延迟电路通过若干个cdl单元的配合工作实现对信号的延迟处理。

78.对于每一个cdl单元,参见图2,其示出了本公开实施例提供的一种延迟电路单元的电路结构示意图。如图2所示,对于每一个cdl单元,其可以包括八个与非门电路:第一与非门电路nd1、第二与非门电路nd2、第三与非门电路nd3、第四与非门电路nd4、第五与非门电路nd5、第六与非门电路nd6、第七与非门电路nd7、第八与非门电路nd8。

79.如图2所示,在cdl单元中,每一个与非门电路均包括两个输入端和一个输出端。

80.对于第一与非门电路nd1,两个输入端分别连接至第一输入接口201和第一与非门输入接口202,两个输入信号分别为:来自第一输入接口201的第一输入接口信号(inf信号)和来自第一与非门输入接口202的第一与非门输入信号(infene信号);第一与非门电路nd1的输出信号为第一与非门输出信号(net12信号),第一与非门电路nd1的输出端与第二与非门电路nd2和第三与非门电路nd3的输入端分别连接。

81.对于第二与非门电路nd2,两个输入端分别连接至第一与非门电路nd1的输出端和第二与非门输入接口203,两个输入信号分别为:来自第一与非门电路nd1的第一与非门输出信号(net12信号)和第二与非门输入信号(infeno信号);第二与非门电路nd2的输出信号为第一输出接口信号(outf信号),第二与非门电路nd2的输出端与第四与非门电路nd4的输入端和第一输出接口204连接。

82.对于第三与非门电路nd3,两个输入端分别连接至第三与非门输入接口205和第一与非门电路nd1的输出端,两个输入信号分别为:来自第三与非门输入接口205的第三与非门输入信号(sele信号)和来自第一与非门电路nd1的第一与非门输出信号(net12信号);第三与非门电路nd3的输出信号为第三与非门输出信号(net37信号),第三与非门电路nd3的输出端与第七与非门电路nd7的输入端连接。

83.对于第四与非门电路nd4,两个输入端分别连接至第四与非门输入接口206和第二与非门电路nd2的输出端,两个输入信号分别为:来自第四与非门输入接口206的第四与非门输入信号(selo信号)和第一输出接口信号(outf信号);第四与非门电路nd4的输出信号为第四与非门输出信号(net46信号),第四与非门电路nd4的输出端与第六与非门电路nd6的输入端连接。

84.对于第五与非门电路nd5,两个输入端分别连接至电源端207和第六与非门电路nd6的输出端,两个输入信号分别为:来自电源端207的电源信号(vdd信号)和第六与非门输出信号(net56信号);第五与非门电路nd5的输出信号为第三输出接口信号(outo信号),第五与非门电路nd5的输出端连接至第三输出接口208。

85.对于第六与非门电路nd6,两个输入端分别连接至第三输入接口209和第四与非门电路nd4的输出端,两个输入信号分别为:来自第三输入接口209的第三输入接口信号(ino信号)和第四与非门输出信号(net46信号);第六与非门电路nd6的输出信号为第六与非门输出信号(net56信号),第六与非门电路nd6的输出端连接至第五与非门电路nd5的输入端。

86.对于第七与非门电路nd7,两个输入端分别连接至第三与非门电路nd3的输出端和第八与非门电路nd8的输出端,两个输入信号分别为:第三与非门输出信号(net37信号)和第八与非门输出信号(net78信号);第七与非门电路nd7的输出信号为第二输出接口信号(oute信号),第七与非门电路nd7的输出端连接至第二输出接口2010。

87.对于第八与非门电路nd8,两个输入端分别连接至电源端207和第二输入接口2011,两个输入信号分别为:电源信号(vdd信号)和第二输入接口信号(ine信号);第八与非门电路nd8的输出信号为第八与非门输出信号(net78信号),第八与非门电路nd8的输出端连接至第七与非门电路nd7的输入端。

88.需要说明的是,上述字母仅代表对信号的简写,并不构成对信号类型的具体限制。在实际中,也可以以其它方式对各信号进行描述,本公开实施例对此不作具体限定。

89.还需要说明的是,第一输入接口信号(inf信号)在被输入到cdl单元后,经过第一与非门电路nd1、第三与非门电路nd3以及第七与非门电路nd7,并与其它信号一起经过延迟处理后,得到第二输出接口信号(oute信号);或者,第一输入接口信号(inf信号)在被输入到cdl单元后,经过第一与非门电路nd1、第二与非门电路nd2、第四与非门电路nd4、第六与非门电路nd6以及第五与非门电路nd5,并与其它信号一起经过延迟处理后,得到第三输出接口信号(outo信号)。也就是说,对于第一输入接口信号(inf信号)而言,在cdl单元内部,会形成inf-oute和inf-outo两条信号线路,其中,inf-oute的信号线路会经过三个与非门电路对信号进行延迟处理,inf-outo的信号线路会经过五个与非门电路对信号进行延迟处理。那么,对于第二输出接口信号(oute信号)和第三输出接口信号(outo信号)而言,在输出时会相差两个与非门电路的延迟时间,也就是相差两个时钟周期。

90.这样,通过八个与非门电路的配合,实现对信号的延迟处理。但是,从图2中可以看

出,由于各与非门电路分布的无序性,以及线路的绕线布局等的影响,导致对于第二输出接口信号(oute信号)和第三输出接口信号(outo信号)而言,其输出延时难以保证为相差两个与非门电路的延迟时间;另外,与非门电路的输出信号在传递到下一个与非门电路时,信号所经过的路径长度可能会有所不同,而且整个电路的布局缺乏整洁,从而对信号之间的延时统一产生影响,不利于cdl单元和延迟电路的延迟工作。

91.而在延迟电路(如dll)设计中,由于每个延迟阶段都需要相同的时间延迟,因此具有相同时间延迟的版图设计非常重要。目前的版图设计,难以保证每个延迟阶段的时间延迟相同。因此,在此基础上,本公开实施例对cdl单元的具体排布进行设计,以改善在信号传输期间,延迟上的不统一,同时增加电路的集成度。

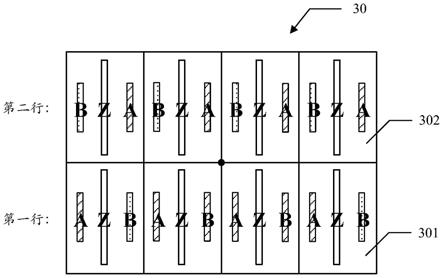

92.在本公开的一实施例中,参见图3,其示出了本公开实施例提供的一种延迟电路单元的版图30的组成结构示意图。如图3所示,该版图30包括多个版图单元,版图单元用于形成与非门电路,且版图单元呈阵列排布;其中,

93.在阵列的第一行中,顺序排布有若干个符合第一布局方式的版图单元301;

94.在阵列的第二行中,顺序排布有若干个符合第二布局方式的版图单元302;

95.其中,第一布局方式与第二布局方式不同,而且第一布局方式和第二布局方式使得第一行与第二行呈中心对称结构。

96.需要说明的是,图3所示为延迟电路中的一个延迟电路单元对应的版图结构,延迟电路由若干个延迟电路单元级联组成,延迟电路可以为dll中的粗延迟电路,也可以为其它类型的延迟电路,本公开实施例对此不作具体限定。

97.在图3所示的版图30中,包括多个版图单元,每个版图单元用于形成一个对应的与非门电路。其中,多个版图单元呈阵列排布,也就是说,在延迟电路单元中,多个版图单元形成的多个与非门电路呈阵列排布。

98.如图3所示,在由若干个版图单元组成的阵列中(由于版图单元用于形成与非门电路,因此,该阵列也可以称为由若干个与非门电路组成的阵列),至少包括第一行和第二行,由于第一行和第二行的版图单元的布局方式不同,将排布于第一行的版图单元记为版图单元301,将排布于第二行的版图单元记为版图单元302;其中,在第一行中,若干个版图单元301的布局方式符合第一布局方式;在第二行中,若干个版图单元302的布局方式符合第二布局方式,且第一布局方式和第二布局方式为不同的布局方式。

99.基于阵列两行的不同布局方式,使得阵列的第一行和第二行呈中心对称结构,其中,中心对称点即为版图30的几何中心,具体如图3中的黑色点所示。这样,使得延迟电路单元的版图整体排布紧促,还能够节省版图面积。

100.对于第一布局方式和第二布局方式,如图3所示,在一些实施例中,版图单元至少可以包括第一输入信号线a、第二输入信号线b和输出信号线z;其中,

101.在第一布局方式下,版图单元301的信号线沿从右至左方向的排布顺序均为:第二输入信号线b,输出信号线z,第一输入信号线a;

102.在第二布局方式中,版图单元302的信号线沿从右至左方向的排布顺序均为:第一输入信号线a,输出信号线z,第二输入信号线b。

103.需要说明的是,如图3所示,对于版图30中的每一个版图单元形成的与非门电路,版图单元均包括第一输入信号线a、第二输入信号线b以及输出信号线z,而且在从左向右或

者从右向左的方向,第一行的版图单元301和第二行的版图单元302中的三根信号线的排布顺序是相反的,形成了两行之间的中心对称结构。

104.也就是说,在图3中,主要示出的是版图单元形成的与非门电路对应的两个输入端(即第一输入信号线a和第二输入信号线b)、一个输出端(即输出信号线z)。

105.进一步地,对于版图30中形成的每一个与非门电路,参见图4,其示出了本公开实施例提供的一种与非门电路的电路结构示意图。如图4所示,在一些实施例中,与非门电路可以包括第一pmos管p1、第二pmos管p2、第一nmos管n1和第二nmos管n2。

106.需要说明的是,如图4所示,对于本公开实施例中的任意一个与非门电路,该与非门电路可以由两个p沟道金属氧化物半导体场效应管(p-type channel metal oxide semiconductor,pmos管)p1和p2,以及两个n沟道金属氧化物半导体场效应管(n-type channel metal oxide semiconductor,nmos管)n1和n2组成。其中,a表示第一输入信号线,b表示第二输入信号线,z表示输出信号线,两个p沟道mos管(即第一pmos管p1和第二pmos管p2)并联,两个n沟道mos管(即第一nmos管n1和第二nmos管n2)串联。

107.在一些实施例中,该版图30至少可以划分为第一金属层和第二金属层,第二金属层位于第一金属层上层;其中,

108.第一金属层,用于布局第一输入信号线、第二输入信号线、输出信号线以及第一层信号线;

109.第二金属层,用于布局第二层信号线;

110.其中,第一输入信号线、第二输入信号线、输出信号线以及第一层信号线均沿第一方向布线,第二层信号线沿第二方向布线,第一方向与第二方向的夹角为90度。

111.需要说明的是,对于本公开实施例提供的版图30,其至少可以划分为第一金属层(也称为metal 0)和第二金属层(也称为metal 1),且第二金属层位于第一金属层的上层。

112.其中,版图单元中的第一输入信号线、第二输入信号线以及输出信号线布局在第一金属层,第一金属层还布局有第一层信号线;第二金属层布局有第二层信号线。第一输入信号线、第二输入信号线、输出信号线以及第一层信号线是沿第一方向布线的,而第二层信号线是沿第二方向布线的,而且第一方向和第二方向的夹角为90度。

113.对于第一金属层,参见图5,其示出了本公开实施例提供的一种延迟电路单元的版图30的详细结构示意图。其中,图5中的(a)表示第一金属层的整体布线排布示意图;图5中的(b)表示在第一金属层的第一行,以第一布局方式排布的版图单元301对应的与非门电路中的信号线的布线排布示意图;图5中的(c)表示在第一金属层的第二行,以第二布局方式排布的版图单元302对应的与非门电路中的信号线的布线排布示意图。

114.如图5所示,在第一金属层的布线中,将除(b)和(c)包含的与非门电路的信号线之外的其它布线均称作第一层信号线。

115.对于第二金属层,参见图6,其示出了本公开实施例提供的另一种延迟电路单元的版图30的详细结构示意图,其示出的是第二金属层的整体布线排布示意图。如图6所示,其中,虚线框内部的金属布线表示第二层信号线,第二层信号线沿第二方向延伸。

116.需要说明的是,如图5和图6所示,在第一金属层中,第一层信号线和与非门电路的各信号线是沿第一方向延伸的;在第二金属层中,第二层信号线是沿第二方向延伸的,且第一方向和第二方向之间的夹角为90度。由于第二金属层位于第一金属层的上层,这样,第二

层信号线可以跨接在第一金属层上方,将第一金属层中不相邻的信号线进行连接,从而实现信号的传输。

117.进一步地,在一些实施例中,如图6所示,第二金属层还可以包括电源线606和接地线607;其中,

118.电源线606分别与第一pmos管和第二pmos管的源极连接;

119.接地线607与第一nmos管的源极连接;

120.第一输入信号线a分别与第二pmos管的栅极和第二nmos管的栅极连接;

121.第二输入信号线b分别与第一pmos管的栅极和第一nmos管的栅极连接;

122.输出信号线z分别与第一pmos管的漏极、第二pmos管的漏极以及第二nmos管的漏极连接。

123.需要说明的是,如图6所示,在第二金属层中,还包括有两个电源线606和两个接地线607,在电源线606和接地线607上均可以设置有连接点303b,每个连接点303b上均可以包括若干个接触点303c。例如,在图6中,每个连接点303b上均包括3个接触点303c,对于接触点的具体数量,本公开实施例不作具体限定。相应地,如图5所示,在第一金属层的信号线上设置有与第二金属层中对应位置和对应数量的连接点303b。这里,第一金属层中的连接点303b和第二金属层中的连接点303b之间的连接方式可以为通过接触插塞连接,其包括的接触点303c可以为接触孔。

124.具体来说,对于每一个与非门电路,电源线606可以分别与第一pmos管p1和第二pmos管p2的源极通过连接点303b进行连接;接地线607可以与第一nmos管n1的源极通过连接点303b进行连接。

125.还需要说明的是,该版图30还可以包括栅源层,用于提供与非门电路中的晶体管(包括nmos管和pmos管)的栅极和有源区。参见图7,其示出了本公开实施例提供的一种栅源层的版图结构示意图,如图7中的(a)所示,栅源层排布有多个晶体管的有源区和栅极,栅源层还可以包括第一隔离结构703和第二隔离结构704。其中,第一隔离结构703能够将第一行和第二行的与非门电路和晶体管进行隔离,避免相互串扰,第二隔离结构704可以将图中示出的与非门电路和晶体管与电路中的其它结构(例如相邻的延迟电路单元的版图)进行隔离,避免电路之间相互串扰造成的不良影响。其中,第一隔离结构703可以为n阱区,第二隔离结构704可以为p阱区。

126.在栅源层的第一行,从左至右依次排布有对应于四个以第一布局方式排布的与非门电路的有源区和栅极。图7中的(b)为对应于以第一布局方式排布的与非门电路的有源区和栅极。如图7中的(b)所示,有源区7022可以表示第一nmos管n1和第二nmos管n2的有源区,有源区7022可以为n型掺杂的有源区;有源区7021可以表示第一pmos管p1和第二pmos管p2的有源区,有源区7021可以为p型掺杂的有源区;栅极7011可以表示第一nmos管n1的栅极,栅极7012可以表示第二nmos管n2的栅极,栅极7013可以表示第一pmos管p1的栅极,栅极7014可以表示第二pmos管p2的栅极。

127.在每个栅极上,均可以设置有连接点303d。相应地,如图5所示,在第一金属层中,每个第一输入信号线a和每个第一输入信号线b上也均设置有对应位置和对应数量的连接点303d,从而通过连接点303d能够将各栅极和各输入信号线进行连接。

128.具体来说,对于版图单元形成的每一个与非门电路,第一输入信号线a分别与第二

pmos管p2的栅极和第二nmos管n2的栅极通过连接点303d进行连接;第二输入信号线b分别与第一pmos管p1的栅极和第一nmos管n1的栅极通过连接点303d进行连接。

129.参见图8,其示出了本公开实施例提供的一种版图单元的组成结构示意图。如图8所示,其示出的是版图30中的第一行的一个版图单元301的叠加连接的示意图,图8与图4中的与非门电路的电路结构示意图是对应的。这里,将栅源层、第一金属层和第二金属层依次叠加并按照对应位置的连接点进行连接,第一金属层位于栅源层的上层,第二金属层位于第一金属层的上层;第一输入信号线a的下端通过连接点303d与第二nmos管n2的栅极7012连接,第一输入信号线a的上端通过连接点303d与第二pmos管p2的栅极7014连接;第二输入信号线b的下端通过连接点303d与第一nmos管n1的栅极7011连接,第二输入信号线b的上端通过连接点303d与第一pmos管的栅极7013连接;输出信号线z分别与第一pmos管的漏极、第二pmos管的漏极以及第二n型晶体管的漏极连接(图中未示出);电源线606分别与第一pmos管的栅极7013和第二pmos管的栅极7014通过连接点303b连接;接地线607与第一nmos管的栅极7011通过连接点303b连接。

130.另外,如图7或者图8所示,在栅极7011和栅极7012的两侧,以及栅极7013和栅极7014的两侧,还包括两根冗余信号线(dummy),用于维持版图的对称整齐,并保证芯片的可制造性,提高工艺过程中的精度,避免刻蚀失败。

131.也就是说,在本公开实施例提供的延迟电路单元的版图中,从下层至上层依次可以包括栅源层,第一金属层和第二金属层。以一个与非门电路对应的一个版图单元为例,结合图4和图8所示,栅源层用于形成晶体管的栅极和有源区;第一金属层用于形成第一输入信号线a、第二输入信号线b和输出信号线z;第二金属层用于形成电源线和接地线。将栅源层、第一金属层和第二金属层叠加,并通过对应位置的连接点进行连接,形成与非门电路。

132.另外,图7中的(c)示出的是在版图30的第二行,以第二布局方式排布的版图单元302对应的与非门电路的栅极和有源区的排布示意图,其与图7中的(b)呈中心对称分布,两者的连接方式相同,这里不再赘述。

133.对于第一层信号线和第二层信号线,在一些实施例中,第一层信号线至少可以包括:第一信号线3021、第二信号线3022、第三信号线3023、第四信号线3024、第五信号线3025和第六信号线3026;

134.第二层信号线至少可以包括:第一输入接口信号线6011、第一输出接口信号线6012、第二输入接口信号线6021、第二输出接口信号线6022、第三输入接口信号线6031和第三输出接口信号线6032。

135.需要说明的是,参见图9,其示出了本公开实施例提供的一种延迟电路单元的版图30的局部放大示意图,其示出的是第一金属层的局部放大示意图,即图5下部的点划线框部分。

136.如图9所示,在第一金属层中,第一层信号线至少可以包括以下六种:第一信号线3021、第二信号线3022、第三信号线3023、第四信号线3024、第五信号线3025和第六信号线3026。

137.其中,第一信号线3021用于传输第一信号,第二信号线3022用于传输第二信号,第三信号线3023用于传输第三信号,第四信号线3024用于传输第四信号,第五信号线3025用于传输第五信号,第六信号线3026用于传输第六信号。第一信号、第二信号、第三信号、第四

信号、第五信号和第六信号为不同的信号。

138.这里,第一信号可以为前述的第四与非门输入信号(selo信号),第二信号可以为前述的第二与非门输入信号(infeno信号),第三信号可以为前述的第四与非门输出信号(net46信号),第四信号可以为前述的第三与非门输出信号(net37信号),第五信号可以为前述的第三与非门输入信号(sele信号),第六信号可以为前述的第一与非门输入信号(infene信号)。

139.其中,selo信号和sele信号对应的是两个不同相位的选择信号,infeno信号和infene信号对应的是输入时钟信号的两个使能信号,net37信号和net46信号对应的是延迟电路单元的内部节点信号。

140.还需要说明的是,在第二金属层中,第二层信号线至少可以包括第一输入接口信号线6011、第一输出接口信号线6012、第二输入接口信号线6021、第二输出接口信号线6022、第三输入接口信号线6031和第三输出接口信号线6032。

141.其中,第一输入接口信号线6011用于传输第一输入接口信号(inf信号),第一输出接口信号线6012用于传输第一输出接口信号(outf信号),第二输入接口信号线6021用于传输第二输入接口信号(ine信号),第二输出接口信号线6022用于传输第二输出接口信号(oute信号),第三输入接口信号线6031用于传输第三输入接口信号(ino信号),第三输出接口信号线6032用于传输第三输出接口信号(outo信号)。

142.在一些实施例中,第一层信号线可以排布于每一个版图单元的两侧;其中,

143.第一层信号线沿从右至左方向的排布顺序为:第一信号线3021、第二信号线3022、第三信号线3023、第四信号线3024、第五信号线3025和第六信号线3026。

144.需要说明的是,参见图10,其示出了本公开实施例提供的一种延迟电路单元的版图30的简化结构示意图,其可以表示第一金属层示出的阵列中的第一行的简化放大,其也可以用于表示第二行的简化放大。如图5、9和10所示,在每一个版图单元的左侧和右侧,均排布有一个第一层信号线,而且对于上下两个版图单元,左侧和右侧的第一层信号线为同一根。在第一金属层中,第一层信号线沿从右至左方向的排布顺序为第一信号线3021、第二信号线3022、第三信号线3023、第四信号线3024、第五信号线3025和第六信号线3026。

145.进一步地,在一些实施例中,第一层信号线还可以包括若干个冗余信号线3027,其中,

146.第一层信号线沿从右至左方向的排布顺序为:第一信号线3021、第二信号线3022、第三信号线3023、第四信号线3024、第五信号线3025、第六信号线3026和所述若干个冗余信号线3027。

147.需要说明的是,如图5、9和10所示,在第一金属层中,第一层信号线还可以包括若干个冗余信号线3027,其中,冗余信号线3027不用于传递信号。另外,参见图6,在接地线607中,按照从左至右的顺序,第一个和第三个连接点303b用于将冗余信号线3027与接地线进行连接。这里,仅示出两条冗余信号线3027和两个用于连接冗余信号线至接地线的连接点303b,在实际中,冗余信号线的数量可以根据工艺需要进行设定,本公开实施例不作具体限定。

148.冗余信号线3027可以保证版图整体的整齐排列,而且能够保证电路在制造过程中的可制造性,防止由于曝光过渡或不足而导致的蚀刻失败,并避免光刻过程中由于光的反

射与衍射对关键元器件物理图形的精度影响。

149.在一些实施例中,在第一金属层中,若干第一层信号线的宽度相同,而且每相邻两个信号线之间的间距相同。

150.需要说明的是,参见图11,其示出了本公开实施例提供的另一种延迟电路单元的版图30的局部放大示意图,其示出的是第一金属层的局部放大示意图,即图5上部的点划线框的部分。如图11所示,对于第一金属层中的信号线(包括第一层信号线和与非门电路的信号线),每个信号线的宽度均相同,而且任意两个相邻的信号线之间的间距均相同,在图11中,每个信号线的宽度与相邻两个信号线间距的和为a。

151.这样,在第一金属层中,各第一层金属线和与非门电路的信号线之间均保持相同的间距和信号线宽度,从而不仅有利于保持不同信号在传递过程中的延时统一,还能够保持电路整体布局的整齐,使得电路排布紧凑,节省版图面积。

152.在一些实施例中,第二层信号线还可以包括若干个中间连接线,且每一个中间连接线上设置有连接点;其中,

153.若干个中间连接线,用于将第一金属层中设置有连接点的信号线进行连接,以实现将目标信号传输至对应的版图单元与非门电路。

154.需要说明的是,如图5所示,在第一金属层中,每一个版图单元和第一层信号线上均设置有连接点303a;如图6所示,在第二金属层中,第二层信号线上也均设置有连接点303a。其中,将图6的虚线框中除前述第一输入接口信号线6011、第一输出接口信号线6012、第二输入接口信号线6021、第二输出接口信号线6022、第三输入接口信号线6031和第三输出接口信号线6032以外的第二层信号线称作中间连接线。

155.基于第一金属层和第二金属层的信号线上设置的连接点303a,可以将第一金属层中的信号线和第二金属层中的信号线连接起来,以实现信号的传输。

156.参见图12~14,其中,图12其示出了本公开实施例提供的再一种延迟电路单元的版图30的详细结构示意图;图13示出了本公开实施例提供的另一种延迟电路单元的版图30的简化结构示意图;图14示出了本公开实施例提供的再一种延迟电路单元的版图30简化结构示意图。

157.如图12所示,将第一金属层与第二金属层进行连接之后,第一金属层中的连接点303a与第二金属层中的连接点303a对应连接,从而将第一金属层的信号线和第二金属层的信号线连接起来。

158.另外,对于本公开实施例中涉及到的各连接点303a、303b、303d等,其可以为相同的连接方式或者不同的连接方式,实现不同的信号线之间的导电连接和信号传输。例如,连接方式可以均为通过接触插塞连接,相应的连接点可以为接触孔,从而能够通过接触插塞和接触孔将两个信号线进行连接。

159.也就是说,通过第二金属层中的信号线将第一金属层中的各信号线连接起来,从而实现了将目标信号传输至对应的与非门电路。其中,目标信号包括前述的第一信号、第二信号、第三信号、第四信号、第五信号和第六信号。

160.在一些实施例中,如图13所示,多个版图单元可以包括第一版图单元3011、第二版图单元3012、第三版图单元3013、第四版图单元3014、第五版图单元3015、第六版图单元3016、第七版图单元3017和第八版图单元3018,且在第一金属层呈2

×

4阵列排布;其中,

161.在阵列的第一行中,沿从右至左方向顺序排布第四版图单元3014、第二版图单元3012、第三版图单元3013和第一版图单元3011;其中,第四版图单元3014用于形成第一与非门电路nd1,第二版图单元3012用于形成第二与非门电路nd2,第三版图单元3013用于形成第三与非门电路nd3,第一版图单元3011用于形成第一与非门电路nd1;

162.在阵列的第二行中,沿从右至左方向顺序排布第八版图单元3018、第六版图单元3016、第七版图单元3017和第五版图单元3015;其中,第八版图单元3018用于形成第八与非门电路nd8,第六版图单元3016用于形成第六与非门电路nd6,第七版图单元3017用于形成第七与非门电路nd7,第五版图单元3015用于形成第五与非门电路nd5。

163.需要说明的是,如图13所示,在本公开实施例提供的版图30中,可以形成八个版图单元,且在第一金属层中,这八个版图单元呈2

×

4阵列排布。其中,以第一布局方式排布于第一行的版图单元301,从右至左依次为:第四版图单元3014、第二版图单元3012、第三版图单元3013和第一版图单元3011;以第二布局方式排布于第二行的版图单元302,从右至左依次为:第八版图单元3018、第六版图单元3016、第七版图单元3017和第五版图单元3015。

164.需要说明的是,结合参考图2,第一版图单元3011用于形成第一与非门电路nd1,第二版图单元3012用于形成第二与非门电路nd2,第三版图单元3013用于形成第三与非门电路nd3,第四版图单元3014用于形成第四与非门电路nd4,第五版图单元3015用于形成第五与非门电路nd5,第六版图单元3016用于形成第六与非门电路nd6,第七版图单元3017用于形成第七与非门电路nd7,第八版图单元3018用于形成第八与非门电路nd8。

165.进一步地,在一些实施例中,如图14所示,在第一版图单元3011和第五版图单元3015的左侧和右侧均排布冗余信号线3027;

166.在第三版图单元3013和第七版图单元3017的左侧和右侧依次排布第六信号线3026和第五信号线3025;

167.在第二版图单元3012和第六版图单元3016的左侧和右侧依次排布第四信号线3024和第三信号线3023;

168.在第四版图单元3014和第八版图单元3018的左侧和右侧依次排布第二信号线3022和第一信号线3021。

169.需要说明的是,在第一金属层中,第一层金属线呈对称结构分布于各版图单元的两侧,从而使得版图排布整齐,有利于信号的传输统一。

170.在一些实施例中,若干个中间连接线可以划分为第一组中间连接线和第二组中间连接线;其中,

171.在第二金属层中,对应于第四版图单元3014、第二版图单元3012、第三版图单元3013和第一版图单元3011的位置,排列有第一组中间连接线以及第一输入接口信号线6011和第一输出接口信号线6012;

172.在第二金属层中,对应于第八版图单元3018、第六版图单元3016、第七版图单元3017和第五版图单元3015的位置,排列有第二组中间连接线以及第二输入接口信号线6021、第二输出接口信号线6022、第三输入接口信号线6031和第三输出接口信号线6033。

173.需要说明的是,如图12和图14所示,在第四版图单元3014、第二版图单元3012、第三版图单元3013和第一版图单元3011对应位置的第二金属层中,排列有第一组中间连接线和第一输入接口信号线6011和第一输出接口信号线6012;其中,第一组中间连接线可以包

括第二信号转接线6041,第三信号转接线一6042,第四信号转接线一6043,第一与非门输出信号转接线6044和第六信号转接线6045。

174.在第一组中间连接线中,第二信号转接线6041用于传输第二信号,第三信号转接线6042用于传输第四与非门电路nd4的输出信号,其中,第四与非门电路nd4的输出信号即第三信号;第四信号转接线6043用于传输第三与非门电路nd3的输出信号,其中,第三与非门电路nd3的输出信号即第四信号;第一与非门输出信号转接线6044用于传输第一与非门电路nd1的输出信号,第六信号转接线6045用于传输第六信号。

175.还需要说明的是,如图12所示,由于第三信号线3023传输的第三信号是第四与非门电路nd4的输出信号,第四信号线3024传输的是第三与非门电路nd3的输出信号。即第三信号线3023和第四信号线3024传输的是版图30内部形成的与非门电路所产生的信号,而非是来自版图30外部的信号,因此第三信号线3023和第四信号线3024在图中较短,即无需与图中未示出的外部线路进行连接。

176.还需要说明的是,如图12所示,在第八版图单元3018、第六版图单元3016、第七版图单元3017和第五版图单元3015对应位置的第二金属层中,排列有第二组中间连接线、第二输入接口信号线6021、第二输出接口信号线6022、第三输入接口信号线6031和第三输出接口信号线6032;其中,第二组中间连接线可以包括第八与非门输出信号转接线6051,第三信号转接线6052,第六与非门输出信号转接线6053和第四信号转接线6054。

177.在第二组中间连接线中,第八与非门输出信号转接线6051用于传输第八与非门电路nd8的输出信号;第三信号转接线6052用于传输第三信号线3023传输的第三信号;第六与非门输出信号转接线6053用于传输第六与非门电路nd6的输出信号;第四信号转接线6054用于传输第四信号线3024传输的第四信号。

178.这样,通过第一组中间连接线和第二组中间连接线,实现了将第一金属层的各信号进行转接传输。

179.还需要说明的是,对于图5~14中,未进行具体描述的信号线,其为延迟电路单元的版图中的其它信号线,用于实现电路的其它功能,对于其具体功能与本领域技术人员的常规理解相同,这里不作详细描述。

180.在一些实施例中,如图12所示,第一组中间连接线,用于将第四版图单元3014、第二版图单元3012、第三版图单元3013和第一版图单元3011中的部分信号线在第一金属层对应连接;

181.第二组中间连接线,用于将第八版图单元3018、第六版图单元3016、第七版图单元3017和第五版图单元3015中的部分信号线在第一金属层对应连接。

182.需要说明的是,如图12所示,对于第一组中间连接线而言,其与版图单元的具体连接方式可以为:第二信号转接线6041的两个连接点分别与第二信号线3022的连接点以及第二版图单元3012的第二输入信号线的连接点进行连接,从而第二信号可以经由第二信号线3022和第二信号转接线6041进入第二与非门电路nd2;第三信号转接线6042的两个连接点分别与第四版图单元3014的输出信号线的连接点以及第三信号线3023的连接点进行连接,从而第三信号可以经由第三信号转接线6042和第三信号线3023进行传输;第四信号转接线6043的两个连接点分别与第三版图单元3014的输出信号线的连接点以及第四信号线3024的连接点进行连接,从而第四信号可以经由第四信号转接线6043和第四信号线3024进行传

输;第一与非门输出信号转接线6044的三个连接点分别第一版图单元3011的输出信号线的连接点、第三版图单元3013的第一输入信号线的连接点以及第二版图单元3012的第一输入信号线的连接点进行连接,从而将第一与非门电路nd1的输出信号传输至第三与非门电路nd3和第二与非门电路nd2。

183.其中,其中第一与非门电路nd1的输出信号可以为前述的第一与非门输出信号net12。

184.另外,结合参照图5,对于第一信号线3021传输的第一信号以及第五信号线3025传输的第五信号,由于第一信号是被传输到第四版图单元3014的第二输入信号线,而且在第一金属层中,第四版图单元3014的第二输入信号线与第一信号线3021是相邻的;因此,为了布线的简洁与便利,这时候可以在第一金属层设置沿第二方向延伸的第一邻接信号线3031,通过第一邻接信号线3031将第一信号线3021和第四版图单元3014的第二输入信号线进行连接,从而将第一信号传输至第四与非门电路nd4。

185.同理,由于第五信号是被传输到第三与非门电路3013的第二输入信号线,而且在第一金属层中,第三版图单元3013的第二输入信号线与第五信号线3025是相邻的;因此,为了布线的简洁与便利,这时候可以在第一金属层设置沿第二方向延伸的第二邻接信号线3032,通过第二邻接信号线3032将第五信号线3025和第三版图单元3013的第二输入信号线进行连接,从而将第五信号传输至第三与非门电路nd3。

186.也就是说,对于第一金属层中,相邻两条信号线之间的信号传输,无需通过第二金属层中的中间连接线进行连接传输,而是可以直接在第一金属层设置邻接连接线实现。从而不仅能够使得整体线路布局简洁便利,易于加工,而且还能够避免线路之间的串扰。

187.还需要说明的是,如图12所示,对于第二组中间连接线而言,其与各版图单元的具体连接方式可以为:第八与非门输出信号转接线6051的两个连接点分别与第八版图单元3018的输出信号线的连接点和第七版图单元3017的第一输入信号线的连接点进行连接,从而将第八与非门电路nd8的输出信号传输至第七与非门电路nd7;第三信号转接线6052的两个连接点分别连接第三信号线3023的连接点以及第六版图单元3016的第二信号输出端,从而经过第三信号线3023和第三信号转接线6052将第三信号传输至第六与非门电路nd6;第六与非门输出信号转接线6053的两个连接点分别与第六版图单元3016的输出信号线的连接点和第五版图单元3015的第二输出信号线的连接点进行连接,从而将第六与非门电路nd6的输出信号传输至第五与非门电路nd5;第四信号转接线6054的两个连接点分别与第四信号线3024的连接点和第七版图单元3017的第二输入信号线进行连接,从而经过第四信号线3024和第四信号转接线6054将第四信号传输至第七与非门电路nd7。

188.其中,第八与非门电路nd8的输出信号可以为前述的第八与非门输出信号net78,第六与非门电路nd6的输出信号可以为前述的第六与非门输出信号net56。

189.这样,基于各连接点将第一金属层和第二金属层的信号线对应连接,从而实现信号的传输。

190.也就是说,对于版图30中的每一个版图单元形成的与非门电路,如图12所示,对于第一版图单元3011,其第一输入信号线,用于接收第一输入接口信号线6011传输的第一输入接口信号(inf信号);其第二输入信号线,用于接收经由第六信号线3026和第六信号转接线6045传输的第六信号;其输出信号线,用于输出第一与非门电路nd1的输出信号。

191.对于第三版图单元3013,其第一输入信号线,用于接收经由第一与非门输出信号转接线6044传输的第一与非门电路nd1的输出信号;其第二输入信号线,用于接收经由第五信号线3025和第二邻接信号线3032传输的第五信号;其输出信号线,用于输出第四信号;且第二邻接信号线3032布局于第一金属层。

192.对于第二版图单元3012,其第一输入信号线,用于接收经由第一与非门输出信号转接线6044传输的第一与非门电路nd1的输出信号;其第二输入信号线,用于接收经由第二信号线3022和第二信号转接线6041传输的第二信号;其输出信号线,用于输出第一输出接口信号(outf信号)。

193.对于第四版图单元3014,其第一输入信号线,用于接收经由第一输出接口信号线6012传输的第一输出接口信号(outf信号),且第一输出接口信号(outf信号)为第二与非门电路nd2的输出信号;其第二输入信号线,用于接收经由第一信号线3021和第一邻接信号线3031传输的第一信号;其输出信号线,用于输出第三信号;其中,第一邻接信号线3031布局于第一金属层。

194.对于第八版图单元3018,其第一输入信号线,用于接收第三输入接口信号线6031传输的第三输入接口信号(ine信号);其第二输入信号线与电源端vdd连接,用于接收电源信号(vdd信号);其输出信号线,用于输出第八与非门电路nd8的输出信号。

195.对于第六版图单元3016,其第一输入信号线,用于接收第二输入接口信号线6021传输的第二输入接口信号(ine信号);其第二输入信号线,用于接收经由第三信号转接线6042、第三信号线以及第三信号转接线6052传输的第三信号;其输出信号线,用于输出第六与非门电路nd6的输出信号。

196.对于第七版图单元3017,其第一输入信号线,用于接收第八与非门输出信号转接线6051传输的第八与非门电路nd8的输出信号;其第二输入信号线,用于接收经由第四信号转接线6043、第四信号线3024和第四信号转接线6054传输的第四信号;其输出信号线,用于输出第一输出接口信号(oute信号)。

197.对于第五版图单元3015,其第一输入信号线,用于接收第六与非门输出信号转接线6053传输的第六与非门输出信号;其第二输入信号线,与电源端vdd连接,用于接收电源信号(vdd信号);其输出信号线,用于输出第三输出接口信号(outo信号)。

198.这样,通过第一金属层和第二金属层中的信号线将第一金属层和第二金属层连接起来,从而能够将各输入信号传输进该延迟电路单元的与非门电路的第一输入信号线或者第二输入信号线,以及将各与非门电路的输出信号传递至其它与非门电路,或者直接进行输出。整个线路布局紧凑,集成度高,而且简单易于加工。

199.本公开实施例提供了一种延迟电路单元的版图,该版图包括多个版图单元,版图单元用于形成与非门电路,且版图单元呈阵列排布;其中,在阵列的第一行中,顺序排布有若干个符合第一布局方式的版图单元;在阵列的第二行中,顺序排布有若干个符合第二布局方式的版图单元;其中,第一布局方式与第二布局方式不同,而且第一布局方式和第二布局方式使得第一行与第二行呈中心对称结构。这样,不仅有利于实现不同相位信号之间的延时一致性,而且延迟电路单元的版图整体排布紧促,还能够节省版图面积。

200.本公开的另一实施例中,参见图15,其示出了本公开实施例提供的一种延迟电路的版图结构示意图,延迟电路可以包括前述的第一金属层和第二金属层,图15示出的是第

一金属层的整体排布示意图。该延迟电路包括n个延迟电路单元,每一个延迟电路单元对应于前述实施例所述的版图30。如图11所示,该延迟电路的版图包括若干个前述的延迟电路单元的版图30。其中,n为大于零的整数。

201.其中,延迟电路例如可以为延迟锁相环电路。

202.在一些实施例中,延迟电路的版图是由n个延迟电路单元的版图级联组成的;其中,

203.第一版图输入的第一输入接口信号为第二版图输出的第一输出接口信号;

204.第二版图输入的第二输入接口信号为第一版图输出的第二输出接口信号;

205.第二版图输入的第三输入接口信号为第一版图输出的第三输出接口信号;

206.其中,第一版图和所述第二版图表示延迟电路的版图中,两个相邻的延迟电路单元的版图。

207.需要说明的是,参见图16,其示出了本公开实施例提供的另一种延迟电路的版图结构示意图,其示出的是第二金属层的整体排布示意图。如图16所示,对于该延迟电路,每个延迟电路单元(cdl单元)的第一输入接口信号(inf信号)、第一输出接口信号(outf信号)、第二输入接口信号(ine信号)、第二输出接口信号(oute信号)、第三输入接口信号(ino信号)和第三输出接口信号(outo信号)均通过第二层信号线进行输入输出,而且每个cdl单元都保持相同的信号线布局和间距,从而能够实现信号延迟的统一。

208.还需要说明的是,如图16所示,以左起第一个cdl单元为第二版图,左起第二个cdl单元为第一版图为例;第一版图输入的第一输入接口信号(inf信号)为第二版图输出的第一输出接口信号(outf信号);第二版图输入的第二输入接口信号(ine信号)为第一版图输出的第二输出接口信号(oute信号);第二版图输入的第三输入接口信号(ino信号)为第一版图输出的第三输出接口信号(outo信号);通过这种信号传输方式,n个延迟电路单元的版图30之间形成级联,组成延迟电路的版图。

209.对于该延迟电路的版图而言,由于其由n个版图30级联组成,从而不仅能够实现版图30内部信号传输的延时统一,还能够实现n个版图30之间的延时统一,使得一整条延迟链上所有的信号长度在版图布局上实现一致性。

210.本公开的再一实施例中,参见图17,其示出了本公开实施例提供的一种半导体存储器130的组成结构示意图,如图17所示,该半导体存储器130包括前述实施例任一项所述的延迟电路的版图对应的延迟电路。

211.其中,半导体存储器可以包括动态随机存取存储器(dynamic random access memory,dram)、静态随机存取存储器(static random-access memory,sram)、磁性随机存储存储器(magnetic random access memory,mram)等等,本公开实施例对此不作具体限定。本公开实施例对此不作具体限定。对于半导体存储器130而言,由于半导体存储器可以包括前述的延迟电路的版图对应的延迟电路,从而不仅能够实现延迟电路单元的版图内部信号传输的延时统一,还能够实现n个延迟电路单元的版图之间的延时统一。

212.以上所述,仅为本公开的较佳实施例而已,并非用于限定本公开的保护范围。

213.需要说明的是,在本公开中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者装置不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者装置所固

有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者装置中还存在另外的相同要素。

214.上述本公开实施例序号仅仅为了描述,不代表实施例的优劣。

215.本公开所提供的几个方法实施例中所揭露的方法,在不冲突的情况下可以任意组合,得到新的方法实施例。

216.本公开所提供的几个产品实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的产品实施例。

217.本公开所提供的几个方法或设备实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的方法实施例或设备实施例。

218.以上所述,仅为本公开的具体实施方式,但本公开的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本公开揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本公开的保护范围之内。因此,本公开的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1