一种芯片布线方法、芯片布线装置、电子设备及存储介质与流程

1.本发明属于版图布线领域,具体涉及一种芯片布线方法、芯片布线装置、电子设备及存储介质。

背景技术:

2.随着半导体技术的发展,为了解决高昂的成本问题,对芯片的良率要求越来越高。对于晶圆制造工厂(foundry)来说,由于芯片的工艺制造过程复杂,制造过程中的缺陷(defect)是无法完全避免的。现如今,大部分晶圆制造工厂foundry可控制的缺陷defect尺寸会在几十纳米到十几微米之间,若缺陷defect在制造过程中落在晶圆wafer上,极易造成芯片内部走线短路和开路,造成芯片失效。因此,对于超大规模的深亚微米集成电路制造来说,缺陷defect是影响良率的重要因素。

3.缺陷defect通常是指晶圆wafer上存在的有形污染或者不完美,通常是由以下几种因素造成:

4.1.晶圆wafer上的物理异性(如:微尘,工艺残留物,不正常反应生成物)。

5.2.化学性污染(如:残留化学药品,有机溶剂)。

6.3.图案缺陷(如:显影(photo)或光刻(etch)造成的异常成像,机械性刮伤变形,厚度不均匀造成的颜色异常)。

7.4.晶圆wafer本身或制造过程中引起的晶格缺陷。

8.版图缺陷defect的存在当前是业界无法避免的问题,尤其对于超大规模芯片而言,致命缺陷(killer defect)对良率的影响会被放大。因此为了提高芯片的良率,就需要同时从设计角度考虑,采用特殊的设计方法,降低生产过程中由缺陷defect引起失效的概率,提升芯片生产良率。

9.现有技术中,降低大面积芯片的缺陷defect引起失效概率通常是依靠晶圆制造工厂foundry对制造工艺流程进行控制,通过各类传感器在制造过程中捕捉,尽量减少制造过程中的致命缺陷killer defect的数量。而为了满足芯片的性能、功耗、面积等要求,设计角度是不会对缺陷defect做预防的,因此缺陷defect失效的概率仍然不可控。

技术实现要素:

10.为了解决现有技术无法很好控制芯片缺陷引起芯片失效概率高的技术问题,本发明提供一种芯片布线方法、芯片布线装置、电子设备及存储介质。本发明通过后端物理实现的方法来减少缺陷defect落在芯片走线上或是走线之间引起芯片失效的概率。

11.本发明的技术解决方案为:

12.一种芯片布线方法,包括以下步骤:

13.基于初始布线状态报告中走线的布线参数,调整相邻走线之间的布线间距,生成预测布线状态报告;所述布线参数包括布线密度、走线类型和对应的经验缺陷尺寸分布中至少一种;

14.基于所述预测布线状态报告对芯片进行布线设计。

15.进一步限定,基于初始布线状态报告中走线的布线参数调整相邻走线之间的布线间距的步骤,包括:

16.基于初始布线状态报告中走线的布线参数,调整预定区域内相邻走线之间的布线间距;所述预定区域基于布线密度和经验缺陷尺寸确定。

17.进一步限定,

18.所述调整相邻走线之间的布线间距包括:扩大关联走线之间的布线间距和/或缩小非关联走线之间的布线间距,

19.所述关联走线包括导通后相互影响的走线;

20.所述非关联走线包括导通后不会相互影响的走线。

21.进一步限定,所述基于初始布线状态报告中走线的布线参数,调整预定区域内相邻走线之间的布线间距的步骤,包括:

22.基于所述布线密度将所述预定区域分为第一预定区域和第二预定区域,所述第一预定区域的布线密度大于所述第二区域的布线密度;

23.基于所述第一预定区域的布线密度、走线类型和对应的经验缺陷尺寸分布调整所述第一预定区域内相邻走线的布线间距;以及基于所述第二预定区域的布线密度、走线类型和对应的经验缺陷尺寸分布调整所述第二预定区域内相邻走线的布线间距。

24.进一步限定,所述相邻走线为两个相邻的信号线,则将相邻的两个信号线的布线间距扩大1.5倍-2倍。

25.进一步限定,所述相邻走线为相邻的电源线和地线,调整电源线与地线的之间的距离大于经验缺陷尺寸分布区间中占比最多的区间最大端值。

26.进一步限定,所述调整预定区域内相邻走线之间的布线间距包括:

27.基于所述预定区域的总面积、所述预定区域的布线密度、所述预定区域的走线程度以及所述预定区域的布线数量确定所述预定区域内相邻走线之间的布线间距。

28.一种芯片布线装置,包括:

29.预测布线状态报告生成模块:获取初始布线报告中走线的布线参数,调整相邻走线之间的布线间距,生成预测布线状态报告;所述布线参数包括布线密度、走线类型和对应的经验缺陷尺寸分布中至少一种;

30.以及布线设计模块:基于预测所述布线状态报告对芯片进行布线设计。

31.一种电子设备,包括相互耦接的处理器以及存储器,其中,

32.所述存储器:用于储存实现上述的芯片布线方法的程序指令;

33.所述处理器:用于执行所述存储器存储的所述程序指令。

34.一种计算机可读存储介质,存储有程序文件,所述程序文件被执行实现上述的芯片布线方法。

35.本发明所具有的有益效果:

36.1、本发明通过获取布线状态报告,依据在芯片布局布线阶段的布线拥挤程度(congestion)的信息(即布线密度),调整相邻走线之间的布线间距,降低缺陷落于信号线上的概率,减少芯片信号短路或开路造成的功能失效问题。

37.2、基于布线密度将预定区域分为第一预定区域和第二预定区域,第一预定区域的

布线密度大于第二区域的布线密度;将整个芯片的布线的可调整区域划分为第一预定区域和第二预定区域,并不同程度的拥挤类型(布线密度),调整布线方法,便于依据不同的布线密度有针对性的进行调整布线。

38.3、本发明提供的一种芯片布线方法,在版图设计时,考虑缺陷defect的影响,适当调整走线的宽度、间距等增加,降低缺陷defect落于电源/地线之间的概率,有效预防缺陷引起的芯片失效。

附图说明

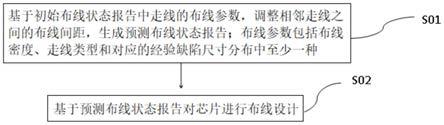

39.图1为本发明一种芯片布线方法实施流程图;

40.图2为不同布线拥挤程度布线的区分示意图;

41.图3为全芯片布线拥挤类型区域划分示意图;

42.图4为增加布线间距前后的缺陷优化效果展示图一;

43.图5为增加布线间距前后的缺陷优化效果展示图二;

44.图6为增加电源网络间距前后的缺陷优化效果展示图;

45.图7为本发明芯片布线装置的结构示意图;

46.图8为本发明一种电子设备的结构示意图;

47.图9为本发明一种计算机可读存储介质的结构示意图;

48.其中,1-预测布线状态报告生成模块,2-布线设计模块。

具体实施方式

49.以下结合附图对本发明的优选实施例进行说明,应当理解,此处所描述的优选实施例仅用于说明和解释本发明,并不用于限定本发明。本发明给出了一种芯片布线方法,由后端物理实现的方法来减少缺陷defect落在芯片走线上或是走线之间引起芯片失效的概率。

50.如图1所示,为本发明一种芯片布线方法的实施流程图,具体而言该方法包括:

51.步骤s01:基于初始布线状态报告中走线的布线参数,调整相邻走线之间的布线间距,生成预测布线状态报告;布线参数包括布线密度、走线类型以及经验缺陷尺寸分布中至少一种。

52.其中,布线密度为单位面积上走线总面积占比,如图2所示,布线不拥挤的布线密度小,布线拥挤的布线密度大;走线类型一般有信号线、电源线、地线等,在实施例中,走线类型还包括走线宽度。具体的,在生成预测布线状态报告时,还应考虑走线宽度,基于走线宽度确定走线之间的间距。其中,经验缺陷尺寸分布是指检测分析以往成型芯片所存在的缺陷数据,分析统计后得到经验缺陷尺寸的分布区间及区间占比。

53.步骤s02:基于所生成的预测布线状态报告对芯片进行布线设计。

54.具体的,基于初始布线状态报告中走线的布线参数调整相邻走线之间的布线间距的步骤为:基于初始布线状态报告中走线的布线参数,调整预定区域内相邻走线之间的布线间距;其中,预定区域是基于布线密度和经验缺陷尺寸确定,预定区域也指芯片上布线参数的可调整区域。可以理解的,预定区域指的是容易发生失效现象的区域,也即布线拥挤区域。本实施例中,对布线拥挤区域内的相邻走线之间的布线间距进行调整,可以减少拥挤区

域中相邻走线之间失效的概率。依据布线状态报告中走线的布线参数,确定布线拥挤程度信息(即布线密度),调整相邻走线之间的布线间距,能够很好地降低缺陷落于信号线上的概率,减少芯片信号、电源短路或开路造成的功能失效问题;本发明主要通过后端物理实现的方法来减少缺陷defect落在芯片走线上或是走线之间引起芯片失效的概率,提高芯片的良率。

55.需要说明的是,芯片中还存在不可调整区域,该区域的布线密度非常大,布线没有调整空间,对于该区域,将其设置为不可调整区域。具体的,布线密度大于等于第一密度的区域为非预定区域,即不可调整区域,因为布线太密,没有调整空间;布线密度小于第一密度的区域为可调整区域。一般第一密度取90%,当然根据实际需要也可以取其他的密度值。本技术所提及的调整布线间距及走线宽度,都是基于有余量面积,具有调整空间的区域。

56.在一实施例中,在调整相邻走线之间的布线间距时,可以扩大关联走线之间的布线间距和/或缩小非关联走线之间的布线间距,关联走线包括导通后相互影响的电源线和/或信号线;非关联走线包括导通后不会相互影响的电源线和/或信号线。具体如图6所示,图6中左边的示意图表示电源线vdd和地线vss的布线示意图,其中,关联的电源线vdd和地线vss之间间距小,在有灰尘(黑色部分)落入电源线vdd和地线vss中间时,会导致短路。为解决该问题,增大关联的电源线vdd和地线vss之间间距,为了不影响芯片的面积,在增大关联的电源线vdd和地线vss之间间距的同时,减小了非关联的电源线vdd和地线vss之间间距,在图6中,a和c均为电源线vdd,bd均为地线vss,其中,a和b以及c和d均为关联的电源线vdd和地线vss,b和c为非关联的电源线vdd和地线vss。

57.根据预定区域的布线密度、走线类型和对应的经验缺陷尺寸分布,生成适应的布线间距调整规则;调整规则是:布线间距变大;增加缺陷掉在布线之间空隙的概率,或是提高缺陷未完全覆盖走线的概率。

58.具体的调整规则:就是使得布线间距大于经验缺陷尺寸分布区间中占比最多的区间最大端值。例如,若经验缺陷尺寸呈正太分布,那么经验缺陷尺寸分布区间中占比最多的区间就是正态分布中凸起的那一段所对应的尺寸区间,取该区间的最大值,是为了保证大部分的缺陷都不会引起芯片失效。缺陷会落在线与线之间,也会落在单根线上。若是线与线之间的间距大于区间的最大值,这样就可增加缺陷落在走线之间空隙的概率,进而提升芯片的良率。同样增加走线的宽度,即便是缺陷落在走线上,但因为缺陷的尺寸小于走线宽度,还是能够保证走线的基本性能。布线间距大于经验缺陷尺寸分布区间中占比最多的区间最大端值时,即使有灰尘落在两线之间也不会将相连的两根线短路。

59.按照生成的调整规则对区域内布线间距进行调整:

60.具体的,布局布线工具将根据生成的调整规则在对应区域内将布线的间隔扩大,使总体的单位布线密度降低。在生产过程中晶圆wafer上出现缺陷defect,导致信号线短路或者开路的概率会极大降低,从而整体降低了芯片因缺陷defect引起的功能失效概率。

61.具体的,所述调整预定区域内相邻走线之间的布线间距包括:基于预定区域的总面积、预定区域的布线密度、预定区域的走线程度以及预定区域的布线数量确定所述预定区域内相邻走线之间的布线间距。在一具体实施例中,定义可调整区域的总面积为s,该区域布线密度为k,走线线长为l,原始布线间距为d,调整规则为,调整后的布线间距d=s*(1-k)/(n-1)*l。其中n为该区域内的布线数量。

62.具体的,为了能够有针对性的生成调整规则,方便布线调整,提升芯片的失效概率,还包括:对可调整区域进一步区域划分;布线密度大于第二密度小于第一密度划分为第一预定区域;布线密度小于等于第二密度划分为第二预定区域,即第一预定区域的布线密度大于所述第二区域的布线密度;基于第一预定区域的布线密度、走线类型和对应的经验缺陷尺寸分布调整第一预定区域内相邻走线的布线间距;以及基于第二预定区域的布线密度、走线类型和对应的经验缺陷尺寸分布调整第二预定区域内相邻走线的布线间距。优选的,第一密度为90%,第二密度为50%。在第二区域内时,也就是布线密度小于等于50%,表明在该区域,有大于等于区域总面积一半的空隙面积,针对此区域的调整规为:布线间距扩大1.5倍-2倍或走线宽度扩大1.5倍-2倍。

63.实施例1:依据在芯片布局布线阶段的布线拥挤程度(congestion,即布线密度)的信息,将整个芯片划分为多个区域(region),依据各个区域的布线拥挤程度(congestion)状态,分别调整不同布线密度区域中的布线间隔(pitch),使得芯片上布线密度较小区域的布线间距增大,从而使所有芯片信号线(包括数字信号、模拟信号线等)在芯片上的平均布线间隔变大,从而增加缺陷defect落于走线之间空隙的概率,减小其落于信号线上的概率。

64.如图3所示,对于宽度较窄的信号线而言,依据在芯片布局布线阶段布线拥挤程度(congestion)的信息,将整个芯片的布线信息划为不同区域,如图中绿色、蓝色区域分别代表的两种区域:绿色为布线不拥挤区域,蓝色为布线较拥挤区域。

65.针对两种区域,生成不同的布线规则(non-default routing rule),从而进行局部的布线调整,分别对不同区域的信号线设置不同的布线间隔,如绿色区域使用最大的布线间隔进行调整,调整前后的对比图如图4所示;蓝色区域使用较大一些的布线间隔进行调整,调整前后的对对比图如图5所示。

66.对蓝色和绿色区域的布线设定布线规则进行约束,布局布线工具将根据设定的规则在该区域内将布线的间隔扩大,使总体的单位布线密度降低,若在生产过程中晶圆wafer上出现缺陷defect,导致信号线短路或者开路的概率会极大降低,从而整体降低了芯片因defect引起的功能失效概率。

67.调整之后,当缺陷defect出现于蓝色和绿色区域时,由于增大了布线间隔pitch,缺陷defect落在信号线上的概率会降低,从而使整个芯片由缺陷defect导致的功能失效概率会降低。

68.实施例2:对于宽度较大的芯片电源网络线(power mesh)来说,缺陷defect造成的短路和开路更为致命。对版图实现来说,从布局规划时就需要考虑缺陷defect造成的芯片失效。由于电源线本身是成对出现的,因此在做电源网络规划时,通过增加电源线之间相对间距(spacing),可有效降低缺陷defect落在电源线之间的概率,降低失效风险。

69.传统的电源/地线的布线方法,为减小电源/地之间的耦合电容,电源线/地线之间会采用最小间距,以保证电源网络的强壮。但若缺陷defect落于电源线与地线之间,极易导致供电网络短路,局部供电电流增大,烧毁晶体管,致使芯片失效。

70.根据工厂提供的经验缺陷尺寸分布以及布线密度,制定电源/地线之间的间隔spacing,满足设计要求的同时,适当增加电源/地线之间的间隔spacing,可以有效降低defect落于电源地线之间的概率,防范短路问题。如图6所示,调整前后的效果示意图。采用此方法,适当增加电源/地线之间的布线spacing,即便生产过程中有缺陷defect出现,降低

缺陷defect落于电源/地线之间的概率,防止电源网络短路导致的芯片失效,能够有效提高芯片的良率。

71.本发明还提供一种芯片布线装置,具体如图7所示,芯片布线装置包括:预测布线状态报告生成模块1和布线设计模块2;

72.预测布线状态报告生成模块1:用于获取初始布线报告中走线的布线参数,调整相邻走线之间的布线间距,生成预测布线状态报告;其中,布线参数包括布线密度、走线类型和对应的经验缺陷尺寸分布中至少一种;

73.布线设计模块2:基于预测布线状态报告对芯片进行布线设计。

74.参见图8,本发明一种电子设备,其包括相互耦接的处理器以及存储器,其中,存储器:用于储存实现上述的芯片布线方法的程序指令;处理器:用于执行存储器存储的程序指令。

75.参见图9,本发明一种计算机可读存储介质,其上存储有程序文件,程序文件被执行实现上述的芯片布线方法。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1