数据通路测试方法、装置、设备、存储介质及程序产品与流程

本技术涉及人工智能与芯片技术,尤其涉及一种存储器的数据通路测试方法、装置、电子设备、计算机可读存储介质及计算机程序产品。

背景技术:

1、人工智能(ai,artificial intelligence)是利用数字计算机或者数字计算机控制的机器模拟、延伸和扩展人的智能,感知环境、获取知识并使用知识获得最佳结果的理论、方法和技术及应用系统。

2、高带宽内存是一种标准化的堆栈存储技术,可为堆栈内部以及存储与逻辑元件之间的数据提供高带宽通道。高带宽内存封装将存储裸片堆叠起来,从而可以实现较高的读写速度,通常需要对高带宽内存存储器的读写数据通路进行测试,以保证在高速读写数据的过程中数据的正确性。

3、相关技术中会每次数据读写之后均会进行一次校验,即相当于需要对全量数据进行校对,且需要进行多次校对,导致测试效率较低,浪费硬件处理资源。

技术实现思路

1、本技术实施例提供一种存储器的数据通路测试方法、装置、电子设备、计算机可读存储介质及计算机程序产品,能够提高存储器的数据通路测试效率。

2、本技术实施例的技术方案是这样实现的:

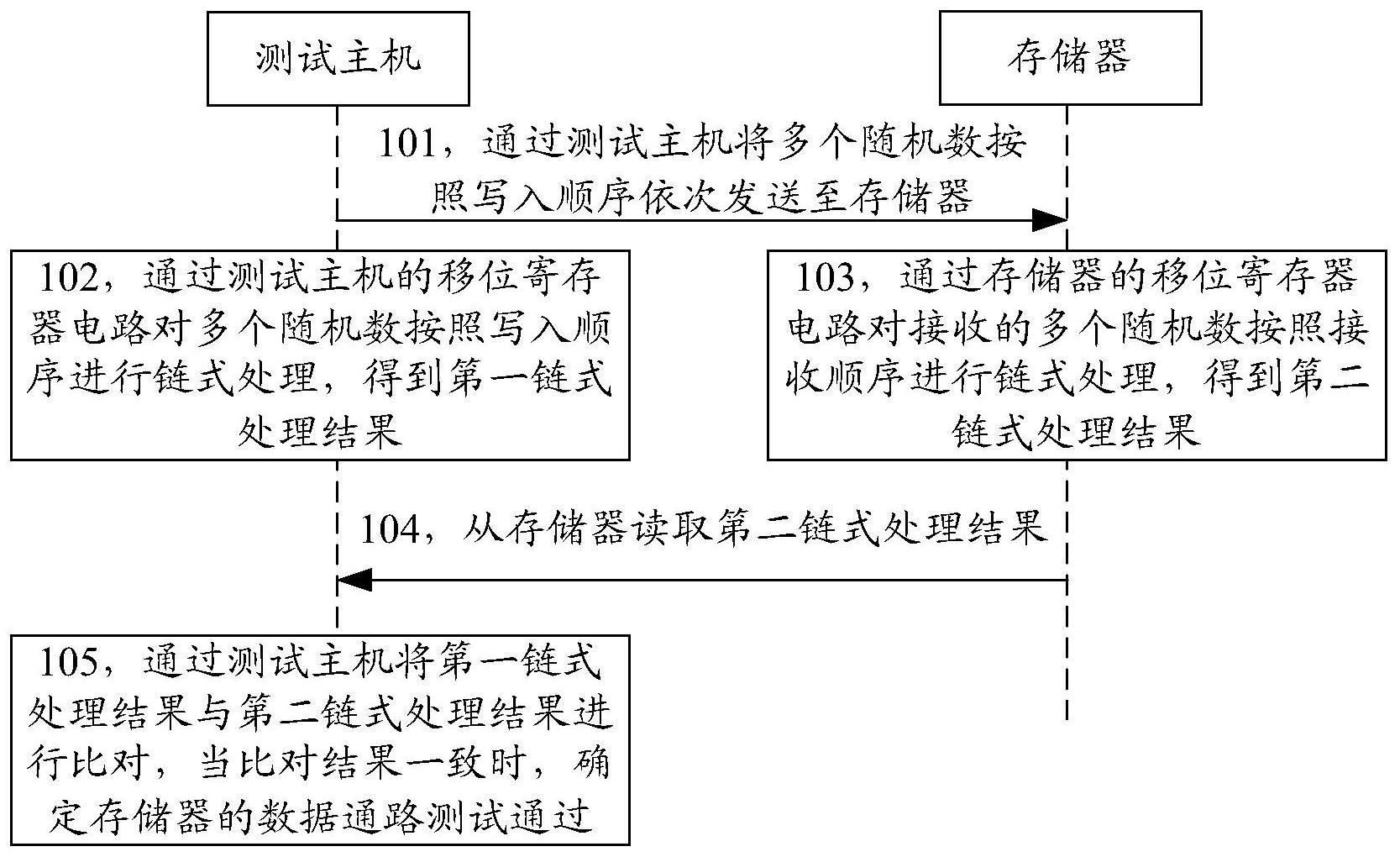

3、本技术实施例提供一种存储器的数据通路测试方法,所述方法包括:

4、通过测试主机将多个随机数按照写入顺序依次发送至所述存储器;

5、通过所述测试主机的电路对所述多个随机数按照所述写入顺序进行链式处理,得到第一链式处理结果;

6、其中,所述第一链式处理结果的位数与写入的最后一个随机数的位数对应;

7、从所述存储器读取第二链式处理结果;

8、其中,所述第二链式处理结果是通过所述存储器的电路对接收的多个随机数按照接收顺序进行链式处理得到的,且所述第二链式处理结果的位数与存储器接收的最后一个随机数的位数对应,所述存储器的电路的电路逻辑与所述测试主机的电路的电路逻辑相同;

9、通过所述测试主机将所述第一链式处理结果与所述第二链式处理结果进行比对,当比对结果一致时,确定所述存储器的数据通路测试通过。

10、本技术实施例提供一种存储器的数据通路测试装置,所述装置包括:

11、发送模块,用于通过测试主机将多个随机数按照写入顺序依次发送至所述存储器;

12、链式模块,用于通过所述测试主机的电路对所述多个随机数按照所述写入顺序进行链式处理,得到第一链式处理结果;其中,所述第一链式处理结果的位数与写入的最后一个随机数的位数对应;

13、接收模块,用于从所述存储器读取第二链式处理结果;其中,所述第二链式处理结果是通过所述存储器的电路对接收的多个随机数按照接收顺序进行链式处理得到的,且所述第二链式处理结果的位数与存储器接收的最后一个随机数的位数对应,所述存储器的电路的电路逻辑与所述测试主机的电路的电路逻辑相同;

14、比对模块,用于通过所述测试主机将所述第一链式处理结果与所述第二链式处理结果进行比对,当比对结果一致时,确定所述存储器的数据通路测试通过。

15、在上述方案中,所述测试主机包括随机数生成器,所述通过测试主机将多个随机数按照写入顺序依次发送至所述存储器之前,所述发送模块,还用于:针对多个时间节点中的每个所述时间节点执行以下处理:通过所述测试主机的随机数生成器在所述时间节点生成至少一个随机数;其中,在所述多个时间节点生成的多个随机数之间互相独立,所述写入顺序是生成每个所述随机数的时间节点的时间先后写入顺序。

16、在上述方案中,所述发送模块,还用于:通过测试主机将多个随机数按照写入顺序依次发送至所述存储器之前,针对多个时间节点中的每个所述时间节点执行以下处理:当所述时间节点是所述多个时间节点中最早的时间节点时,获取针对所述测试主机的电路配置的随机数;当所述时间节点不是所述多个时间节点中最早的时间节点时,通过所述测试主机的电路对输入数据进行数字信号处理,得到对应所述时间节点的随机数;其中,所述写入顺序是生成每个所述随机数的时间节点的时间先后写入顺序,所述测试主机的电路的输入数据是在所述时间节点的上一个相邻时间节点输出的随机数。

17、在上述方案中,所述测试主机的电路的数目为多个;所述发送模块,还用于:获取针对所述测试主机的每个所述电路配置的随机数单元,并将多个所述随机数单元组成所述随机数;通过所述测试主机的每个所述电路执行以下处理:接收在上一个相邻时间节点输出的随机数单元,并对接收的随机数单元进行数字信号处理,得到对应所述时间节点的随机数单元;将所述测试主机的每个所述电路在所述时间节点输出的随机数单元组成所述随机数;其中,所述测试主机的多个电路与多个所述随机数单元一一对应。

18、在上述方案中,所述发送模块,还用于:通过所述测试主机针对每个所述随机数按照所述写入顺序执行以下处理:对所述随机数进行基于配置位数的划分处理,得到多个随机数单元;其中,所述随机数单元包括至少一个上升沿数据位、至少一个下降沿数据位、上升沿数据掩码位、下降沿数据掩码位、上升沿数据总线翻转位以及下降沿数据总线翻转位;将所述多个随机数单元并行发送至所述存储器。

19、在上述方案中,所述链式模块,还用于:按照所述写入顺序针对所述多个随机数中每个所述随机数执行以下处理:通过所述测试主机的电路对上一个相邻随机数的链式处理结果以及所述随机数进行数字信号处理,得到对应所述随机数的链式处理结果;当所述随机数是所述多个随机数中基于所述写入顺序的最后一个随机数时,将对应所述随机数的链式处理结果确定为所述第一链式处理结果。

20、在上述方案中,所述测试主机的电路的数目为多个;所述链式模块,还用于:通过所述测试主机的每个所述电路执行以下处理:接收上一个相邻随机数单元的链式处理结果,并对接收的上一个相邻随机数单元的链式处理结果以及所述随机数中对应所述电路的随机数单元进行数字信号处理,得到对应所述随机数单元的链式处理结果;将所述测试主机的每个所述电路输出的对应所述随机数单元的链式处理结果组成对应所述随机数的链式处理结果。

21、在上述方案中,每个所述电路包括n个级联的电路单元,所述链式模块,还用于:基于所述上一个相邻随机数单元的链式处理结果以及所述随机数中对应所述电路的随机数单元,确定第n电路单元的输入;通过n个级联的电路单元中的第n电路单元,对所述第n电路单元的输入进行移位处理,得到对应所述第n电路单元的输出比特位编码;基于对应所述第n电路单元的输出比特位编码,确定第n+1电路单元的输入;通过第n+1电路单元继续对所述第n+1电路单元的输入进行移位处理,得到对应所述第n+1电路单元的输出比特位编码;其中,n为大于或者等于2的整数,n为取值从1开始递增的整数变量,n的取值范围为1≤n<n;将每个所述电路单元的输出比特位编码进行基于对应电路单元的n值的降序排序处理,并按照降序排序结果将多个所述输出比特位编码组成对应所述随机数单元的链式处理结果。

22、在上述方案中,所述链式模块,还用于:当所述第n+1电路单元与所述第n电路单元之间直接连接时,将所述第n电路单元的输出比特位编码、以及所述随机数单元中对应所述第n+1电路单元的输入比特位编码作为所述第n+1电路单元的输入;当所述第n+1电路单元与所述第n电路单元之间通过异或门连接时,对第n电路单元在上一相邻时间节点输出的首位编码与所述第n电路单元的输出比特位编码进行异或处理,得到异或输出比特位编码,将所述异或输出比特位编码、以及所述随机数单元中对应所述第n+1电路单元的输入比特位编码确定为所述第n+1电路单元的输入。

23、在上述方案中,所述第n电路单元包括第一与门、第二与门、异或门以及触发器;所述链式模块,还用于:当n取值为1时,通过所述第一与门对所述随机数单元的末位编码以及第一编码值进行与门处理,得到第一与门结果;通过所述第二与门对第二编码值以及在上一相邻时间节点所述电路输出的随机数单元的首位编码进行与门处理,得到第二与门结果;通过所述异或门对所述第一与门结果与所述第二与门结果进行异或处理,得到异或结果,并将所述异或结果传输至所述触发器;当所述触发器接收到时钟信号时,将所述异或结果确定为所述第n电路的输出比特位编码。

24、在上述方案中,所述第n电路单元包括第一与门、第二与门、异或门以及触发器;所述链式模块,还用于:当n的取值范围为2≤n<n时,通过所述第一与门对所述随机数单元的第n-n+1位编码以及第一编码值进行与门处理,得到第一与门结果;当所述第n-1电路单元与所述第n电路单元通过所述异或门连接时,对第n电路单元在上一相邻时间节点输出的首位编码与所述第n-1电路单元的输出比特位编码进行异或处理,得到异或输出比特位编码,通过所述第二与门对第二编码值以及所述异或输出比特位编码进行与门处理,得到第二与门结果;当所述第n-1电路单元与所述第n电路单元直接连接时,通过所述第二与门对第二编码值以及所述第n-1电路单元的输出比特位编码进行与门处理,得到第二与门结果;

25、;通过所述异或门对所述第一与门结果与所述第二与门结果进行异或处理,得到异或结果,并将所述异或结果传输至所述触发器;当所述触发器接收到时钟信号时,将所述异或结果确定为所述第n电路的输出比特位编码。

26、本技术实施例提供一种电子设备,包括:

27、存储器,用于存储可执行指令;

28、处理器,用于执行所述存储器中存储的可执行指令时,实现本技术实施例提供的存储器的数据通路测试方法。

29、本技术实施例提供一种计算机可读存储介质,存储有可执行指令,用于被处理器执行时,实现本技术实施例提供的存储器的数据通路测试方法。

30、本技术实施例具有以下有益效果:

31、通过本技术实施例提供的存储器的数据通路测试方法可以由测试主机对多个随机数进行发送至存储器,并接收存储器返回的对应最后一个随机数的第二链式处理结果,将存储器返回的对应最后一个随机数的链式处理结果与测试主机对对多个随机数进行链式处理得到的第一链式处理结果进行比对,由此可以看出整个过程包括多次数据发送以及单次数据接收,最终仅需要基于单次接收得到的对应最后一个随机数的第二链式处理结果进行比对,减少了比对次数也节省了该次比对需要比对的数据量,从而提升了存储器的数据通路测试效率。

- 还没有人留言评论。精彩留言会获得点赞!