一种快速处理集成电路版图走线的电磁仿真方法及装置与流程

1.本技术属于集成电路版图电磁仿真技术领域,具体涉及一种快速处理集成电路版图走线的电磁仿真方法及装置。

背景技术:

2.随着通信技术的发展,超大规模集成电路的研究与发展已逐渐展开。为了提高电子设备的性能,缩小体积,降低成本,将晶体管与其他元器件以及线路都集成在一小块半导体基片上。为了实现更多的功能,超大规模集成电路有几层到上百层结构,每层结构极其复杂,集成数千万甚至数亿的晶体管,对数千万、数亿个分布在各层的元器件提供稳定、达标的电压是集成电路电源设计首先需要考虑的问题,在此基础上,还需要保证集成电路电源层各处的电流密度不能过大,否则会导致局部过热,直至电路板烧毁。为此,需要针对设计的超大规模集成电路的电位分布和电流分布进行仿真计算,以针对电压降和电流密度超标的区域进行设计上的整改,避免因为设计失误带来损失。

3.在集成电路元器件分布越来越密集的情况下,集成电路的覆铜版图也会因不同网络的不同元器件的连接形成的走线而被裁剪成非常复杂的几何图形。通常做法是将这些复杂的几何图形离散成形状简单的网格单元,再基于这些网格单元进行数值计算以获得形状复杂的版图的电位分布和电流分布。在集成电路版图的电磁仿真过程中,由于走线的不规则性,通常针对走线的处理是将走线也当版图多边形处理,对走线形成的覆铜层也进行同样的网格剖分,然后统一通过有限元方程的求解计算每个网格节点的电位,在此基础上通过插值的方法计算版图多边形上的电位分布和电流分布。这样处理的好处是处理方法统一简单,缺点是在细长的走线及其周围会产生大量的网格单元,由此大大增加稀疏矩阵的求解规模,进而增加电磁仿真的时间。目前还没有方法解决上述问题。

技术实现要素:

4.为解决现有技术中的不足,本技术提出了一种快速处理集成电路版图走线的电磁仿真方法及装置。

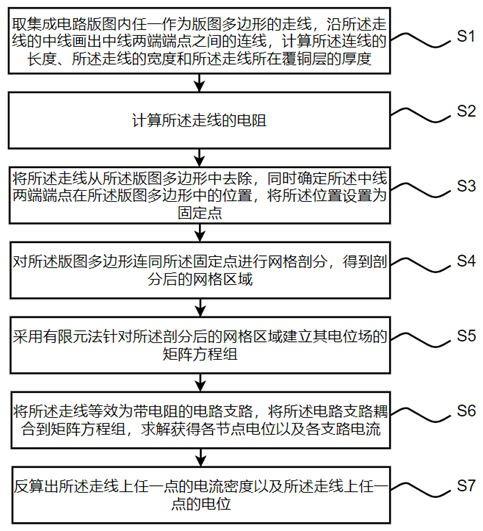

5.第一方面本技术提出了一种快速处理集成电路版图走线的电磁仿真方法,包括如下步骤:取集成电路版图内任一作为版图多边形的走线,沿所述走线的中线画出中线两端端点之间的连线,计算所述连线的长度、所述走线的宽度和所述走线所在覆铜层的厚度;计算所述走线的电阻;将所述走线从所述版图多边形中去除,同时确定所述中线两端端点在所述版图多边形中的位置,将所述位置设置为固定点;对所述版图多边形连同所述固定点进行网格剖分,得到剖分后的网格区域;采用有限元法针对所述剖分后的网格区域建立其电位场的矩阵方程组;将所述走线等效为带电阻的电路支路,将所述电路支路耦合到矩阵方程组,求解

获得各节点电位以及各支路电流;反算出所述走线上任一点的电流密度以及所述走线上任一点的电位。

6.所述走线须满足走线长度大于或等于所述走线宽度10倍。

7.采用有限元法针对所述剖分后的网格区域建立其电位场的矩阵方程组,具体表述为:式中k为有限元刚度矩阵,u为网格节点的电位向量,b为与外部激励产生的表面电流密度相关的右端项。

8.将所述走线等效为带电阻的电路支路,将所述电路支路耦合到矩阵方程组,求解获得各节点电位以及各支路电流,包括如下步骤:建立所述走线的电路方程;将所述电路方程加入到所述矩阵方程组,得到修改的矩阵方程;改写所述矩阵方程组得到通用的修改的矩阵方程组;求解所述通用的修改的矩阵方程组,获得各节点电位以及各支路电流,所述支路电流即为所述走线的电流。

9.所述建立所述走线的电路方程,如下式:设走线的中线两端点为a和b,a和b对应的固定点在网格节点中的编号为na和nb,其对应的电位为u(na)和u(nb),i

ab

为经过走线ab的电流,r

ab

为所述走线ab的电阻。

10.所述通用的修改的矩阵方程组,如下式:式中ku为与节点电位相关的矩阵,a

ui

为节点电位与支路电流的关联矩阵,ki为与支路电流相关的矩阵,i为走线电流的未知量形成的列向量。

11.所述反算出所述走线上任一点的电流密度以及所述走线上任一点的电位,具体计算过程如下:反算出走线上任一点p的电流密度为:反算出走线上的中线上任一点p的电位为:其中l

ap

为中线上p到a沿中线的长度,l

ab

为中线上b到a沿中线的长度,w为走线的宽度,d为走线覆铜的厚度;所述走线的中线采用以下方法获得:针对多条直走线段连成的走线,相邻直走线段的轮廓线的交点称为拐点,根据所述走线上的所有拐点对连成的线段对走线进行分割,将所述走线分为m段,对每个所述走线段,连接所述走线段的一端的边的中点和所述走线段另一端的边的中点形成每个走线段的中线,连接所有走线段的中线形成所述走线的中线;

走线上任一点的电位根据走线上的中线上的电位采用分段插值法计算求值。

12.所述采用分段插值法计算求值过程如下:对每个所述走线段进行插值,设置所述走线段的一端的边为pq,顶点为p、q,设置所述走线段另一端的边为cg,顶点为c、g,走线段af所形成的区域pcgq的中线为af,所述中线端点f位置的电位计算公式为:其中,为中线af的长度,为中线上点f的电位,u(pq)=u(na), u(cg)=,u(pq)表示边pq上任意点的电位,u(cg)表示边cg上任意点的电位;pcgq区域其他位置h的电位通过以下步骤得出,过h作与pc平行的直线,与pq交点为h1,与cg交点为h2,则其中,为pcgq区域其他位置h的电位,为h与h1之间连线的长度,为h1与h2之间连线的长度。

13.第二方面本技术提出了一种快速处理集成电路版图走线的电磁仿真装置,包括第一模块、第二模块、第三模块、第四模块、第五模块、第六模块、第七模块,各模块依次顺序连接;第一模块用于取集成电路版图内任一作为版图多边形的走线,沿所述走线的中线画出中线两端端点之间的连线,计算所述连线的长度、所述走线的宽度和所述走线所在覆铜层的厚度;第二模块用于计算所述走线的电阻;第三模块用于将所述走线从所述版图多边形中去除,同时确定所述中线两端端点在所述版图多边形中的位置,将所述位置设置为固定点;第四模块用于对所述版图多边形连同所述固定点进行网格剖分,得到剖分后的网格区域;第五模块用于采用有限元法针对所述剖分后的网格区域建立其电位场的矩阵方程组;第六模块用于将所述走线等效为带电阻的电路支路,将所述电路支路耦合到矩阵方程组,求解获得各节点电位以及各支路电流;第七模块用于反算出所述走线上任一点的电流密度以及所述走线上任一点的电位。

14.所述第六模块包括第一单元、第二单元、第三单元、第四单元,各单元依次顺序连接;所述第一单元用于建立所述走线的电路方程;所述第二单元用于将所述电路方程加入到所述矩阵方程组,得到修改的矩阵方程;所述第三单元用于改写所述矩阵方程组得到通用的修改的矩阵方程组;所述第四单元用于求解所述通用的修改的矩阵方程组,获得各节点电位以及各支

路电流,所述支路电流即为所述走线的电流。

15.有益技术效果在走线长度远大于走线宽度情况下,本技术提出的一种快速处理集成电路版图走线的电磁仿真方法及装置避免了传统方法处理细长走线时,在其周围产生大量的网格单元,进而大大增加了稀疏矩阵的求解规模,增加电磁仿真的时间的问题,并因为走线长度远大于走线宽度,忽略了进行走线端部电流计算时产生理论误差问题,实现了集成电路电位分布和电流分布的快速仿真计算。

附图说明

16.图1为快速处理集成电路版图走线的仿真方法流程图;图2为含有拐角的走线示意图;图3为快速处理集成电路版图走线的仿真装置原理框图。

具体实施方式

17.在集成电路版图的电磁仿真过程中,针对走线的处理是将走线当版图多边形处理,通过有限元方程组求解出电位分布,通过公式计算电流密度分布,式中j为场域(即多边形覆铜区域)内任意点的电流密度,e为电场强度,为电导率,为梯度算子,u为求解的电位场。此方法缺点是在细长的走线及其周围会产生大量的网格单元,大大增加了稀疏矩阵的求解规模,进而增加电磁仿真的时间。

18.本技术提出一种快速处理集成电路版图走线的仿真方法及装置,在走线长度大于或等于走线宽度10倍时,可以将走线等效为连接走线两端的理想导线与带电阻的电路支路,将这个支路耦合到有限元方法形成的电位场的矩阵方程组,用来计算走线两端的电位,然后,反过来计算走线任意位置的电位和电流。与将走线作为多边形加入到场的计算相比,这个等效在走线绝大部分位置是准确的,但由于这个等效忽略了走线的端部,忽略了走线端部的电流分布由于几何形状的改变而发生了变化,因此对于走线端部电流分布的计算有理论上的误差。如果走线长度远大于走线宽度,这个误差可以忽略不计。

19.由于集成电路版图的走线的特点是宽度一致且为细长形状,可以假设走线上电流密度分布均匀,可将集成电路版图的走线简化为带电阻的电路支路,即将走线所在的覆铜层用带电阻的电路支路代替,并将这个电路与网格剖分形成的矩阵方程组进行耦合,形成场-路耦合方程组进行求解。求解获得走线两端的电位后,即可根据走线的几何尺寸反算走线上的电位分布和电流分布。

20.下面结合附图对本技术作进一步描述。以下实施例仅用于更加清楚地说明本发明的技术方案,而不能以此来限制本技术的保护范围。

21.第一方面,本技术提出一种快速处理集成电路版图走线的电磁仿真方法,如图1所示,步骤如下:步骤s1:取集成电路版图内任一作为版图多边形的走线,如图2所示,沿所述走线的中线画出中线两端端点a和b之间的连线,计算所述连线的长度l、所述走线的宽度w和所述走线所在覆铜层的厚度d;步骤s2:计算所述走线的电阻r,公式如下:

其中,为走线所在覆铜层的电导率。

22.步骤s3:将所述走线从所述版图多边形中去除,同时确定所述中线两端端点在所述版图多边形中的位置,将所述位置设置为固定点;步骤s4:对所述版图多边形连同所述固定点进行网格剖分,得到剖分后的网格区域;过程详述如下:将所述固定点插入到版图多边形所在网格,对含有固定点的版图多边形所在网格进行网格剖分,并确保所述固定点包含在剖分的网格中。

23.步骤s5:采用有限元法针对所述剖分后的网格区域建立其电位场的矩阵方程组;如下式所示:(1)式中k为有限元刚度矩阵,u为网格节点的电位向量,b为与外部激励产生的表面电流密度相关的右端项;其中k与b具体计算步骤如下:s5.1对于集成电路的电源网络,其网络上的直流电源在覆铜层的电流形成直流电场模型;由于集成电路的结构为多层带复杂版图形状的覆铜层和介质形成的三维多层结构,因此需要计算的集成电路模型为多层集成电路的三维直流电场模型,此时,直流电场模型中电导率、电位u的分布均为三维空间坐标(x,y,z)的函数,即:,该三维直流电场模型的函数满足以下方程(2):(2)及边界条件(3):(3)式中为第一类边界,n为第二类边界的法向,表示电位u在第一类边界上的值,用表示,为外部电流源的体电流密度;s5.2多层超大规模集成电路中实际pcb板或芯片封装的板尺寸远大于金属层的厚度,将多层集成电路的三维直流场问题简化为二维直流场问题;由此可以建立各层集成电路直流电场二维模型的泛函(4):

(4)式中,所述i(u)为泛函,t为金属层的厚度,为网格单元e的电导率,为网格单元e的电位,为网格单元e的面积,为外部激励产生的表面电流密度,表示网格单元e的边;s5.3对所述泛函(4)取极值并令极值为0,即可获得有限元法形成的矩阵方程组(1),其中b为与外部激励产生的表面电流密度相关的右端项,即为泛函(4)中的;而有限元方程组(1)的左端k矩阵则为泛函(4)中的。

24.步骤s6:将所述走线等效为带电阻的电路支路,将所述电路支路耦合到矩阵方程组,求解获得各节点电位以及各支路电流;具体包括步骤如下:s6.1设走线的端点a和b对应的固定点在网格节点中的编号为na和nb,其对应的电位为u(na)和u(nb);建立走线的端点a和b之间的电路方程,如下式(5)所示:(5)式中i

ab

为经过走线ab的电流,l

ab

为走线ab的长度。

25.s6.2将走线ab之间的电路方程加入到原来的矩阵方程组,形成修改的矩阵方程,如下式(6)所示:(6)式中ku为有限元法形成的与节点电位相关的矩阵,a

ui

为节点电位u(na)和u(nb)与支路电流的关联矩阵,其为的矩阵,第na和nb个元素为1,其余元素为0,其中n为有限元节点电位未知量的个数,也是矩阵ku的维数。

26.对于单条走线ab来说,与原有的矩阵方程组相比,增加了一个方程,同时也增加了一个未知量i

ab

。

27.s6.3当有多条走线作以上相同转换时,原始方程组形成以下通用的修改的矩阵方程组(7):

(7)式中ku为与节点电位相关的矩阵,a

ui

为节点电位与支路电流的关联矩阵,ki为与支路电流相关的矩阵,其中a

ui

为多个a

ui

按行组合而成,其组合的顺序为处理走线的顺序,矩阵大小为,m为待处理的走线数量,ki为对角阵,矩阵大小为,第i个元素为-ri,这里ri为第i条走线的电阻,i为走线电流的未知量形成的列向量。

28.s6.4求解所述通用的修改的矩阵方程组,获得各节点电位以及各支路电流,所述支路电流即为所述走线的电流。

29.步骤s7:反算出所述走线上任一点的电流密度以及所述走线上任一点的电位。具体过程详述如下:由于假设了走线电流密度分布均匀,则可反算出走线上任一点p的电流密度为式(8)所示:(8)同时反算出走线上的中线上任一点p的电位为式(9)所示:(9)其中l

ap

为中线上p到a沿中线的长度,l

ab

为中线上b到a沿中线的长度,w为走线的宽度,d为走线覆铜的厚度。所述走线的中线采用以下方法获得:针对多条直走线段连成的走线,相邻直走线段的轮廓线的交点称为拐点,根据所述走线上的所有拐点对连成的线段对走线进行分割,将所述走线分为m段,对每个所述走线段,连接所述走线段的一端的边的中点和所述走线段另一端的边的中点形成每个走线段的中线,连接所有走线段的中线形成所述走线的中线。

30.走线上任一点的电位根据走线上的中线上的电位采用分段插值法计算求值。

31.在具体实施中,对每个走线段进行插值,本实施例,如图2所示,走线段的一端的边为pq,点p、q为边pq的两个顶点,边pq的中点为a,另一端边的中点为b,以走线ab命名此走线,点c、g位于走线ab拐角位置处,为走线ab的一对拐角对,连线cg的中点为f,根据此拐角对对走线ab分割,得到走线段af,所述走线段af另一端的边即为cg,边cg的顶点即为c、g,,走线段af所形成的区域pcgq的中线为af。

32.由于走线长度远大于走线宽度,例如走线长度为1cm,宽度为,假设在长度上的压降为0.1v,即u(ab)=0.1v,且由于走线上的电流沿走线中线流动,因此走线上的电压沿中线的下降速度远大于沿宽度方向的下降速度,即走线宽度上的压降远小于1,因此,可近似认为u(pq)=u(na),u(cg)=,其中为中线上点f的电位,u(pq)表示边pq上任意点的电位,u(cg)表示边cg上任意点的电位,为中线af的长度。所述中点f位置的电位可通过下式计算得出:

那么走线pcgq区域其他位置h的电位采用插值法计算求值,计算如下:过h作与pc平行的直线,与pq交点为h1,与cg交点为h2,则其中, 为pcgq区域其他位置h的电位,为h与h1之间连线的长度,为h1与h2之间连线的长度;同理可以求出走线ab其他走线段任意点的电位;当走线不存在拐点时,即,计算过程同上,此时由实际计算求值结果可认为走线上任一点电位等于过此点与中线垂直的中线位置的电位。

33.第二方面本技术提出了一种快速处理集成电路版图走线的电磁仿真装置,如图3所示:包括第一模块、第二模块、第三模块、第四模块、第五模块、第六模块、第七模块,各模块依次顺序连接;第一模块用于取集成电路版图内任一作为版图多边形的走线,沿所述走线的中线画出中线两端端点之间的连线,计算所述连线的长度、所述走线的宽度和所述走线所在覆铜层的厚度;第二模块用于计算所述走线的电阻;第三模块用于将所述走线从所述版图多边形中去除,同时确定所述中线两端端点在所述版图多边形中的位置,将所述位置设置为固定点;第四模块用于对所述版图多边形连同所述固定点进行网格剖分,得到剖分后的网格区域;第五模块用于采用有限元法针对所述剖分后的网格区域建立其电位场的矩阵方程组;第六模块用于将所述走线等效为带电阻的电路支路,将所述电路支路耦合到矩阵方程组,求解获得各节点电位以及各支路电流;第七模块用于反算出所述走线上任一点的电流密度以及所述走线上任一点的电位。

34.所述第六模块包括第一单元、第二单元、第三单元、第四单元,各单元依次顺序连接;所述第一单元用于建立所述走线的电路方程;所述第二单元用于将所述电路方程加入到所述矩阵方程组,得到修改的矩阵方程;所述第三单元用于改写所述矩阵方程组得到通用的修改的矩阵方程组;所述第四单元用于求解所述通用的修改的矩阵方程组,获得各节点电位以及各支路电流,所述支路电流即为所述走线的电流。

35.本发明申请人结合说明书附图对本发明的实施示例做了详细的说明与描述,但是本领域技术人员应该理解,以上实施示例仅为本发明的优选实施方案,详尽的说明只是为了帮助读者更好地理解本发明精神,而并非对本发明保护范围的限制,相反,任何基于本发明的发明精神所作的任何改进或修饰都应当落在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1