一种两步模迭代法应用于混合尺寸单元电路设计

1.本发明涉及超大规模集成电路物理设计自动化领域,具体涉及一种两步模迭代法应用 于混合尺寸单元电路设计,可用于混合尺寸标准单元电路的合法化过程。

背景技术:

2.多年来,单倍行高标准单元布局一直占据着主导地位。然而,随着高级技术节点设要 求的复杂性增加,混合尺寸标准单元电路布局逐渐被引入到超大规模集成电路设计中。通 常,如反相器这类简单的单元被设计成单倍行高,而触发器这类复杂单元则被设计成多倍 行高;在物理设计综合中,布局阶段的目标是确定各个单元在版图中的位置以及方向。

3.布局问题是np-难问题,且每个电路设计中的标准单元数据庞大,使得解空间爆炸, 精确求解几乎变得不可能;因此通常采用一些近似方法来获得近似最优解,以避免直接求 解的计算时间复杂度;然而,如何快速、高效地逼近最优解是当前亟待解决的一个问题。

4.为简化布局阶段的设计复杂度,通常将该阶段进行分解成三个子阶段,即全局布局、 合法化、详细布局阶段。全局布局阶段中会暂时忽略单元间重叠,以最小化线长为目标; 合法化则是消除上一阶段中产生的单元重叠,并间单元对齐到行中的可放置位置中去;详 细布局阶段会通过单元交换等操作来进一步细化前序阶段的布局结果;由于标准单元的异 质结构,使得合法化问题变得愈加复杂;现有的合法化算法主要有启发式算法、解析式算 法;启发式算法具有求解速度快的优点,然而容易陷入局部最优解;解析式算法则能从全 局角度对问题模型进行分析,更有可能产生高质量邻域解;陈建利等(cn 106971042 a) 提出了将合法化问题中二次规划问题转化成线性互补问题,并应用模系矩阵分裂迭代法对 线性互补问题进行求解;从全局角度出发,进一步提高求解线性互补问题的收敛速度,但 是其迭代次数以及运行时间都比较长,布局阶段设计效率低。

技术实现要素:

5.发明目的:本发明的目的是为了解决现有技术中的不足,本发明提供一种两步模迭代 法应用于混合尺寸单元电路设计,该方法由前向扫描和向后扫描组成,能减少线性互补问 题求解过程中的迭代次数以及运行时间,进一步提升布局阶段设计效率。

6.为了实现以上目的,本发明提供一种两步模迭代法应用于混合尺寸单元电路设计,用于混 合尺寸标准单元电路的合法化过程,包括如下步骤:

7.s1:对标准单元进行预处理,将多倍行高标准单元分割为多个单倍行高标准子单元;

8.s2:将标准单元进行扩散;

9.s3:将混合尺寸标准单元合法化问题表示为二次规划数学模型;

10.s4:将二次规划模型转换成线性互补问题;

11.s5:利用两步模系矩阵分裂迭代法求解线性互补问题;

12.s6:将多倍行高标准单元分割成的子单元的x坐标进行统一,并对齐到行中的可放置 位上;

13.s7:对剩余的非法单元进行合法化处理。

14.进一步的,步骤s1的具体实现方式包括:给定一个芯片的布局矩形区域,用(0,0)和 (w,h)分别表示其左下角坐标和右上角坐标;w表示布局区域的宽度,h表示布局区域的 高度;待布局的标准单元集为c=(c1,c2,

…cn

),其中单元ci从全局阶段获得的初始左下角 坐标为单元宽度及高度分别为wi,hi,所求的合法化阶段后的坐标为(xi,yi);将 所有标准单元对齐到最近的与其电源线匹配的行上去;对于多倍行高标准单元,将其表示 成多个子单元,用(c

i1

,c

i2

,

…cit

)表示,其中,t表示标准单元的高度是行高的t倍。

15.进一步的,步骤s2中,为避免后续处理中标准单元过于拥挤,利用网络流算法对单元进 行扩散,确保每行中的单元宽度之后不超过该行的宽度;我们对布局区域在水平方向和垂 直方向进行均匀地划分成网格,每一个网格构成网络流图中的一个节点;此外,再额外创 建两个节点,即超级源节点(nb)和超级汇节点(ne);计算每个网格中所属单元的面积 之和sc,将其与网格面积sg进行比较;如果sc》sg,则该网格称为溢出网格并记录溢出 的面积so;如果sc≤sg,则该网格称为空闲网格并记录剩余的空闲面积sf。对于溢出网 格,将其设置成网络流中的源节点ns,并建立一条从nb到ns的弧,弧上的容量和成本分 别设置为so和零;对于空闲网格,将其设置为目标节点n

t

,并建立一条从n

t

到ne的弧, 弧上的容量和成本分别设置为sf和0;并且对溢出网格,寻找与它相邻的空闲网格,建立 从ns到n

t

的弧,弧上的容量和成本分别设置为无穷大和单元在两个网格之间移动的位 移;对于建立好的网络流图进行求解,可得到单元在网格中移动的策略,按照该策略移动 单元,移动后的单元ci的坐标为进一步的,步骤s3中,合法化过程是消除单元之间的重叠,并以最小化标准单元总位移 为优化目标,并且在前述步骤中单元已经进行垂直方向上的最小移动,即与匹配的电源轨 对齐,因此可忽略垂直方向上的位移,将合法化问题描述为下述模型(17):

[0016][0017]

将上述模型改写为凸二次规划问题的标准形式,即:

[0018][0019]

其中,b是一个单位矩阵,是一个分量由单元的初始横坐标构成 的列向量;任意相邻的一对标准单元应该满足不等式x

j-xi≥wi(xj≥xi),对所有相邻单元 之间建立该不等式,则可以写成矩阵形式wx≥d,w为每行仅包含-1和1这两个元素的 矩阵,分别表示单元ci和cj的横坐标xj,xi,d为一个列向量,其中对应的分量表示左侧单 元ci的宽度wi;那么w和d的行数为约束的个数,w的列数为标准单元的总个数,即单倍 行高单元的数量与多倍行高单元拆分成的子单元数量之和;r同样为每行由-1和1组成的 矩阵,-1

表示多倍行高单元ci的子单元c

i1

,1表示ci的子单元c

i2

,依次推类。x

i2-x

i1

=0保证ci的子单元横坐标相等,由此可得到约束矩阵rx=0;一个混合尺寸标准单元布局的简单示例,根据该位置构造的矩阵w、r和向量d如下所示:

[0020]

r=(0-110),d=(w1w2);

[0021]

利用拉格朗日乘子法,将二次规划中的等式约束加入到目标函数中,则(23)可表示为:

[0022][0023]

其中,λ为拉格朗日乘子。

[0024]

进一步的,所述步骤s4中,利用karush-kuhn-tucker(kkt)条件,可将模型(23)写成如下条件的kkt方程组:

[0025][0026]

将方程组(23)改下为如下形式:

[0027][0028]

令该问题则演变为寻求一对非负且正交的解向量(w,z)满足如下条件:

[0029]

w=az+q≥0,z≥0andw

t

z≥0.(14)

[0030]

问题(23)则为线性互补问题。

[0031]

进一步的,所述步骤s5的具体实施方式为:令a=m

1-n1=m

2-n2为a的两个分裂,则(23)可转换成下列等价的绝对值方程:

[0032][0033]

给定一个任意的初始向量v

(0)

∈rn×1,通过迭代地求解线性系统来计算v

(k+1)

的值,直到绝对残差向量的二范数res(z

(k)

):=||min(az

(k)

+q,z

(k)

)||2小于等于给定的一个常数,此时可认为迭代序列收敛,该求解过程可描述为:

[0034][0035]

且

[0036][0037]

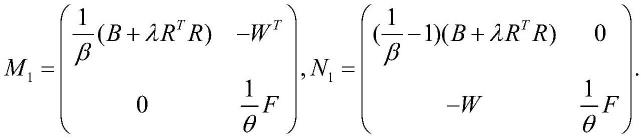

对于公式(24),可以采用cholesky分解或者lu分解等直接法进行求解,也采用共轭 梯度法进行近似求解;取ω=ωi,选取的m1,n1,m2,n2如下所示:

[0038][0039][0040]

其中,β,θ为正常数,f=tridiag(w(b+λr

t

r)-1wt

)是矩阵a的舒尔补矩阵 w(b+λr

t

r)-1wt

的三对角矩阵。由于矩阵求逆需要耗费大量时间,应用sherman-morrison 公式简化求逆计算;因为rr

t

是一个由对角线元素均为2构成的对角矩阵,且b为单位矩 阵,那么(b+λr

t

r)-1

可用如下等式表示:

[0041][0042]

因此,进一步的,所述步骤s6中,将每个多倍行高标准单元的所有子单元的x坐标按照升序排 序,中位数即为所求的该多倍行高单元的x坐标,接着将单元放置到离所求得的x坐标最 近的可放置位上。

[0043]

进一步的,所述步骤s7中,针对少许仍然重叠或超出布局区域右边界的标准单元,从布 局区域右上角开始,按照从右到左,从上到下的顺序对标准单元进行遍历,若单元ci超过 右边界,则把其坐标置为w-wi,若单元ci与c

i-1

重叠,则将c

i-1

坐标置为x

i-w

i-1

。由于多 倍行高单元的移动可能会引起相邻行的单元重叠,因此,对于在上一行中已经移动过的多 倍行高单元,在下一行则不再移动它们;接着,按照相同的规则从左到右,从下到上的顺 序遍历再次遍历标准单元,经过该步骤处理后,所有单元重叠均可消除。

[0044]

本发明的上述技术方案相比现有技术具有以下优点:一种两步模迭代法应用于混合尺 寸单元电路设计,首先对多倍行高单元预处理成单倍行高子单元,然后对所有单元建立网 络流,对其进行扩散,避免局部拥挤,接着将合法化问题等价为凸二次规划,并将二次规 划问题等价地转换成线性互补问题,利用两步模系矩阵分裂迭代法求解,最后将多倍行高 标准单元进行复原并放置到行中的可放置位上,并对余下的非法单元进行处理;与现有技 术相比,本发明通过一种前向扫描和向后扫描技术,通过选取两对合适的分裂矩阵 m1,n1,m2,n2,能够加快迭代过程的收敛速度,快速得到合法化问题的高质量邻域解,能 减少线性互补问题求解过程中的迭代次数以及运行时间,进一步提升布局阶段设计效率。

附图说明

[0045]

图1是混合尺寸标准单元电路合法化流程图;

[0046]

图2是混合尺寸标准单元的布局示例图;

[0047]

图3是两步模系矩阵分裂迭代法求解步骤图。

具体实施方式

[0048]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地 描述,显然,所描述的实施例仅是本发明一部分实施例,而不是全部的实施例,基于本发 明中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例, 都属于本发明保护的范围。

[0049]

如图1所示的一种两步模迭代法应用于混合尺寸单元电路设计,具体步骤如下:

[0050]

s1:对标准单元进行预处理,将多倍行高标准单元分割为多个单倍行高标准子单元;

[0051]

具体实现方式包括:给定一个芯片的布局矩形区域,用(0,0)和(w,h)分别表示其左下 角坐标和右上角坐标;w表示布局区域的宽度,h表示布局区域的高度。待布局的标准单 元集为c=(c1,c2,

…cn

),其中单元ci从全局阶段获得的初始左下角坐标为单元宽 度及高度分别为wi,hi,所求的合法化阶段后的坐标为(xi,yi);将所有标准单元对齐到最 近的与其电源线匹配的行上去。对于多倍行高标准单元,将其表示成多个子单元,用 (c

i1

,c

i2

,

…cit

)表示,其中,t表示标准单元的高度是行高的t倍。

[0052]

s2:将标准单元进行扩散;

[0053]

为避免后续处理中标准单元过于拥挤,利用网络流算法对单元进行扩散,确保每行中 的单元宽度之后不超过该行的宽度;我们对布局区域在水平方向和垂直方向进行均匀地划 分成网格,每一个网格构成网络流图中的一个节点;此外,再额外创建两个节点,即超级 源节点(nb)和超级汇节点(ne);计算每个网格中所属单元的面积之和sc,将其与网格 面积sg进行比较;如果sc》sg,则该网格称为溢出网格并记录溢出的面积so;如果 sc≤sg,则该网格称为空闲网格并记录剩余的空闲面积sf;对于溢出网格,将其设置成网 络流中的源节点ns,并建立一条从nb到ns的弧,弧上的容量和成本分别设置为so和零; 对于空闲网格,将其设置为目标节点n

t

,并建立一条从n

t

到ne的弧,弧上的容量和成本 分别设置为sf和0;并且对溢出网格,寻找与它相邻的空闲网格,建立从ns到n

t

的弧, 弧上的容量和成本分别设置为无穷大和单元在两个网格之间移动的位移;对于建立好的网 络流图进行求解,可得到单元在网格中移动的策略,按照该策略移动单元,移动后的单元 ci的坐标为

[0054]

s3:将混合尺寸标准单元合法化问题表示为二次规划数学模型;

[0055]

合法化过程是消除单元之间的重叠,并以最小化标准单元总位移为优化目标,并且在 前述步骤中单元已经进行垂直方向上的最小移动,即与匹配的电源轨对齐,因此可忽略垂 直方向上的位移,将合法化问题描述为下述模型(17):

[0056][0057]

将上述模型改写为凸二次规划问题的标准形式,即:

[0058][0059]

其中,b是一个单位矩阵,是一个分量由单元的初始横坐标构成的列向量;任意相邻的一对标准单元应该满足不等式x

j-xi≥wi(xj≥xi),对所有相邻单元之间建立该不等式,则可以写成矩阵形式wx≥d,w为每行仅包含-1和1这两个元素的矩阵,分别表示单元ci和cj的横坐标xj,xi,d为一个列向量,其中对应的分量表示左侧单元ci的宽度wi;那么w和d的行数为约束的个数,w的列数为标准单元的总个数,即单倍行高单元的数量与多倍行高单元拆分成的子单元数量之和;r同样为每行由-1和1组成的矩阵,-1表示多倍行高单元ci的子单元c

i1

,1表示ci的子单元c

i2

,依次推类;x

i2-x

i1

=0保证ci的子单元横坐标相等,由此可得到约束矩阵rx=0;图2是一个混合尺寸标准单元布局的简单示例图,根据该位置构造的矩阵w、r和向量d如下所示:

[0060]

r=(0-110),d=(w1w2)。

[0061]

利用拉格朗日乘子法,将二次规划中的等式约束加入到目标函数中,则(23)可表示为:

[0062][0063]

其中,λ为拉格朗日乘子。

[0064]

s4:将二次规划模型转换成线性互补问题;

[0065]

利用karush-kuhn-tucker(kkt)条件,可将模型(23)写成如下条件的kkt方程组:

[0066][0067]

将方程组(23)改下为如下形式:

[0068][0069]

令该问题则演变为寻求一对非负且正交的解向量(w,z)满足如下条件:

[0070]

w=az+q≥0,z≥0andw

t

z≥0.(22)

[0071]

问题(23)则为线性互补问题。

[0072]

s5:利用两步模系矩阵分裂迭代法求解线性互补问题;

[0073]

进一步地,所述步骤s5的具体实施方式为:令 a=m

1-n1=m

2-n2为a的两个分裂,则(23)可转换成下列等价的绝对值方程:

[0074][0075]

给定一个任意的初始向量v

(0)

∈rn×1,通过迭代地求解线性系统来计算v

(k+1)

的值,直到 绝对残差向量的二范数res(z

(k)

):=||min(az

(k)

+q,z

(k)

)||2小于等于给定的一个常数,此时可认 为迭代序列收敛,该求解过程可描述为:

[0076][0077]

且

[0078][0079]

对于公式(24),可以采用cholesky分解或者lu分解等直接法进行求解,也采用共轭 梯度法进行近似求解;本发明中,取ω=ωi,选取的m1,n1,m2,n2如下所示:

[0080][0081][0082]

其中,β,θ为正常数,f=tridiag(w(b+λr

t

r)-1wt

)是矩阵a的舒尔补矩阵 w(b+λr

t

r)-1wt

的三对角矩阵。由于矩阵求逆需要耗费大量时间,本发明应用sherman

‑ꢀ

morrison公式简化求逆计算;因为rr

t

是一个由对角线元素均为2构成的对角矩阵,且b 为单位矩阵,那么(b+λr

t

r)-1

可用如下等式表示:

[0083][0084]

因此,具体求解过程如图3所示。

[0085]

s6:将多倍行高标准单元分割成的子单元的x坐标进行统一,并对齐到行中的可放置 位上;

[0086]

将每个多倍行高标准单元的所有子单元的x坐标按照升序排序,中位数即为所求的该 多倍行高单元的x坐标,接着将单元放置到离所求得的x坐标最近的可放置位上。

[0087]

s7:对剩余的非法单元进行合法化处理;

[0088]

针对少许仍然重叠或超出布局区域右边界的标准单元,从布局区域右上角开始,按照 从右到左,从上到下的顺序对标准单元进行遍历,若单元ci超过右边界,则把其坐标

置为 w-wi,若单元ci与c

i-1

重叠,则将c

i-1

坐标置为x

i-w

i-1

;由于多倍行高单元的移动可能会 引起相邻行的单元重叠,因此,对于在上一行中已经移动过的多倍行高单元,在下一行则 不再移动它们。接着,按照相同的规则从左到右,从下到上的顺序遍历再次遍历标准单 元,经过该步骤处理后,所有单元重叠均可消除。

[0089]

以上所述仅为本发明的示例性实施例,并非因此限制本发明专利保护范围,凡是利用 本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关 的技术领域,均同理包括在本发明的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1