集成电路数字后端ECO方法、系统及计算机存储介质与流程

集成电路数字后端eco方法、系统及计算机存储介质

技术领域

1.本发明属于集成电路设计行业设计自动化eda技术领域,具体涉及一种集成电路数字后端eco方法、系统及计算机存储介质。

背景技术:

2.随着集成电路规模越来越大,不少设计已经达到数百万门,尽管在流片前会经过许多逻辑分析、仿真以及fpga实测验证,但还是难以覆盖所有功能组合,流片后经常还是会发现一些功能bug,此时便需要eco(engineering change order,工程修改)来解决。eco指流片后不改变版图底层物理单元,利用一些备用单元(spare cell),仅更改金属层走线来更改连接,进而达到修复逻辑功能的目的。相比较重新流片,eco的方法周期更短也更节约成本,因此已经被广泛采用。

3.为了减少eco改动的层数,后端设计工程师通常会将备用单元的输出端口引出来,如专利jp2006237123a中所述。这样在eco时就可以避免修改原有的第一金属层(metal1)和第一过孔层(via1),保留复用原有的第一金属层和第一过孔层,以减少修改层数,达到压缩生产周期和成本的目的。

4.但是,随之而来产生的问题是,由于芯片规模不断增大,专用集成电路(asic)的功能越来越复杂,对于soc(system on chip)来说,外设数量也越来越多,或者单一外设内部的通道数量也很多,这就意味着eco也会涉及不少功能点,需要用到较多的备用单元来进行逻辑修复。而连接逻辑改变后需要对应的在物理版图上修改所涉及的对象(object)的线网名(net name),所涉及的对象包括要复用的第一金属层的金属形状(shape)及第一过孔层的过孔(via),数量众多,导致需修改线网名的对象的查找变得非常困难。现有技术均是通过人工进行查找修改,效率极低,尤其对于经常有一些过孔不是直接打在管脚上,而是通过一段甚至多段金属走线才与管脚相连的这种情况,将会更加困难,另一方面也极易造成遗漏的情况。所以当芯片规模较大,连接逻辑较复杂时,通过大量复用原有第一金属层和第一过孔层的对象来减少修改层数,将受到极大的阻碍。

技术实现要素:

5.发明目的:为了解决现有技术中,当eco逻辑较为复杂时,无法通过快速高效地完成原有第一金属层和第一过孔层的复用来减少eco过程中的修改层数,提高eco的效率,本发明提供一种集成电路数字后端eco方法、系统及计算机存储介质。

6.技术方案:一种集成电路数字后端eco方法,包括以下步骤:后端设计工具根据原设计数据库及逻辑eco后的网表,得到管脚列表及原线网名列表,管脚列表包括需要更改连接的管脚,管脚列表中的管脚与原线网名列表中的原线网名一一对应;后端设计工具根据逻辑eco后的网表,将原设计数据库中需要更改的管脚及所述管脚的更名对象的原线网名均改为新线网名,得到新设计数据库,所述更名对象包括金属

形状及过孔;将所述管脚的更名对象的原线网名改为新线网名包括:后端设计工具分别选择管脚列表中不同的管脚,根据所选管脚属性确定中心区域,执行同步更名对象环节,直至遍历所有管脚;所述同步更名对象环节包括:查找版图上与中心区域接触的且与该管脚原线网名相同的更名对象,对于查找到的金属形状,将该金属形状作为中心区域重复执行本环节,直到不再有新的更名对象出现;将所有更名对象的原线网名更改为该管脚的新线网名;后端设计工具基于新设计数据库进行eco布线。

7.进一步地,根据所选管脚属性确定中心区域的方法为:所述中心区域为矩形区域,以管脚坐标作为矩形对角坐标确定矩形区域。

8.进一步地,根据所选管脚属性确定中心区域的方法为:所述中心区域为多边形区域,以管脚边界多个点的坐标确定多边形区域。

9.进一步地,在同步更名对象环节中,若存在金属形状,且不存在过孔,则修改连接逻辑,重复执行本方法。

10.进一步地,在同步更名对象环节中,若存在多个金属形状,将所有金属形状的原线网名更改为该管脚的新线网名,再分别将每个金属形状作为中心区域重复执行本环节,直到遍历所有金属形状。

11.进一步地,查找更名对象的具体方法为:对于每次更新的中心区域,均分别查找对应的过孔;或者先查找出所有金属形状并记录,直到不再有新的金属形状出现,再统一查找所有记录的金属形状所对应的过孔。

12.进一步地,管脚列表及原线网名列表的获取方式为:将逻辑eco后的网表读入到原设计数据库中,得到需要更改连接的管脚及管脚的原连接关系,根据管脚的原连接关系得到管脚的原线网名,将需要更改连接的管脚构成管脚列表,将管脚的原线网名构成原线网名列表。

13.一种集成电路数字后端eco系统,包括:列表模块,用于根据原设计数据库及逻辑eco后的网表,建立管脚列表及原线网名列表,管脚列表包括需要更改连接的管脚,管脚列表中的管脚与原线网名列表中的原线网名一一对应;管脚及更名对象更名模块,用于根据逻辑eco后的网表更改原设计数据库中管脚的连接,将需要更改的管脚的原线网名改为新线网名;将所述管脚的更名对象的原线网名改为新线网名,得到新设计数据库,所述更名对象包括金属形状及过孔;布线模块,用于基于新设计数据库进行eco布线。

14.进一步地,将所述管脚的更名对象的原线网名改为新线网名包括:选择管脚列表中的管脚;根据所选管脚属性确定中心区域,执行同步更名对象环节,直至遍历所有管脚;所述同步更名对象环节包括:查找版图上与中心区域接触的且与该管脚原线网名相同的更名对象,对于查找到的金属形状,将该金属形状作为中心区域重复执行本环节,直到不再有新的更名对象出现;将所有更名对象的原线网名更改为该管脚的新线网名。

15.一种计算机存储介质,所述计算机存储介质上存储有计算机程序指令,所述计算机程序指令被处理器执行时实现上述集成电路数字后端eco方法。

16.本发明提供一种集成电路数字后端eco方法、系统及计算机存储介质,相比较现有技术,存在以下有益效果:不管芯片复杂与否,连接逻辑复杂与否,均能够通过快速高效地完成原有第一金属层和第一过孔层的复用来减少修改层数,至少保证第一金属层及第一过孔层无需修改,以此减少eco改动层数,提高eco的效率,辅助降低eco的成本;在eco过程中,能够准确全面地寻找需要修改线网名的对象,对其更名,不易遗漏,准确度高,尤其适合芯片比较复杂、连接逻辑较多、备用单元较多的场景;提供两种通过管脚查找第一金属形状的方案,根据后端设计工具的不同改进选择较合适的使用,满足不同需求,更加方便。

附图说明

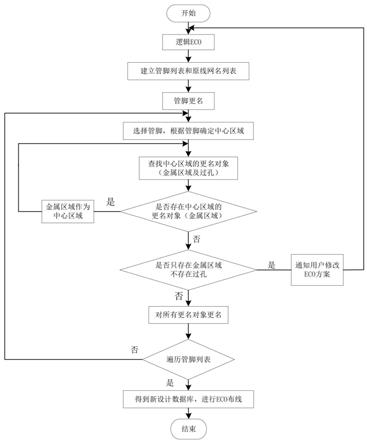

17.图1为实施例一查找更名对象的第一种情况示意图;图2为实施例一查找更名对象的第二种情况示意图;图3为实施例一查找更名对象的第三种情况示意图;图4为实施例一查找更名对象的第四种情况示意图;图5为实施例一查找更名对象的第五种情况示意图;图6为集成电路数字后端eco方法的流程图。

18.其中,管脚1、矩形区域2、过孔3、一级金属形状4、二级金属形状5、三极金属形状6。标有i或o的实线框为管脚,未标i或o的实线框为填充单元(filler)等物理单元,细虚线框为过孔,粗虚线框为根据管脚确定的中心区域。

具体实施方式

19.下面结合附图和具体实施例对本发明做进一步解释说明。

20.实施例一:本实施例提供一种集成电路数字后端eco方法,如图6,包括以下步骤:后端设计工具将逻辑eco(也叫功能eco,指逻辑关系发生了改变)后的网表读入到原设计数据库中,得到需要更改连接的管脚及管脚的原连接关系,根据管脚的原连接关系得到管脚的原线网名,将需要更改连接的管脚构成管脚列表,将管脚的原线网名构成原线网名列表,管脚列表中的管脚与原线网名列表中的原线网名一一对应,根据某管脚,就可以找到该管脚对应的原线网名;后端设计工具根据逻辑eco后的网表,将原设计数据库中需要更改的管脚及所述管脚的更名对象的原线网名均改为新线网名,得到新设计数据库,所述更名对象包括金属形状及过孔;将所述管脚的更名对象的原线网名改为新线网名包括:后端设计工具分别选择管脚列表中不同的管脚,根据所选管脚属性确定中心区域,执行同步更名对象环节,直至遍历所有管脚;如图1所示,选择管脚1,管脚1对应的原线网名为a,通过管脚1左下角坐标和右上角坐标能够确定一个矩形区域2。

21.所述同步更名对象环节包括:查找版图上与中心区域接触的且与该管脚原线网名相同的更名对象,所述更名对象包括金属形状及过孔,对于查找到的金属形状,将该金属形

状作为中心区域重复执行本环节,直到不再有新的更名对象出现;将查找到的所有更名对象的原线网名更改为该管脚的新线网名。本环节中,更名的方法可以找到一个更名对象更名一个,也可以将全部更名对象找齐后一同更名。查找更名对象的方法可以是找到一个金属形状后,随即查找金属形状相对应的过孔,图6即为这种方法,也可以将全部的金属形状(多级金属形状)均找到并记录后再统一找各级金属形状对应的过孔,此顺序不做限制。

22.为了便于描述,可以将与管脚所确定的中心区域相接触的且与该管脚原线网名相同的金属形状作为一级金属形状,与一级金属形状所确定的中心区域相接触的金属形状为二级金属形状,以此类推。可存在以下情况:1、不存在与管脚确定的中心区域相接触且与该管脚原线网名相同的一级金属形状。此情况下,必然会存在与管脚确定的中心区域相接触的且与该管脚原线网名相同的过孔,过孔可能是一个,也可能是多个,将所有该类过孔的原线网名更改为该管脚的新线网名。

23.如图1即为该情况,不存在一级金属形状,只存在过孔3。其中与矩形区域接触的另一个金属形状因原线网名为b,不属于该管脚的更名对象。

24.2、存在与管脚确定的中心区域相接触的一级金属形状,此情况下,将该一级金属形状的原线网名更改为该管脚的新线网名,继续以一级金属形状作为中心区域,查找并更名下一级金属形状,以此类推直到不存在新增更名对象为止。此情况下,可能存在过孔,也可能不存在过孔。存在的过孔可能直接与管脚确定的中心区域相接触,也可能与一级金属形状或二级金属形状等相接触,不管与谁相接触,均将过孔的原线网名改为该管脚的新线网名。若不存在过孔,表明当前管脚未通过过孔往更上层走线,而是通过第一金属层走线直接与其他管脚连接,若其他管脚的连线不能改变同时又不想改动第一金属层,只能放弃当前逻辑eco方案,修改连接逻辑后再返回步骤一重新开始。

25.如图2为存在一级金属形状4及两个过孔3(其中有两个过孔是管脚的中心区域接触的过孔,还有一个过孔是一级金属形状接触的过孔)的情况,该例中管脚1为半口形状,另外一个与管脚1的中心区域相接触的金属形状及其过孔因原线网名为b,因此不属于该管脚的更名对象。

26.如图3为存在一级金属形状4、二级金属形状5及一个过孔的情况。

27.如图4为存在一级金属形状4、二级金属形状5、三级金属形状6及一个过孔的情况。

28.如图5为存在一级金属形状4,不存在过孔的情况,此时只能通过修改逻辑eco再返回步骤一重新开始。

29.在同步更名对象环节中,某一级金属形状可能会存在多个,比如与管脚确定的中心区域相接触的一级金属形状有两个,将所有一级金属形状的原线网名更改为该管脚的新线网名,再分别将每个一级金属形状作为中心区域查找二级金属形状。实现上,可以将查找到的金属形状形成列表,遍历列表元素以获取每一个金属形状的下一级更名对象,不易遗漏。

30.其中,管脚的更名和更名对象的更名不分先后顺序,甚至是找到所有需要更名的管脚及更名对象后统一更名,只要最终实现所有需要更名的对象均完成更名即可。在现有的后端设计工具中,将逻辑eco后的网表读入原设计数据库中,即可自动实现了管脚的更名,所以若是对现有后端设计工具的基础上进行改进的话,增加将更名对象的原线网名改

为新线网名的步骤即可。如图6所示为先对管脚更名,再对更名对象更名的举例。

31.获取到新设计数据库后,后端设计工具基于新设计数据库进行eco布线。

32.本实施例提供一种集成电路数字后端eco系统,包括列表模块、管脚更名模块、同步更名对象模块、布线模块:列表模块,用于根据原设计数据库及逻辑eco后的网表,建立管脚列表及原线网名列表,管脚列表包括需要更改连接的管脚,管脚列表中的管脚与原线网名列表中的原线网名一一对应;管脚及更名对象更名模块,用于根据逻辑eco后的网表更改原设计数据库中管脚的连接,将需要更改的管脚的原线网名改为新线网名;将所述管脚的更名对象的原线网名改为新线网名,得到新设计数据库,所述更名对象包括金属形状及过孔;将所述管脚的更名对象的原线网名改为新线网名具体包括:选择管脚列表中的管脚;根据所选管脚属性确定中心区域,执行同步更名对象环节,直至遍历所有管脚;所述同步更名对象环节包括:查找版图上与中心区域接触的且与该管脚原线网名相同的更名对象,对于查找到的金属形状,将该金属形状的原线网名更改为该管脚的新线网名,并将该金属形状作为中心区域重复执行本环节,直到不再有新的更名对象出现;对于查找到的过孔,将过孔的原线网名更改为该管脚的新线网名;布线模块,用于基于新设计数据库进行eco布线。

33.其中对于管脚及更名对象更名模块,在现有后端设计工具中,本身已经包含管脚更名模块,即将逻辑eco后的网表读入原设计数据库即可自动实现管脚的更名,在此基础上,可另外增加更名对象更名模块,实现更名对象的更名。

34.本实施例提供一种计算机存储介质,所述计算机存储介质上存储有计算机程序指令,所述计算机程序指令被处理器执行时实现上述的集成电路数字后端eco方法。

35.实施例二:实施例二与实施例一相比,区别在于,实施例二提供的集成电路数字后端eco方法中,步骤三,根据管脚属性确定中心区域,中心区域为多边形区域,所述多边形区域根据管脚边界很多个点的坐标确定,所确定的多边形区域就是管脚所在的区域。

36.此处简单说明提供这两种实施例的理由,实施例一采用管脚两个对角的坐标点确定矩形区域,为直接采用现有设计工具确定管脚位置的方法,使得实施例一中的后端设计工具可以尽可能延续现有设计工具,在此基础上新增其他部分功能,原有功能不做修改。而实施例二作为全新设计的后端设计工具,将通过管脚查找一级金属形状的方式也改为后续通过一级金属形状查找二级金属形状的方式,使其查找更加精准,提高准确度,提高eco成功率。因此,在实现eda技术时,可根据需要选择实施例一或实施例二。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1