一种基于RISC-V内核的微控制器的调试系统的制作方法

一种基于risc-v内核的微控制器的调试系统

技术领域

1.本发明涉及微控制器调试技术领域,尤其涉及一种基于risc-v内核的微控制器的调试系统。

背景技术:

2.复杂的片上芯片系统(soc)一般要求在芯片内集成调试系统,用来控制和监控硅后测试的内部行为。调试系统已经成为芯片上系统(soc)开发的一个重要组成部分,考虑到其在测试阶段的影响,以降低复杂性。调试系统必须提供可实际观测的soc,以便与其不同的系统进行通信。这种可观测性对于可配置的soc电路,可以提取电路中的信息。可观察性有利于在硅后验证期间的校验过程中提供便利。另一个预期的特性是运行控制,它允许控制soc中的操作,加快了soc的应用程序开发。除了控制和观察soc外,调试系统还必须监控和分析集成系统的活动。

3.soc调试可以分为软件调试和硬件调试。

4.目前业界主要存在两种soc硬件调试系统。一种是arm开发的基于jtag调试系统,其调试原理参阅:

5.https://developer.arm.com/documentation/102551/0100/manually-configuring-a-platform-configuration-for-debug;

6.一种是gaisler实验室开发的基于uart串口的调试支持模块dsu(debugger support units),其调试原理参阅:

7.https://www.gaisler.com/doc/grmon2.pdf;

8.综合上述,对于现有的调试系统关于如何监视以及分析soc活动的细节很少,为此,我们提出了本发明的一种基于risc-v内核的微控制器的调试系统,本发明是非侵入的,支持jtag调试,具有一个灵活的事务过滤功能和执行分析功能。

技术实现要素:

9.本发明的目的是提供一种基于risc-v内核的微控制器的调试系统,用于解决现有技术问题:无法全面监视以及分析soc活动的细节。

10.为了实现上述目的,本发明采用了如下技术方案:

11.一种基于risc-v内核的微控制器的调试系统,包括以下模块:

12.jtag-tap模块、调试模块和总线监视器;

13.所述jtag-tap模块包括jtag通信模块和tap测试访问端口,且所述tap测试访问端口中包括一数据寄存器;jtag通信模块将调试指令并行的存储在tap测试访问端口的数据寄存器中,并将此信息发送给调试模块;

14.所述调试模块用于管理所述总线监视器的设置和数据提取,所述调试模块管理还包括一ahb系统总线的主要接口,所述主接口提供soc的可观测性,且允许访问和修改连接到ahb系统的主总线和外围设备总线的不同外围设备的配置;

15.所述总线监视器捕获ahb系统总线事务、过滤事务,并分析性能。

16.进一步优选的,所述jtag通信模块采用ieee1149.1-2013标准进行jtag通信。

17.进一步优选的,所述调试指令包括:与调试控制寄存器、数据和操作的地址关联的信息。

18.进一步优选的,所述jtag-tap模块还包括一些边界扫描寄存器,用于控制输入和输出。

19.进一步优选的,所述总线监视器过滤事务阶段允许根据主id、从属地址、操作类型、已发送的数据或这些参数的组合来选择特定的ahb事务。

20.进一步优选的,所述总线监视器分析性能阶段,记录成功的事务、读/写事务及其延迟。

21.本发明至少具备以下有益效果:

22.本发明通过jtag-tap模块、调试模块和总线监视器的设置,能有效提高监视和分析能力,且通过总线监视器的捕获和分析阶段设置,能有效在过滤阶段之后对soc活动进行行为分析。

附图说明

23.为了更清楚地说明本发明实施例技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

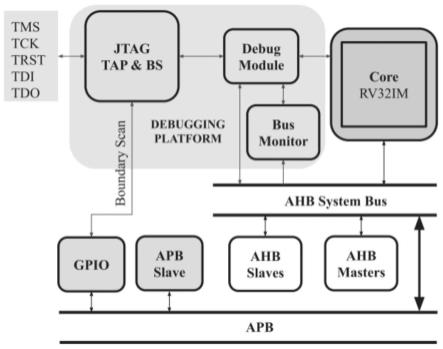

24.图1为与soc连接的调试系统的简化方框图;

25.图2为jtag结构方框图;

26.图3为调试平台支持的运行模式和指令示意图。

具体实施方式

27.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

28.调试系统已经成为芯片上系统(soc)开发的一个重要组成部分,考虑到其在测试阶段的影响,以降低复杂性。调试系统必须提供可实际观测的soc,以便与其不同的系统进行通信。这种可观测性对于可配置的soc电路,可以提取电路中的信息。可观察性有利于在硅后验证期间的校验过程中提供便利。另一个预期的特性是运行控制,它允许控制soc中的操作,加快了soc的应用程序开发。除了控制和观察soc外,调试系统还必须监控和分析集成系统的活动。

29.监视和分析能力通常不是调试系统中包含的一个因素。报告的工作显示了可控性和可观测性是如何与核心控制和联系相关联的。该分析能力与使用系统总线进行的非侵入性操作有关。这种特性允许调试系统捕获和分析soc内部执行的不同操作。必须向此特性中添加一个灵活性特性,以便对soc活动执行特定的或通用的分析。调试系统的报告通常不对系统提供这种特性。如何获取运行在总线上的事件的配置信息的细节也一直是稀缺的。此外,这个过滤阶段之后必须有一个对soc活动进行行为分析的阶段。

30.为此,在本实施例中,提出了一种应用于集成到基于risc-v的32位微控制器(mcu)中的调试平台。

31.本发明所提出的调试平台为soc的后硅验证提供了可控性、可观察性和分析能力。本平台通过操作系统核心来提供可控性。通过将平台作为系统总线主机连接来获得可观测性。最后,该平台监控系统总线活动,提供分析能力。为了执行上述操作,所实现的平台有三个主要模块,如图1所示。这些模块如下:

32.(1)jtag-tap

33.具体参阅图2,本平台采用ieee1149.1-2013标准(具体参阅文献:ieee standard for test access port and boundary-scan architecture,”ieee std 1149.1-2013(revision of ieee std 1149.1-2001),pp.1

–

444,may 2013.)进行jtag通信,该标准要求调试的指令并行的存储在测试访问端口(tap)的数据寄存器当中。调试指令包含与调试控制寄存器、数据和操作(写、读或空)的地址关联的信息。jtag将此信息发送到一个名为调试模块(dm)的中央调试系统,其中所有操作都通过寄存器进行控制。在tap中实现了一个状态寄存器,以显示在dm中执行的操作的状态。此外,jtag采用了一个边界扫描寄存器来控制输入和输出。

34.(2)debug模块

35.参阅图3,调试模块(dm)提供了soc的可控性、可观察性和分析能力。图2显示了dm有三种操作类型的调试平台的操作模式。可控性主要集中在核心调试上。在这个操作类型中,可以执行三个指令:停止命令,重置命令,并运行存储在dm命名程序缓冲区(pb)中的保留内存空间中的程序。

36.dm有一个ahb系统总线(ahb总线协议请参阅文献:arm,amba specification(rev 2.0),1999)的主要接口,提供soc的可观测性。该接口允许访问和修改连接到系统的主总线和外围设备总线的不同外围设备的配置。另一方面,dm负责管理该总线监视器的设置和数据提取。

37.(3)总线监视器

38.总线监视器捕获系统总线事务、过滤事务,并分析性能。总线监控器分为两个阶段:过滤阶段和分析阶段。过滤阶段允许根据主id、从属地址、操作类型(w/r)、已发送的数据或这些参数的组合来选择特定的ahb事务。通过过滤阶段的总线事务将被发送到分析阶段。分析阶段记录成功的事务、读/写事务及其延迟。延迟的测量范围为时钟周期(例如范围0:1至5个时钟周期)。分析阶段是基于性能计数器和解码逻辑。关于总线监视器的信息由dm提取。

39.以上显示和描述了本发明的基本原理、主要特征和本发明的优点。本行业的技术人员应该了解,本发明不受上述实施例的限制,上述实施例和说明书中描述的只是本发明的原理,在不脱离本发明精神和范围的前提下本发明还会有各种变化和改进,这些变化和改进都落入要求保护的本发明的范围内。本发明要求的保护范围由所附的权利要求书及其等同物界定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1