一种基于网络编码的RAM利用率提升方法

一种基于网络编码的ram利用率提升方法

技术领域

1.本发明属于计算机和集成电路领域,特别涉及一种基于网络编码的ram利用率提升方法。

背景技术:

2.随着科技的进步,集成电路中的ram正朝两个重要方向发展。一是随着集成电路特征尺寸的缩小和低功耗要求,单个ram单元的面积越来越小,工作电压越来越低。这就使得ram单元越来越敏感。另一个是随着人们对性能和应用越来越高的需求,ram的容量越来越大。随着集成电路规模的增大和集成度的提高,系统所需的ram的数量越来越多。在典型应用的soc芯片中,ram已经占到总芯片面积的30%以上,甚至更高。在集成电路的生产过程中,由于加工工艺、超净间尘埃等影响,在ram中会产生一些缺陷,特别是在纳米工艺下。由于缺陷的存在,ram中的有些单元将无法利用。在某些有尘埃颗粒的地方,会引起多个ram单元的功能缺陷。针对ram中的缺陷,一般采用两种解决方法:

3.(1)禁用缺陷word:一般采用的方法是在一个word中发现有一个缺陷,将会把整个word禁用。优点:简单,易于实现。缺点:由于禁用了不少word中可以正常使用的ram单元,ram的利用率不高。例如一个32bits的word,里面只有一个bit cell有缺陷,将会禁用整个32bits的word。

4.(2)传统纠错码。优点:由于通过纠错码引入了纠错能力,一些存在缺陷的word也可以使用,提升了ram的利用率。缺点:纠错码会引入额外的冗余位,而且由于纠错码本身的运算逻辑复杂,会引入不小的面积开销和延迟。

技术实现要素:

5.本发明的目的在于克服现有技术的不足,提供一种基于异或操作和选择操作,运算简单高效,不仅无需占用太多的硬件资源,而且不会引入太多的延迟信息,可以直接嵌入到ram控制中,提升ram的利用率和容错性的基于网络编码的ram利用率提升方法。

6.本发明的目的是通过以下技术方案来实现的:一种基于网络编码的ram利用率提升方法,包括以下步骤:

7.s1、交织写操作:利用交织控制位对原始数据序列进行重组,生成重组数据序列;

8.s2、编码操作:对重组后的数据序列xi进行异或操作,得到重组数据序列的网络编码位ei:

9.ei=^xi[n-1:0]

[0010]

其中^为异或运算;

[0011]

s3、ram写入:将编码后的重组数据序列xi及对应的网络编码位ei写入ram中;

[0012]

s4、ram读出:把ram写入逻辑中写入的数据读出,产生m个小序列x

′

i和产生m个对应的网络编码位e

′

i;

[0013]

s5、基于网络编码的纠错;

[0014]

s6、交织读操作:在交织控制位的控制下,对m个小序列xi进行重组生成原始数据序列x[n*m-1:0]。

[0015]

进一步地,所述步骤s1具体实现方法为:具体实现方法为:假设原始数据序列共有n*m位,编号为0~n*m-1,原始数据序列表示为x[n*m-1:0],重组后分为m个小的数据序列xi,i∈[0,m-1],重组方法为:

[0016]

xi[n-1:0]={xi[j]=x[i+j*m] j∈[0,n-1]

[0017]

或:xi[n-1:0]={xi[j]=x[j+i*m] j∈[0,n-1]。

[0018]

进一步地,所述步骤s5具体实现方法为:假设错误位置位为k,含错误的数据位为x

′

i[n-1:0],i∈[0,m-1],则纠错过程为:

[0019][0020]

其中e

′

i为网络编码位,xi[n-1∶0]为正确的数据位,得到m个小序列xi。

[0021]

进一步地,所述数据的格式为:包含数据位、禁止位、错误位置位、网络编码位和交织控制位,其中禁止位标识前面的数据位可用与否;错误位置位用来指定前面的数据位中错误数据的位置,错误数据的位置位通过数据位测量获得;网络编码位为基于网络编码所产生的冗余位;交织控制位用来实现数据序列重组。

[0022]

本发明所提出的方法的有益效果主要表现在两个方面:(1)由于加入网络编码的纠错功能,相对于禁用缺陷word,本技术方案在可接受的开销下提升了ram本身的利用率。(2)相对于传统的纠错码,本发明的实现主要基于异或操作和选择操作,运算简单高效,不仅无需占用太多的硬件资源,而且不会引入太多的延迟信息,可以直接嵌入到ram控制中,提升ram的利用率和容错性。

附图说明

[0023]

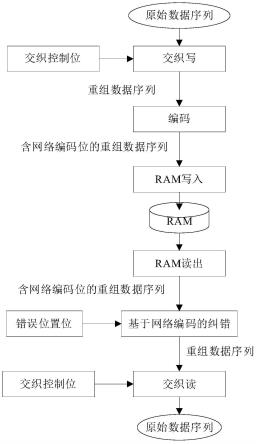

图1为本发明的基于网络编码的ram利用率提升方法的流程图;

[0024]

图2为本发明进行交织写和网络编码的流程图;

[0025]

图3为本发明进行纠错和交织读的流程图;

[0026]

图4为本发明数据序列结构图。

具体实施方式

[0027]

下面结合附图进一步说明本发明的技术方案。

[0028]

如图1所示,本发明的一种基于网络编码的ram利用率提升方法,包括以下步骤:

[0029]

s1、交织写操作:利用交织控制位对原始数据序列进行重组,生成重组数据序列;具体实现方法为:假设原始数据序列共有n*m位,编号为0~n*m-1,原始数据序列表示为x[n*m-1:0],重组后分为m个小的数据序列xi,i∈[0,m-1],重组方法为:

[0030]

xi[n-1:0]={xi[j]=x[i+j*m] j∈[0,n-1]

[0031]

或:xi[n-1:0]={xi[j]=x[j+i*m] j∈[0,n-1]

[0032]

其具体实现为选择器阵列,通过交织控制位控制选择器阵列完成数据序列的重组。

[0033]

s2、编码操作:对重组后的数据序列xi进行异或操作,得到重组数据序列的网络编

码位ei:

[0034]

ei=^xi[n-1∶0]

[0035]

其中^为异或运算。步骤s1和s2的具体流程如图2所示。

[0036]

s3、ram写入:将编码后的重组数据序列xi及对应的网络编码位ei写入ram中;

[0037]

s4、ram读出:把ram写入逻辑中写入的数据读出,产生m个小序列x

′

i和产生m个对应的网络编码位e

′

i;

[0038]

s5、基于网络编码的纠错:具体实现方法为:假设错误位置位为k,含错误的数据位为x

′

i[n-1:0],i∈[0,m-1],则纠错过程为:

[0039][0040]

其中e

′

i为网络编码位,xi[n-1:0]为正确的数据位,得到m个小序列xi。

[0041]

s6、交织读操作:在交织控制位的控制下,对m个小序列xi进行重组生成原始数据序列x[n*m-1:0]。交织读操作为交织写操作的逆过程。其具体实现为选择器阵列,通过交织控制位控制选择器阵列完成,数据序列重组。步骤s5和s6的具体流程如图3所示。

[0042]

本发明所采用的数据的格式为:包含数据位、禁止位、错误位置位、网络编码位和交织控制位,其中禁止位标识前面的数据位可用与否;错误位置位用来指定前面的数据位中错误数据的位置,错误数据的位置位通过数据位测量获得;网络编码位为基于网络编码所产生的冗余位;交织控制位用来实现数据序列重组,具体结构如图4所示。

[0043]

本领域的普通技术人员将会意识到,这里所述的实施例是为了帮助读者理解本发明的原理,应被理解为本发明的保护范围并不局限于这样的特别陈述和实施例。本领域的普通技术人员可以根据本发明公开的这些技术启示做出各种不脱离本发明实质的其它各种具体变形和组合,这些变形和组合仍然在本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1