一种概率比特单元电路、概率比特电路系统及其控制方法与流程

本技术涉及概率计算领域,尤其涉及一种概率比特单元电路、概率比特电路系统及其控制方法。

背景技术:

1、组合优化类问题越来越多的转化至伊辛模型,对伊辛模型进行退火操作求得伊辛能量最低态或近似最低态,从而得到组合优化类问题的最优解或近似最优解。比如噪声平均场伊辛退火算法。目前可以利用专用概率计算机来求解伊辛模型和组合优化类问题,而专用概率计算机可以通过概率比特电路系统来实现。其中,概率比特是指一种随时间不断在0和1两个态之间跳动的比特,其中0和1出现的概率可以由输入信号进行调控。而概率比特电路的主要实现基础为概率比特器件,比如随机磁隧道结、阻变存储器件、超导器件等。随机磁隧道结是一种具有低能量势垒的磁隧道结,在热扰动或者电流、电压激励下,随机磁隧道结的状态随时间不断在低电阻态和高电阻态二者之间跳动,因此可用于构建概率比特器件。随机磁隧道结为基础的概率比特器件可以通过改变作用在磁隧道结的电流、电压大小,从而调控低电阻态和高电阻态出现的概率。

2、目前的概率比特单元电路的结构可以如图1a所示,其包括1个晶体管,1个随机磁隧道结,1个比较器,1个电阻。基于该概率比特单元电路构成的概率比特电路系统的连接关系如图1b所示,即每个概率比特单元电路均与数模转换器(digital to analogconverter,dac)以及微控制器(micro controller)相连。在该概率比特电路系统中每个概率比特单元电路的输出被送至微控制器与待求解问题对应的权重进行乘累加运算后,将结果反馈给概率比特单元电路的输入端,进行迭代刷新。

3、在此方案中,多个概率比特单元电路分别与dac和微控制器相连,这样进行计算时各个计算结果为单独计算,从而导致计算并行度差、迭代时延长、功耗高。

技术实现思路

1、本技术提供了一种概率比特单元电路、概率比特电路系统及其控制方法,用于实现概率比特单元电路之间的相互级联,从而提高计算并行度,降低迭代时延和功耗。

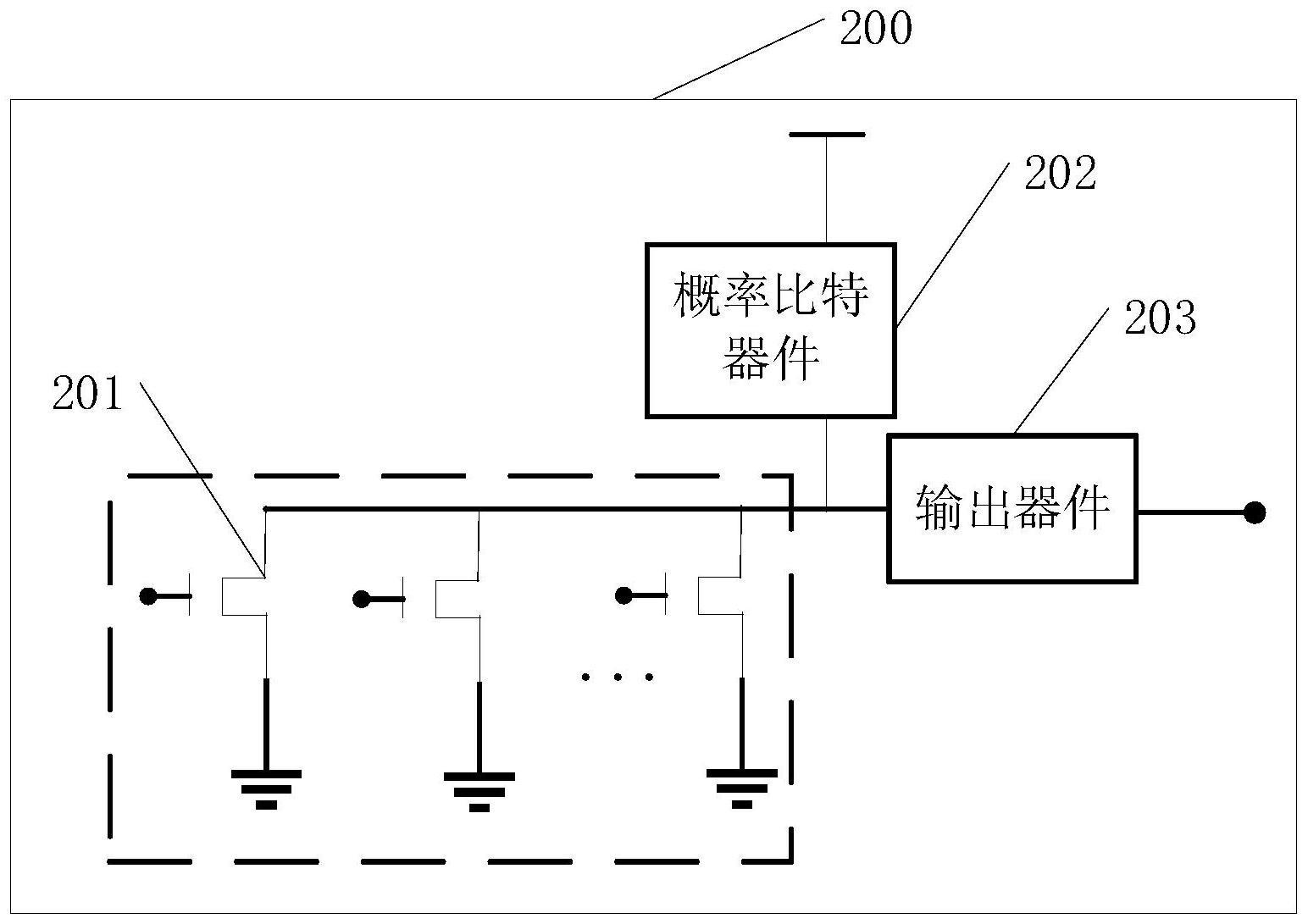

2、第一方面,本技术提供一种概率比特单元电路,其具体包括至少两个第一晶体管、概率比特器件、输出器件;其中,所述至少两个第一晶体管的栅极为所述概率比特单元电路输入端,所述输入端输入模拟信号;所述至少两个第一晶体管的源漏极中的一端与所述概率比特器件的底端以及所述输出器件的输入端相连,所述至少两个第一晶体管的源漏极中的另一端接地,所述输出器件的输出端输出数字信号。

3、可以理解的是,该至少两个第一晶体管的源漏极中的另一端也可以在与电阻相连之后再接地,即只要实现该至少两个第一晶体管的源漏极中的另一端接地即可,具体连接方式此处不再赘述。

4、本技术提供的技术方案中,该概率比特单元电路中的多个第一晶体管作为该概率比特单元电路的输入端,使得该概率比特单元电路中包括多个输入端,从而实现该概率比特单元电路之间的相互级联,进而提高计算并行度,降低迭代时延和功耗。

5、可选的,该概率比特单元电路还包括控制模块,所述控制模块与所述概率比特器件的底端相连,用于改变作用于该概率比特器件的偏置电流或者偏置电压。这样使得该概率比特单元电路具有更高的可调性。

6、可选的,所述控制模块为第二晶体管,所述第二晶体管的源漏极的一端与所述概率比特器件的底端相连,所述第二晶体管的源漏极的另一端接地;

7、或,所述控制模块包括两个第三晶体管,所述两个第三晶体管的源漏极的一端相连,所述两个第三晶体管的源漏极的另一端分别与所述概率比特器件的底部相连以及接地,所述两个第三晶体管的栅级作为所述控制模块的输入端;

8、或者,所述控制模块为电流源,所述电流源的一端与所述概率比特器件的底端相连,所述电流源的另一端接地。这样使得该概率比特单元电路中控制模块的实现方式多样化,从而减少该控制模块的实现成本。

9、可选的,所述概率比特单元电路还包括迟滞模块,所述迟滞模块与所述概率比特器件的底端相连,或位于所述至少两个第一晶体管的源漏极中的一端与所述概率比特器件的底端之间,用于减缓作用在概率比特器件上的电流或电压的变化。这样使得该概率比特单元电路构成的系统运行更加平稳,更加容易达到电路系统的稳态或目标问题的伊辛能量最低态。

10、可选的,所述迟滞模块包括电容和第四晶体管,其中所述电容的一端以及所述第四晶体管的栅极与所述至少两个第一晶体管的源漏极的一端相连,所述电容的另一端与电源电压相连,所述第四晶体管的源漏极的一端与所述概率比特器件的底端相连,所述第四晶体管的源漏极的另一端接地;

11、或者,

12、所述迟滞模块包括电容和第五晶体管,其中所述电容的一端以及所述第五晶体管的栅极与所述至少两个第一晶体管的源漏极的一端相连,所述电容的另一端与所述概率比特器件的底端相连,所述第四晶体管的源漏极的一端与所述概率比特器件的底端相连,所述第四晶体管的源漏极的另一端接地;

13、或者,

14、所述迟滞模块包括电容,所述电容的一端与所述至少两个第一晶体管的源漏极的一端相连,所述电容的另一端与电源电压相连。

15、可选的,所述概率比特器件为随机磁隧道结、阻变存储器件或超导器件。

16、可选的,所述输出器件为反相器、比较器或运算放大器。

17、第二方面,本技术提供一种概率比特电路系统,其包括n个上述第一方面所描述的概率比特单元电路,所述n为大于1的整数;所述n个概率比特单元电路通过m个连接电路进行级联生成概率比特电路系统,所述m为大于或等于所述n的整数;所述连接电路用于实现前一个概率比特单元电路的输出信号到后一个概率比特单元电路的输入信号的变换。

18、可选的,所述连接电路具有控制端,用于实现前一个概率比特单元电路的输出信号到后一个概率比特单元电路的输入信号的变换。

19、本技术提供的技术方案中,该概率比特单元电路中的多个第一晶体管作为该概率比特单元电路的输入端,从而该概率比特单元电路中包括多个输入端,从而实现该概率比特单元电路之间的相互级联,从而提高计算并行度,降低迭代时延和功耗。

20、可选的,所述n个概率比特单元电路通过m个连接电路进行级联生成概率比特电路系统包括:所述n个概率比特单元电路中的概率比特单元通过所述m个连接电路两两连接,所述m等于n*(n-1),所述n个概率比特单元电路中的每一个概率比特单元电路包括n-1个第一晶体管。即概率比特单元电路在级联时进行两两互联,实现全连接,这样增加了求解问题的广泛性和计算问题的速度。

21、可选的,所述概率比特电路系统以所述n个概率比特单元电路为一组纵向或者横向周期性扩展。即该概率比特电路系统中可以包括以一组概率比特单元电路组成的结构进行周期性的扩展,从而扩大该概率比特电路系统的规模,这样增加了求解问题的规模和广泛性。

22、可选的,本技术中,该概率比特电路系统的扩展方式可以如下:所述概率比特电路系统包括x个包括所述n个概率比特单元电路的概率比特电路模块,所述概率比特电路模块中n个概率比特单元电路两两相连,且所述x个概率比特电路模块通过概率比特单元电路相连相连,所述x为大于1的正整数。比如假设该概率比特电路系统包括2个概率比特电路模块(第一概率比特电路模块和第二概率比特电路模块),每个概率比特电路模块包括8个概率比特单元电路,则各个概率比特电路模块之间的连接可以如下:

23、一种可能实现方式中,第一概率比特电路模块中有四个概率比特单元电路与第二概率比特电路模块中的四个概率比特单元电路一一相连,同时,该第一概率比特电路模块剩下的四个概率比特单元电路与第二概率比特电路模块中的剩下的四个概率比特单元电路一一相连。

24、另一种可能实现方式中,该第一概率比特电路模块中的一个概率比特单元电路与该第二概率比特电路模块中的8个概率比特单元电路相连。

25、另一种可能实现方式中,该第一概率比特电路模块中的一个概率比特单元电路与该第二概率比特电路模块中的4个概率比特单元电路相连,该第一概率比特电路模块中的另一个概率比特单元电路与该第二概率比特电路模块中剩下的4个概率比特单元电路相连。

26、可以理解的是,只要可以实现该第一概率比特电路模块与该第二概率比特电路模块相连即可,该第一概率比特电路模块与该第二概率比特电路模块之间的连接方式不做限定。可选的,所述连接电路包括至少两个第六晶体管,所述至少两个第六晶体管的栅极并联后与所述n个概率比特单元电路的其中一个概率比特单元电路的输出端相连,所述至少两个第六晶体管的源漏极的一端相连后与所述n个概率比特单元电路的另一个概率比特单元电路的输入端相连,所述至少两个第六晶体管的源漏极的另一端作为所述连接电路的控制端。

27、可选的,所述至少两个第六晶体管中包括n型晶体管和p型晶体管。这样可以有效的设计连接电路功能。

28、第三方面,本技术提供一种概率比特电路系统的控制方法,该控制方法主要应用于上述第二方面描述的概率比特电路系统,具体包括:控制装置控制所述概率比特电路系统中的控制信号由第一组预设值逐渐调节至第二组预设值,以使得对所述概率比特电路系统进行退火操作得到输出信号;可以理解的是,该控制信号可以是连续变化,也可以是阶跃变化;在所述控制信号达到所述第二组预设值时,输出所述第二组预设值对应的输出信号。比如该概率比特电路系统具有2个控制电压,第一组预设值为(1v,1v),而该第二组预设值为(0.5v,1.5v)。控制电压可以是连续变化,如从1v连续变化到1.5v,也可以是阶跃变化,如1v、1.1v、…、1.5v。

29、本实施例中,基于该概率比特电路系统的架构,从而对该概率比特电路系统进行退火操作,这样可以更快速度的达到该概率比特电路系统对应的目标问题的伊辛能量稳态,用于求解组合优化类的问题。

30、可选的,所述概率比特电路系统的连接电路为晶体管时,所述控制所述概率比特电路系统中的控制信号对所述概率比特电路系统进行退火操作得到输出信号包括:控制所述连接电路的两个控制端电压从该第一组预设值(如(1v,1v))至第二组预设值(如(0.5v,1.5v)),对所述概率比特电路系统进行退火操作得到该输出信号。

31、第四方面,本技术提供一种概率比特电路系统的控制装置,该装置具有实现上述第三方面中控制装置行为的功能。该功能可以通过硬件实现,也可以通过硬件执行相应的软件实现。该硬件或软件包括一个或多个与上述功能相对应的模块。

32、在一个可能的实现方式中,该装置包括用于执行以上第三方面各个步骤的单元或模块。例如,该装置包括:控制模块,用于控制所述概率比特电路系统中的控制信号由第一组预设值至第二组预设值,以使得对所述概率比特电路系统进行退火操作得到输出信号;输出模块,用于在所述控制信号达到所述第二组预设值时,输出所述第二组预设值对应的输出信号。

33、可选的,还包括存储模块,用于保存控制装置必要的程序指令和数据。

34、在一种可能的实现方式中,该装置包括:处理器和收发器,该处理器被配置为支持控制装置执行上述第三方面提供的方法中相应的功能。可选的,此装置还可以包括存储器,该存储器用于与处理器耦合,其保存控制装置必要的程序指令和数据。

35、在一种可能的实现方式中,当该装置为控制装置内的芯片时,该芯片包括:处理模块和收发模块,该处理模块例如可以是处理器,此处理器用于控制所述概率比特电路系统中作用于各个概率比特器件的信号的控制信号由第一组预设值至第二组预设值,以使得对所述概率比特电路系统进行退火操作得到多组输出信号,该处理模块可执行存储单元存储的计算机执行指令,以支持控制装置执行上述第三方面提供的方法。该收发模块例如可以是该芯片上的输入/输出接口、管脚或电路等,在所述控制信号信号范围达到所述第二组预设值时,输出所述第二组预设值对应的输出信号传送给与此芯片耦合的其他芯片或模块中。可选地,该存储单元可以为该芯片内的存储单元,如寄存器、缓存等,该存储单元还可以是位于该芯片外部的存储单元,如只读存储器(read-only memory,rom)或可存储静态信息和指令的其他类型的静态存储设备,随机存取存储器(random access memory,ram)等。

36、在一种可能实现方式中,该装置包括通信接口和逻辑电路该逻辑电路,用于控制所述概率比特电路系统中的控制信号由第一组预设值至第二组预设值,以使得对所述概率比特电路系统进行退火操作得到输出信号;该通信接口,还用于在所述控制信号达到所述第二组预设值时,输出所述第二组预设值对应的输出信号。

37、其中,上述任一处提到的处理器,可以是一个通用中央处理器(centralprocessing unit,cpu),微处理器,特定应用集成电路(application-specificintegrated circuit,asic),或一个或多个用于控制上述各方面数据传输方法的程序执行的集成电路。

38、第五方面,本技术实施例提供一种计算机可读存储介质,该计算机存储介质存储有计算机指令,该计算机指令用于执行上述第四方面所述的方法。

39、第六方面,本技术实施例提供一种包含指令的计算机程序产品,当其在计算机上运行时,使得计算机指令用于执行上述第四方面所述的方法。

40、第七方面,本技术提供了一种芯片系统,该芯片系统包括处理器,用于支持控制装置实现上述方面中所涉及的功能,例如生成或处理上述方法中所涉及的数据和/或信息。在一种可能的设计中,该芯片系统还包括存储器,该存储器,用于保存控制装置必要的程序指令和数据,以实现上述各方面中任意一方面的功能。该芯片系统可以由芯片构成,也可以包含芯片和其他分立器件。

- 还没有人留言评论。精彩留言会获得点赞!