用于对电路进行仿真的方法、电子设备、计算机可读存储介质和程序产品与流程

本公开涉及硬件设计领域,更具体而言涉及用于对电路进行仿真的方法、电子设备、计算机可读存储介质和程序产品。

背景技术:

1、在集成电路(integrated circuit,ic)芯片设计领域,通常使用硬件描述语言(hardware description language,hdl)进行电路设计和描述。例如,systemverilog语言是常用的硬件描述语言之一。一些硬件描述语言描述的程序是由执行线程组成,用事件(event)来模拟集成电路中的信号或变量状态的变化。为避免在同一个时刻执行线程执行顺序的不确定性,hdl可以规定不同执行线程执行所在的域(region)。

2、用hdl描述的芯片在流片之前,需要用电子设计自动化(electronic designautomation,eda)工具对它进行完整的功能仿真。目前主要采用的仿真技术是多核并行仿真技术。商业上能够支持多核并行仿真的方案都是把事件作为基本单位进行任务分割。但是,为了确保事件的确定性执行顺序,事件之间须在每个region完成一次同步。由于在每个时隙(timeslot)内要执行多个region,这就导致了基于事件分离的任务之间调度开销和同步开销过大,使得多核并行仿真的加速效果不够理想。

技术实现思路

1、鉴于上述问题,本公开的实施例旨在提供用于对电路进行仿真的方法、电子设备、计算机可读存储介质和程序产品,其可以用于提高电路仿真的效率。

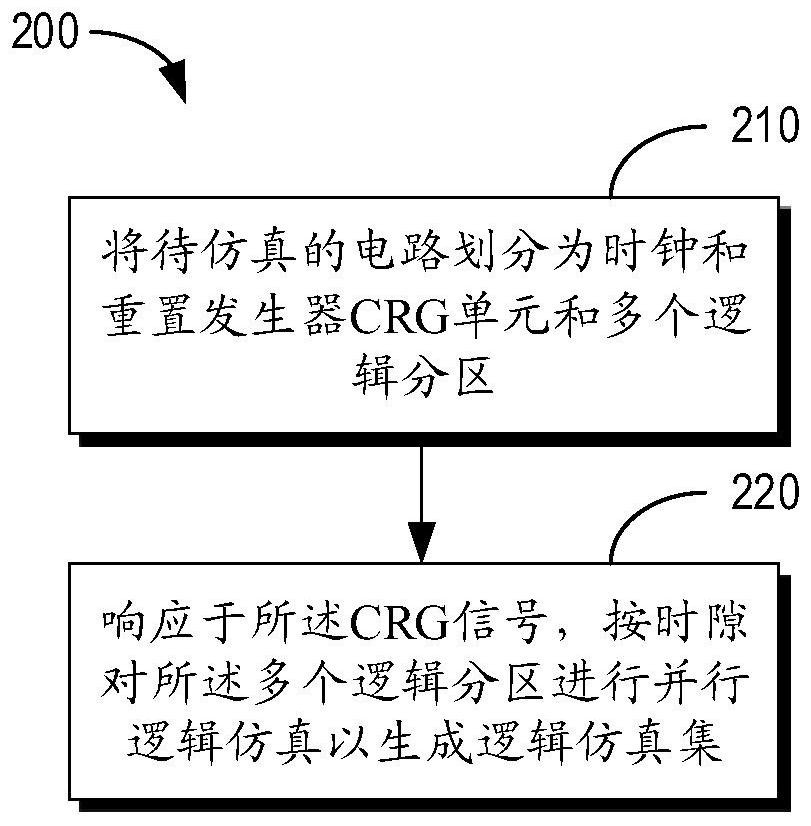

2、根据本公开的第一方面,提供一种用于对电路进行仿真的方法。该方法包括:将待仿真的电路划分为时钟和重置发生器crg单元和多个逻辑分区,crg单元被配置为发出crg信号,crg信号包括时钟信号和重置信号中的至少一项;以及响应于crg信号,按时隙对多个逻辑分区进行并行逻辑仿真以生成逻辑仿真集。由于电路被划分为crg单元和各个逻辑分区,因此各个逻辑分区在每个时隙内的寄存器逻辑进程没有数据依赖,可以按时隙对各个逻辑分区进行相互独立的仿真,而只需要在每个时隙开始时对crg单元和多个逻辑分区进行同步。相对于目前同步发生在每个region的情况,这可以减小调度开销和同步开销,从而提高仿真的效率。

3、在第一方面的一种实现方式中,响应于来自crg单元的crg信号按时隙对多个逻辑分区进行并行仿真以生成逻辑仿真集包括:在第一仿真时隙内,基于crg信号触发多个逻辑分区中的相应逻辑分区,使用来自存储器的在第二仿真时隙期间计算完成的数据来对相应分区进行并行仿真,第二仿真时隙位于第一仿真时隙之前;在第一仿真时隙内对多个逻辑分区进行并行仿真,以生成第一仿真子集并且将相应逻辑分区的逻辑仿真的第一完成状态集反馈给crg单元;以及基于第一仿真子集和第一完成状态集生成逻辑仿真集。通过上述设置,在当前时隙,只需要从存储器中读取上一时隙计算完成的数据,便可以让每个逻辑分区开始独立进行计算。因此执行线程之间同步只会发生在每个时隙的开始时刻,从而提高了仿真的效率。

4、在第一方面的一种实现方式中,多个逻辑分区中的每个逻辑分区包括多个寄存器逻辑进程,寄存器逻辑进程包括寄存器和由寄存器驱动的组合逻辑。

5、在第一方面的一种实现方式中,将待仿真的电路划分为crg单元和多个逻辑分区包括:将待仿真的电路初步划分为顶层模块和多个初始分区;指定顶层模块为crg单元;确定多个初始分区的多个输出信号是否是crg信号;响应于多个初始分区中的至少一个初始分区的输出信号是crg信号,将至少一个初始分区合并到crg单元,并且将多个初始分区中除至少一个初始分区之外的初始分区确定为多个逻辑分区。

6、在第一方面的一种实现方式中,确定多个初始分区的多个输出信号是否是crg信号包括:遍历所有多个初始分区中的功能模块的输入信号列表中的敏感信号,形成敏感信号集合;遍历所有多个初始分区以确定多个初始分区中的每个初始分区是否为另一初始分区的输入敏感信号列表;基于多个初始分区中的至少一个初始分区是否是另一初始分区的输入敏感信号列表,确定至少一个初始分区的输出信号是否是crg信号。

7、在第一方面的一种实现方式中,将多个初始分区中除至少一个初始分区之外的分区确定为多个逻辑分区还包括:构建针对待仿真的电路的模块的节点的超图;在构建超图连接关系时判断每个图边的可切分性;以及基于可切分性来确定多个逻辑分区。相对于基于事件构建超图,上述切分方式可以使图的节点数量缩减,大大降低了切分的复杂度;其次,在切分前分析每个图边的可细分性可以减少后期处理的复杂性。

8、在第一方面的一种实现方式中,将多个初始分区中除至少一个初始分区之外的分区确定为多个逻辑分区还包括:对初始分区的边界进行调整以使多个逻辑分区的负载平衡。上述调整可以进一步减小调度开销。

9、在第一方面的一种实现方式中,将多个初始分区中除至少一个初始分区之外的分区确定为多个逻辑分区还包括:响应于待仿真的电路中具有多个异步时钟,将跨异步时钟的数据流动划分在同一逻辑分区内。通过上述切分方式,使得异步时钟不会跨不同的逻辑分区,从而进一步减少了同步开销。

10、在第一方面的一种实现方式中,对多个逻辑分区进行并行逻辑仿真还包括:将待仿真的电路中的最高频时钟设为基准,将其他低频时钟的时钟沿与最高频时钟的时钟沿对齐;基于对齐后的时钟对多个逻辑分区进行并行逻辑仿真。上述设置可以实现集成电路的大部分逻辑分区在同一个调度区间之内并行仿真,从而将多个逻辑分区之间的同步次数减少到有效高频时钟沿数,多个逻辑分区之间同步的次数不会随着异步时钟数量的增加而增加,进一步提高了仿真效率。

11、在第一方面的一种实现方式中,该方法还包括:确定多个逻辑分区的数目;如果多个逻辑分区的数目不低于处理器核的数目的预定倍数,则将多个逻辑分区中相互之间具有数据交换的多个逻辑分区划分成一个组;以及优先调度同一组内的多个逻辑分区来对多个逻辑分区进行并行逻辑仿真。上述设置可以减少处理器核的空闲时间,从而进一步提高仿真的效率。

12、在第一方面的一种实现方式中,将待仿真的电路划分为时钟和重置发生器crg单元和多个逻辑分区包括:确定待仿真电路中的共有电路模块,共有电路模块被多个逻辑分区中的至少两个分区共享;以及将共有电路模块复制以将共有电路模块划分至至少两个分区。上述设置可以确保单个逻辑分区的完整性,提高了仿真的准确性。

13、在第一方面的一种实现方式中,将待仿真的电路划分为crg单元和多个逻辑分区还包括:响应于crg单元的输出不包括多个逻辑分区之间交换数据使用的时钟,在crg单元中添加伪时钟,其中伪时钟的时钟周期小于或等于crg单元和多个逻辑分区中的最短周期。

14、在第一方面的一种实现方式中,对多个逻辑分区进行并行逻辑仿真还包括:在对多个逻辑分区进行并行逻辑仿真时,在第二仿真时隙期间,控制crg单元在处理器核的空闲期间发出第一仿真时隙的crg信号。上述设置可以隐藏crg单元和多个逻辑分区之间的同步开销,从而进一步提高仿真效率。

15、根据本公开的第二方面,提供一种用于对电路进行仿真的电子设备。该电子设备包括:划分单元,被配置为将待仿真的电路划分为时钟和重置发生器crg单元和多个逻辑分区,crg单元被配置为发出crg信号,crg信号包括时钟信号和重置信号中的至少一项;以及仿真单元,被配置为响应于crg信号,按时隙对多个逻辑分区进行并行逻辑仿真以生成逻辑仿真集。由于电路被划分为crg单元和各个逻辑分区,因此各个逻辑分区在每个时隙内的寄存器逻辑进程没有数据依赖,可以按时隙对各个逻辑分区进行相互独立的仿真,而只需要在每个时隙开始时对crg单元和多个逻辑分区进行同步。相对于目前同步发生在每个region的情况,这可以减小调度开销和同步开销,从而提高仿真的效率。

16、在第二方面的一种实现方式中,划分单元被进一步配置为:在第一仿真时隙内,基于crg信号触发多个逻辑分区中的相应逻辑分区,使用来自存储器的在第二仿真时隙期间计算完成的数据来对相应分区进行并行仿真,第二仿真时隙位于第一仿真时隙之前;在第一仿真时隙内对多个逻辑分区进行并行仿真,以生成第一仿真子集并且将相应逻辑分区的逻辑仿真的第一完成状态集反馈给crg单元;以及基于第一仿真子集和第一完成状态集生成逻辑仿真集。通过上述设置,在当前时隙,只需要从存储器中读取上一时隙计算完成的数据,便可以让每个逻辑分区开始独立进行计算。因此执行线程之间同步只会发生在每个时隙的开始时刻,从而提高仿真的效率。

17、在第二方面的一种实现方式中,多个逻辑分区中的每个逻辑分区包括多个寄存器逻辑进程,寄存器逻辑进程包括寄存器和由寄存器驱动的组合逻辑。

18、在第二方面的一种实现方式中,划分单元被进一步配置为:将待仿真的电路初步划分为顶层模块和多个初始分区;指定顶层模块为crg单元;确定多个初始分区的多个输出信号是否是crg信号;响应于多个初始分区中的至少一个初始分区的输出信号是crg信号,将至少一个初始分区合并到crg单元,并且将多个初始分区中除至少一个初始分区之外的初始分区确定为多个逻辑分区。

19、在第二方面的一种实现方式中,划分单元被进一步配置为:遍历所有多个初始分区中的功能模块的输入信号列表中的敏感信号,形成敏感信号集合;遍历所有多个初始分区以确定多个初始分区中的每个初始分区是否为另一初始分区的输入敏感信号列表;基于多个初始分区中的至少一个初始分区是否是另一初始分区的输入敏感信号列表,确定至少一个初始分区的输出信号是否是crg信号。

20、在第二方面的一种实现方式中,划分单元被进一步配置为:构建针对待仿真的电路的模块的节点的超图;在构建超图连接关系时判断每个图边的可切分性;以及基于可切分性来确定多个逻辑分区。相对于基于事件构建超图,上述切分方式可以使图的节点数量缩减,大大降低了切分的复杂度;其次,在切分前分析每个图边的可细分性可以减少后期处理的复杂性。

21、在第二方面的一种实现方式中,将多个初始分区中除至少一个初始分区之外的分区确定为多个逻辑分区还包括:对初始分区的边界进行调整以使多个逻辑分区的负载平衡。上述调整可以进一步减小调度开销。

22、在第二方面的一种实现方式中,划分单元被进一步配置为:响应于待仿真的电路中具有多个异步时钟,将跨异步时钟的数据流动划分在同一逻辑分区内。通过上述切分方式,使得异步时钟不会跨不同的逻辑分区,从而进一步减少了同步开销。

23、在第二方面的一种实现方式中,仿真单元被进一步配置为:将待仿真的电路中的最高频时钟设为基准,将其他低频时钟的时钟沿与最高频时钟的时钟沿对齐;基于对齐后的时钟对多个逻辑分区进行并行逻辑仿真。上述设置可以实现集成电路的大部分逻辑分区在同一个调度区间之内并行仿真,从而将多个逻辑分区之间的同步次数减少到有效高频时钟沿数,多个逻辑分区之间同步的次数不会随着异步时钟数量的增加而增加,进一步提高了仿真效率。

24、在第二方面的一种实现方式中,确定单元被进一步配置为:确定待仿真电路中的共有电路模块,共有电路模块被多个逻辑分区中的至少两个分区共享;以及将共有电路模块复制以将共有电路模块划分至至少两个分区。上述设置可以确保单个逻辑分区的完整性,提高了仿真的准确性。

25、在第二方面的一种实现方式中,划分单元被进一步配置为:响应于crg单元的输出不包括多个逻辑分区之间交换数据使用的时钟,在crg单元中添加伪时钟,其中伪时钟的时钟周期小于或等于crg单元和多个逻辑分区中的最短周期。

26、在第二方面的一种实现方式中,仿真单元被进一步配置为:在对多个逻辑分区进行并行逻辑仿真时,在第二仿真时隙期间,控制crg单元在处理器核的空闲期间发出第一仿真时隙的crg信号。上述设置可以隐藏crg单元和多个逻辑分区之间的同步开销,从而进一步提高仿真效率。

27、在第二方面的一种实现方式中,该电子设备还包括:确定单元,被配置为确定多个逻辑分区的数目;如果多个逻辑分区的数目不低于处理器核的数目的预定倍数,则将多个逻辑分区中相互之间具有数据交换的多个逻辑分区划分成一个组;以及优先调度同一组内的多个逻辑分区来对多个逻辑分区进行并行逻辑仿真。

28、在本公开的第三方面,提供一种电子设备。该电子设备包括:至少一个处理器;至少一个存储器,至少一个存储器被耦合到至少一个处理器,并且存储用于由至少一个处理器执行的指令,指令当由至少一个处理器执行时,使得设备执行根据第一方面的方法。

29、在本公开的第四方面,提供一种计算机可读存储介质。该计算机可读存储介质存储有计算机程序,计算机程序被处理器执行时实现根据第一方面的方法。

30、在本公开的第五方面,提供一种计算机程序产品。该计算机程序产品包括计算机可执行指令,计算机可执行指令在被处理器执行时,使计算机实现根据第一方面的方法。

31、应当理解,

技术实现要素:

部分中所描述的内容并非旨在限定本公开的实施例的关键或重要特征,亦非用于限制本公开的范围。本公开的其它特征将通过以下的描述变得容易理解。

- 还没有人留言评论。精彩留言会获得点赞!