一种多功能性使能管脚的控制系统及方法与流程

1.本发明涉及一种芯片设计领域,具体为一种多功能性使能管脚的控制系统及方法。

背景技术:

2.目前在手机、平板电脑、个人计算机等众多移动电子设备中,集合了多种芯片,为了实现更好的管控,很多芯片的开关受控于cpu,目前的芯片设计有如下不足:首先,通常芯片的使能功能和复位功能都是单独占用一个管脚,且管脚都需要片外额外提供rc才能实现相对较好的鲁棒性;其次,受控芯片多数是数模混合的soc芯片,需要对数字系统(如寄存器、flash等)断电前进行预保护,同时,为了满足应用场景和测试需求,也需要额外提供一个复位管脚,用以芯片逻辑异常状态的恢复;最后,芯片系统在断电后,还存在内部器件的功耗问题。

3.现有技术已经不能满足现阶段人们的需求,基于现状,急需对现有技术进行改革。

技术实现要素:

4.本发明的目的在于提供一种多功能性使能管脚的控制系统及方法,以解决上述背景技术中提出的问题。

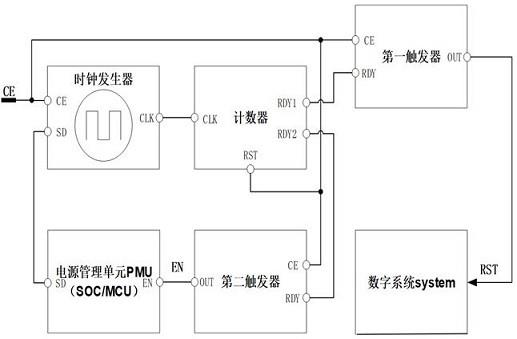

5.一方面,本发明提供如下技术方案一种多功能性使能管脚的控制系统,系统包括:时钟发生器、计数器、第一触发器、第二触发器、soc或mcu中的电源管理单元pmu和数字系统system。

6.所述时钟发生器的输入端耦接一外部管脚ce,且该外部管脚ce耦接第一触发器和第二触发器,所述时钟发生器的输出端耦接计数器;所述外部管脚ce作为第一触发器的输入端时,所述第一触发器的输出端通过复位管脚rst控制数字系统system,所述外部管脚ce作为第二触发器的输入端时,所述第二触发器的输出端通过使能管脚en控制电源管理单元pmu。

7.所述计数器具有两路输出端rdy1和rdy2,其中rdy1耦接第一触发器,且rdy2耦接第二触发器,所述计数器还具有一复位管脚rst,该复位管脚rst分别耦接第一触发器和第二触发器的ce端。

8.所述第一触发器的输出端耦接数字系统system的复位端,所述第二触发器的输出端耦接电源管理单元pmu的使能端,且电源管理单元pmu的sd端耦接时钟发生器的sd端。

9.另一方面,本发明提供如下技术方案:一种用于实现所述第一方面的多功能性使能管脚的控制方法,具体的步骤包括:待芯片系统打开时,将芯片外部管脚ce由低电压变为高电压,时钟发生器不工作,且计数器被复位,第一触发器和第二触发器分别保持复位管脚rst和使能管脚en同外部管脚ce一样由低电压变为高电压。

10.待芯片系统关闭时,将芯片外部管脚ce由高电压变为低电压,时钟发生器开始工

作,计数器通过复位管脚rst复位释放开始计时,且第一触发器和第二触发器分别保持复位管脚rst和使能管脚en维持在高电压状态。

11.待计时到t1-t2的时间后,将复位管脚rst由高电压变为低电压,使能管脚en仍然维持高电压,在t2时间内,数字系统system对其内部的寄存器、flash等模块进行复位或保护,从而实现了电源管理单元pmu断电前对数字系统system的预保护,其中,t1-t2时间是提高芯片鲁棒性的保护时间;t2是电源管理单元pmu断电前的数字系统保护时间。

12.本发明通过耦接外部管脚ce整合了原芯片系统中的使能管脚和复位管脚,实现了在无需片外器件的前提下,将使能和复位功能集合于外部管脚ce,不但提高了使能管脚的鲁棒性,而且节省了管脚外部的元器件;本发明通过数字系统system对其内部的寄存器、flash等模块进行复位或保护,从而实现了电源管理单元pmu断电前对数字系统的预保护,并且在整个芯片系统断电后,且电源管理单元pmu通过sd管脚关闭时钟发生器,实现整个芯片系统的零功耗。

附图说明

13.图1为本发明结构框图示意图;图2为本发明芯片系统打开和关闭的时序图;图3为本发明芯片系统复位的时序图;图4为本发明外部管脚ce防误触发的高鲁棒性时序图;图5为本发明时钟发生器电路的示意图;图6为本发明计数器电路的示意图;图7为本发明第一触发器和第二触发器的电路示意图。

具体实施方式

14.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

15.参考图1,一方面,本发明提供如下技术方案:一种多功能性使能管脚的控制系统,其控制系统包括时钟发生器、计数器、第一触发器、第二触发器以及soc或mcu中包括的电源管理单元pmu和数字系统system。

16.其中,时钟发生器的输入端耦接一外部管脚ce,第一触发器和第一触发器均具有ce输入端和rdy输入端,且外部管脚ce耦接到第一触发器的ce输入端和第二触发器的ce输入端,时钟发生器clk的输出端耦接计数器。

17.其中,计数器具有两路输出端rdy1和rdy2,其中rdy1耦接第一触发器的rdy输入端,且rdy2耦接第二触发器的rdy输入端,该计数器还具有一复位管脚rst,该复位管脚rst分别耦接第一触发器和第二触发器的ce输入端。

18.第一触发器的输出端耦接数字系统system的复位端,第二触发器的输出端耦接电源管理单元pmu的使能端,且电源管理单元pmu的sd端耦接时钟发生器的sd端。

19.本发明通过耦接外部管脚ce整合了原芯片系统中的使能管脚和复位管脚,当外部

管脚ce作为第一触发器的输入端时,第一触发器的输出端通过复位管脚rst控制数字系统system,当外部管脚ce作为第二触发器的输入端时,第二触发器的输出端通过使能管脚en控制电源管理单元pmu。实现了在无需片外器件的前提下,将使能和复位功能集合于外部管脚ce,不但提高了使能管脚的鲁棒性,而且节省了管脚外部的元器件。

20.参考图5、图6和图7,本发明还公开了一具体实施例,上述的时钟发生器、计数器、第一触发器、第二触发器可以由多种相同功能的电路实现,本实施例公开的时钟发生器电路,由电流源、充放电电容c1、nmos开关管q2和比较器组成,整个闭环是一个负反馈,初始状态c1的电压为零,n1关闭;电流源ib给电容c1充电,比较器comp负输入端逐渐升高,当高于comp正端电压ref,n1打开;comp的正端电压被拉低,n1再次关闭,ib再次给c1充电,如此往复,产生时钟。本实施例公开的计数器电路,由n组d触发器级联构成,计数个数为 ,其中rdy1和rdy2相差 ,且rdy1和rdy2计数的个数不唯一,rdy1和rdy2可以根据实际需要选择计数个数。本实施例公开的第一触发器和第二触发器均为具有相同功能由或非门组成的一种rs触发器,其真值表如表1所示:表1:rs触发器真值表;另一方面,本发明提供如下技术方案:一种用于实现第一方面的多功能性使能管脚的控制方法,用于实现电源管理单元pmu断电前对数字系统system的预保护和整个芯片系统的零功耗。

21.参考图2,待芯片系统打开时,将芯片外部管脚ce由低电压变为高电压,时钟发生器不工作,且计数器被复位,第一触发器和第二触发器分别保持复位管脚rst和使能管脚en同外部管脚ce一样由低电压变为高电压。第一触发器的输出端通过复位管脚rst控制数字系统system工作,且第二触发器的输出端通过使能管脚en控制电源管理单元pmu工作;待芯片系统关闭时,将芯片外部管脚ce由高电压变为低电压,时钟发生器开始工作,计数器通过复位管脚rst复位释放开始计时,且第一触发器和第二触发器分别保持复位管脚rst和使能管脚en维持在高电压状态;待计时到t1-t2的时间后,将复位管脚rst由高电压变为低电压,在t2时间内,数字系统system对其内部的寄存器、flash等模块进行复位或保护,从而实现了电源管理单元pmu断电前对数字系统的的预保护,其中,t1是芯片断电的延迟时间,t1-t2时间是提高芯片鲁棒性的保护时间;t2是电源管理单元pmu断电前的数字系统保护时间。

22.本发明还公开了另一具体实施例,待计时到t1后,使能管脚en由高电压变为低电压,此时,电源管理单元pmu关闭,整个芯片系统断电;且电源管理单元pmu通过sd管脚关闭时钟发生器,实现整个芯片系统的零功耗。

23.参考图3,本发明还公开了另一具体实施例:芯片复位的应用,将外部管脚ce由高电压变为低电压后,且低电压状态的维持的时间大于t1-t2且小于t1,这样复位管脚rst会从高电压变为低电压,用于系统复位或flash保护等中断,且使能管脚en始终维持高电压状态,使得芯片内部并未断电。

24.参考图4,本发明还公开了另一具体实施例:将外部管脚ce由高电压变为低电压,但低电压的维持的时间小于t1-t2,则使能管脚en和复位管脚rst时钟不变,芯片复位被误触发,但是系统不会被复位和断电。

25.尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1