一种加速NVMeSSDTrim的方法及系统与流程

一种加速nvme ssd trim的方法及系统

技术领域

1.本发明涉及存储领域,具体是一种加速nvme ssd trim的方法及系统。

背景技术:

2.nvme ssd是遵循非易失性内存主机控制器接口规范(non-volatile memory express)的固态驱动器(solid state disk)。ssd由控制器和存储器组成。一个优秀的nvme ssd的控制器,能够充分利用pcie通道的低延时以及并行性,在可控制的存储成本下,极大地提升固态硬盘的读写性能,降低由于ahci接口带来的高延时,彻底解放stat时代固态硬盘的极致性能。

3.在nvme ssd和host的交互中,dataset management命令是host下发的一种用于数据trim的io命令,此命令附带有lbarange,可以将某段或某几段lba 进行trim操作,被trim的lba会被标记为无效,从而可以进行垃圾回收。但是在host下发的lba range中,可能存在诸多相互交叠的lba range,在fw处理这些lba range时,造成了额外的cpu负担。

技术实现要素:

4.针对现有技术的缺陷,本发明公开一种加速nvme ssd trim的方法及系统,可以在lba range有交叠的情况下,将lba range进行排序合并后,展现给固件,降低固件对dataset management命令的处理复杂度,降低对cpu的占用。

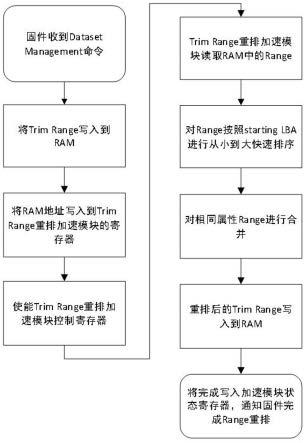

5.为了解决所述技术问题,本发明采用的技术方案是:一种加速nvme ssd trim的方法,包括以下步骤:s01)、固件收到dataset management命令,将trim range写入到ram中;s02)、固件将trim range所在的地址,写入到trim range重排加速模块的寄存器中;s03)、固件写入trim range重排加速模块的使能寄存器;s04)、trim range重排加速模块按照固件配置的地址读取ram中的trim range;s05)、trim range重排加速模块按照每个range的起始lba,对range进行排序;s06)、对排序后的range,从range0开始,到rangen检查每个range的起始lba与逻辑长度的和,查看该值是否包含了下一个range的起始lba,如果包含且属性相同,则进入步骤s07),否则重复该步骤;s07)、将该range和下一个range合并为同一个range,合并后的range,起始lba取前range的起始lba,逻辑长度取d,d=a+b-c,a表示后range的起始lba,b表示后range的逻辑长度,c表示前range的起始lba,执行步骤s04);s08)、检查下一组range,进入步骤s06);s09)、所有range检查完毕,更新trim range重排加速模块的状态寄存器,告知固件重排完成。

6.进一步的,步骤s05)中,对range进行从小到大的排序。

7.本发明还公开了一种加速nvme ssd trim的系统,包括固件、trim range重排加速模块和ram;固件用于接收dataset management命令,将trim range写入到ram中,使能trim range重排加速模块,并将trim range所在的地址写入到trim range重排加速模块的寄存器中;trim range重排加速模块包括控制寄存器、快速排序模块和合并range模块,控制寄存器接收固件写过来的trim range所在的地址并接收固件的使能信号,使trim range重排加速模块开始工作;快速排序模块读取ram中的trim range并按照每个range的起始lba,对range进行排序;合并range模块对排序后的range,从range0开始,到rangen检查每个range的起始lba与逻辑长度的和,查看该值是否包含了下一个range的起始lba,如果包含且属性相同,则将该range和下一个range合并为同一个range,合并后的range,起始lba取前range的起始lba,逻辑长度取d,d=a+b-c,a表示后range的起始lba,b表示后range的逻辑长度,c表示前range的起始lba;ram用于存储trim range并与固件、trim range重排加速模块进行交互。

8.进一步的,快速排序模块对range进行从小到大的排序。

9.本发明的有益效果:本发明在lba range有交叠的情况下,将lba range进行排序合并后,展现给固件,降低固件对dataset management命令的处理复杂度,硬件加速模块实现,也减少了固件处理trim range时带来的cpu损耗,降低对cpu的占用。

附图说明

10.图1为lba range 的结构示意图;图2为实施例1所述方法的流程图;图3为实施例2所述系统的原理框图。

具体实施方式

11.下面结合附图和具体实施例对本发明作进一步的说明。

12.实施例1本实施例公开一种加速nvme ssd trim的方法,如图1所示,lba range的结构由context attributes(属性), length in logical blocks(长度)和starting lba(起始)组成。每个每个dataset data命令可以包含多个range。range交叠时,三个lba range,rang1的starting lba(起始)位于range0的范围内,range2的starting lba(起始)位于range1的范围内。因此,交叠的lba,实际只被1个range包含就足够了。

13.本方法就是实现一种硬件合并range使其加速的方式,如图1所示,包括以下步骤:s01)、固件收到dataset management命令,将trim range写入到ram中;s02)、固件将trim range所在的地址,写入到trim range重排加速模块的寄存器中;s03)、固件写入trim range重排加速模块的使能寄存器;

s04)、trim range重排加速模块按照固件配置的地址读取ram中的trim range;s05)、trim range重排加速模块按照每个range的起始lba,对range进行从小到大的排序;s06)、对排序后的range,从range0开始,到rangen检查每个range的起始lba与逻辑长度的和,查看该值是否包含了下一个range的起始lba,如果包含且属性相同,则进入步骤s07),否则重复该步骤;s07)、将该range和下一个range合并为同一个range,合并后的range,起始lba取前range的起始lba,逻辑长度取d,d=a+b-c,a表示后range的起始lba,b表示后range的逻辑长度,c表示前range的起始lba,执行步骤s04);s08)、检查下一组range,进入步骤s06);s09)、所有range检查完毕,更新trim range重排加速模块的状态寄存器,告知固件重排完成。

14.实施例2本实施例公开一种加速nvme ssd trim的系统,如图3所示,包括固件、trim range重排加速模块和ram。

15.固件用于接收dataset management命令,将trim range写入到ram中,使能trim range重排加速模块,并将trim range所在的地址写入到trim range重排加速模块的寄存器中。

16.trim range重排加速模块包括控制寄存器、快速排序模块和合并range模块,控制寄存器接收固件写过来的trim range所在的地址并接收固件的使能信号,使trim range重排加速模块开始工作。

17.快速排序模块读取ram中的trim range并按照每个range的起始lba,对range进行从小到大的排序。

18.合并range模块对排序后的range,从range0开始,到rangen检查每个range的起始lba与逻辑长度的和,查看该值是否包含了下一个range的起始lba,如果包含且属性相同,则将该range和下一个range合并为同一个range,合并后的range,起始lba取前range的起始lba,逻辑长度取d,d=a+b-c,a表示后range的起始lba,b表示后range的逻辑长度,c表示前range的起始lba;ram用于存储trim range并与固件、trim range重排加速模块进行交互。

19.所有range检查完毕,更新trim range重排加速模块的状态寄存器,告知固件重排完成。

20.以上描述的仅是本发明的基本原理和优选实施例,本领域技术人员根据本发明做出的改进和替换,属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1