一种基于FPGA的并行超图构建方法及装置

一种基于fpga的并行超图构建方法及装置

技术领域

1.本发明属于网络分析和图论分析领域,具体涉及一种基于fpga的并行超图构建方法及装置。

背景技术:

2.在网络分析领域中,图论是一个非常强大的工具,它可以表征网络中顶点与顶点之间的关系,并可以解决各种各样的组合问题。而超图作为图概念的延伸,可以通过一条超边来包含两个以上的顶点,多条超边组成一张超图,而普通图的一条边只能连接两个顶点。相较于图而言,超图能够表征更高阶的数据信息,因而在复杂的分析任务中具备更好的性能,例如社交网络分析、数据挖掘、生物信息网络分析、图像处理等领域。

3.常用的构建超图的方法包括直接构造法以及普通图转化法。直接构造法根据目标对象之间的关系进行超图构建,关系可以是距离、相关性、属性等,构造的方法例如k最邻近(knn,k-nearest neighbor)等。这些方法仅考虑了目标顶点与邻域顶点之间的关系,而没有考虑邻域顶点之间的关系,因而超边中可能会混入并不属于超边的顶点,或者遗漏本该属于超边的点,对后续的处理造成影响。但由于其高效的计算性能,目前是最为常用的方法。

4.普通图转化法是通过算法将已经生成的普通图转化为超图的方法。通过一定关系将各个目标顶点通过二维邻接矩阵的形式进行表示,然后通过搜索的方法将二维邻接矩阵转化为超图矩阵。常用的搜索方法包括深度优先搜索(dfs,depth first search),广度优先搜索(bfs,breadth first search),以及基于这些方法开发的算法等,例如cliques算法。这些算法能很好地得到完备的超边,有助于后续的进一步处理,但是计算复杂度很高,且通常为串行计算,时间开销很大,因此并不是目前最常用的超图构造方法,但其构造的超图性能是优于直接构造法构造的超图。

5.将普通图转化法的超图计算时间复杂度降低,是一个能够提升超图结构的目标方向。可以考虑的是将串行的计算步骤转化为并行的计算,通过将时间复杂度转化到空间复杂度来降低其时间开销。已经有部分工作是将超图计算的过程通过gpu来实现,可以实现部分加速。现场可编程门阵列(fpga,field-programmable gate array)是非常适合应用于并行计算任务,并且其所有的功能均依靠硬件实现,同时具备很高的实时性,在降低运算时间开销方面具有潜力。

技术实现要素:

6.鉴于上述,本发明的目的是提供一种基于fpga的并行超图构建方法及装置,通过fpga超边的并行计算,将超边构建的时间复杂度转化到空间复杂度来降低运算时间开销,进而实现精确超图的快速构建。

7.为实现上述发明目的,本发明提供以下技术方案:

8.一种基于fpga的并行超图构建装置,包括通信连接的计算机系统和fpga;

9.所述计算机系统被配置成用于向fpga发送表示普通图的无向邻接矩阵,接收fpga发送的所有超边,并依据所有超边构建超图;

10.所述fpga被配置成用于接收无向邻接矩阵并存储后,依据无向邻接矩阵生成每个目标顶点对应的邻接顶点集合,依据邻接顶点集合并行构建每个目标顶点对应的超边,并将所有超边传输至计算机系统。

11.在一个实施例中,所述无向邻接矩阵为n*n大小的二维矩阵,二维矩阵中元素值代表顶点和顶点之间的关联信息,若第i个顶点与第j个顶点关联,则二维矩阵中第i行、第j列的值为1,反之则为0。

12.在一个实施例中,所述fpga包括数据存储模块、邻接顶点生成模块、超边计算模块、结果输出模块;

13.所述数据存储模块用于对接收的无向邻接矩阵进行存储,包括:为n*n大小的无向邻接矩阵构建一个深度为n、位宽为n的存储空间,将无向邻接矩阵的每一行作为一个二进制数据进行存储,即将每个顶点对应的那一行的二进制数据存储在一个地址空间,并标记该地址空间的地址为对应顶点;

14.所述邻接顶点生成模块用于从数据存储模块中提取存储收据,将每个顶点作为单个目标顶点,并构建每个目标顶点的邻接顶点集合;

15.所述超边计算模块用于根据n个邻接顶点集合并行构建超边;

16.所述结果输出模块用于将构建的所有超边按顺序传输至计算机系统。

17.在一个实施例的邻接顶点生成模块中,从数据存储模块中提取每个地址空间的地址以及二进制数据,其中,地址存储的顶点作为单个目标顶点,将二进制数据中目标顶点位置的数据值置0后的数据作为目标顶点的邻接顶点集合,邻接顶点集合中值为1对应的顶点为邻接顶点。

18.在一个实施例的超边计算模块中,根据n个邻接顶点集合进行首轮的并行超边构建,包括:以每个目标顶点为起始顶点,执行以下超边构建步骤:

19.首先,将起始顶点的邻接顶点集合记为avs

initial,j

,并为目标顶点初始化超边集合bc

initial,j

和备选集合ss

initial,j

,其中,bc

initial,j

和ss

initial,j

的位宽与avs

initial,j

相等,且所有数值为0;

20.然后,遍历avs

initial,j

中每个邻接顶点pi,并执行:获取邻接顶点pi的邻接顶点集合avs

adjoin,i

,将avs

adjoin,i

与当前bc

initial,j

进行与运算,当与运算结果与bc

initial,j

相等,则将bc

initial,j

中邻接顶点pi的对应位置赋值为1,以更新bc

initial,j

,否则将ss

initial,j

中邻接顶点pi的对应位置赋值为1,以更新ss

initial,j

;

21.在遍历完avs

initial,j

中所有邻接顶点,将最后更新的bc

initial,j

作为目标顶点的超边。

22.在一个实施例的超边计算模块中,在第k轮并行超边构建结束后,当ss

initial,j

中存在数值1时,进行第k+1轮的并行超边构建,包括:针对每个第k轮的avs

initial,j

,将第k轮的avs

initial,j

对应的初始顶点从无向邻接矩阵中去除,同时更新初始顶点对应的邻接顶点pi的邻接顶点集合avs

adjoin,i

,以更新后邻接顶点集合avs

adjoin,i

中每个邻接顶点pi作为第k+1轮的初始顶点,执行第k+1轮的超边构建步骤。

23.在一个实施例的结果输出模块中,将并行计算的所有超边按照轮次顺序将每轮次

构建的超边进行输出,在每个轮次内,按照初始顶点的序号顺序输出。

24.为实现上述发明目的,实施例还提供了一种基于fpga的并行超图构建方法,所述并行超图构建方法采用上述并行超图构建装置,包括以下步骤:

25.所述计算机系统向fpga发送表示普通图的无向邻接矩阵;

26.所述fpga接收无向邻接矩阵并存储后,依据无向邻接矩阵生成每个目标顶点对应的邻接顶点集合,并行依据邻接顶点集合构建每个目标顶点对应的超边,并将所有超边传输至计算机系统;

27.所述计算机系统接收fpga发送的所有超边,并依据所有超边构建超图。

28.与现有技术相比,本发明具有的有益效果至少包括:

29.基于fpga的并行处理能力和加速计算能力,在接收无向邻接矩阵并存储后,依据无向邻接矩阵生成每个目标顶点对应的邻接顶点集合,并行依据邻接顶点集合构建每个目标顶点对应的超边,在降低运算时间开销的同时,加速超图的生成。

附图说明

30.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图做简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动前提下,还可以根据这些附图获得其他附图。

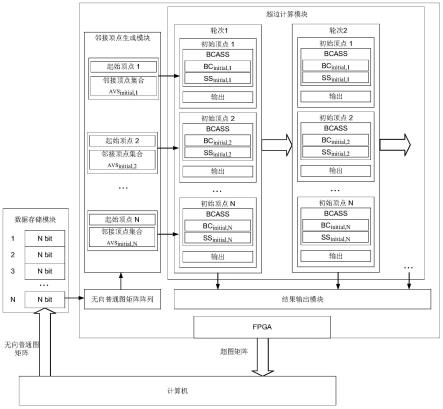

31.图1是本发明实施例提供的基于fpga的并行超图构建装置的结构示意图;

32.图2为本发明实施例提供的普通图的无向邻接矩阵构建原理图;

33.图3为本发明实施例提供的超边计算模块中生成超边的示例示意图。

具体实施方式

34.为使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例对本发明进行进一步的详细说明。应当理解,此处所描述的具体实施方式仅仅用以解释本发明,并不限定本发明的保护范围。

35.为了降低计算机系统根据普通图生成超图的计算开销,以提升计算效率,加速生成超图。实施例提供了一种基于fpga的并行超图构建方法和装置。

36.图1是本发明实施例提供的基于fpga的并行超图构建装置的结构示意图。如图1所示,实施例提供的基于fpga的并行超图构建装置包括计算机系统和fpga。

37.实施例中,计算机系统被配置成用于向fpga发送表示普通图的无向邻接矩阵和接收fpga发送的所有超边并依据所有超边构建超图。其中,无向邻接矩阵是由无向普通图转化而来,为n*n大小的二维矩阵,二维矩阵中元素值代表顶点和顶点之间的关联信息,若第i个顶点与第j个顶点关联,则二维矩阵中第i行、第j列的值为1,反之则为0。举例说明,如图2所示,左图是一张无向普通图,其中顶点1,2,3与顶点4相连。转化为无向邻接矩阵为右图,在无向邻接矩阵中,顶点与顶点相连的位置赋1,不相连的位置赋0。除此以外,矩阵对角线的值也赋1,表示顶点自身。计算机系统将转换好的无向邻接矩阵通过网络的方式发送给fpga。

38.实施例中,fpga被配置成用于接收无向邻接矩阵并存储后,依据无向邻接矩阵生

成每个目标顶点对应的邻接顶点集合,并行依据邻接顶点集合构建每个目标顶点对应的超边,并将所有超边传输至计算机系统。如图1所示,包括数据存储模块、邻接顶点生成模块、超边计算模块、结果输出模块。

39.实施例中,数据存储模块用于对接收的无向邻接矩阵进行存储,包括:为n*n大小的无向邻接矩阵构建一个深度为n、位宽为n的存储空间,将无向邻接矩阵的每一行作为一个二进制数据进行存储,即将每个顶点对应的那一行的二进制数据存储在一个地址空间,并标记该地址空间的地址为对应顶点。存储空间可以为ram空间。在后续的计算过程中将以数据存储格式进行处理。

40.实施例中,邻接顶点生成模块用于从数据存储模块中提取存储收据,将每个顶点作为单个目标顶点,并构建每个目标顶点的邻接顶点集合。具体地,从数据存储模块中提取每个地址空间的地址以及二进制数据,其中,地址存储的顶点作为单个目标顶点,将二进制数据中目标顶点位置的数据值置0后的数据作为目标顶点的邻接顶点集合,邻接顶点集合中值为1对应的顶点为邻接顶点。举例说明,例如在地址1存储空间里的二进制数为10001001,在邻接顶点生成模块中,得到的目标顶点为1,对应的邻接顶点集合为00001001。搜索过程从所有顶点开始,因此并行生成n个顶点与n个邻接顶点集合。

41.实施例中,超边计算模块用于并行根据n个邻接顶点集合构建超边。具体地,根据n个邻接顶点集合进行首轮的并行超边构建,包括:以每个目标顶点为起始顶点,执行以下超边构建步骤:

42.(a)首先,将起始顶点的邻接顶点集合记为avs

initial,j

,并为目标顶点初始化超边集合bc

initial,j

和备选集合ss

initial,j

,其中,bc

initial,j

和ss

initial,j

的位宽与avs

initial,j

相等,且所有数值为0;(b)然后,遍历avs

initial,j

中每个邻接顶点pi,并执行:获取邻接顶点pi的邻接顶点集合avs

adjoin,i

,将avs

adjoin,i

与当前bc

initial,j

进行与运算,当与运算结果与bc

initial,j

相等,则将bc

initial,j

中邻接顶点pi的对应位置赋值为1,以更新bc

initial,j

,否则将ss

initial,j

中邻接顶点pi的对应位置赋值为1,以更新ss

initial,j

;(c)在遍历完avs

initial,j

中所有邻接顶点,将最后更新的bc

initial,j

作为目标顶点的超边,其中,i为邻接顶点的索引,j为初始顶点的索引。

43.实施例中,ss

initial,j

用于判断是否终止超边计算。若ss

initial,j

中所有值均为0,则判断可以终止下轮的超边构建。当ss

initial,j

中存在数值1时,则进行下一轮并行超边构建。具体地,在超边计算模块中,在第k轮并行超边构建结束后,当ss

initial,j

中存在数值1时,进行第k+1轮的并行超边构建,包括:针对每个第k轮的avs

initial,j

,将第k轮的avs

initial,j

对应的初始顶点从无向邻接矩阵中去除,同时更新初始顶点对应的邻接顶点pi的邻接顶点集合avs

adjoin,i

,以更新后邻接顶点集合avs

adjoin,i

中每个邻接顶点pi作第k+1轮的初始顶点,执行第k+1轮的并行超边构建,即执行第k+1轮的上述步骤(a)-步骤(c)中的超边构建步骤。

44.举例说明,如图3所示,图3左侧是一张无向普通图及其无向邻接矩阵g。以顶点4为目标顶点,右侧是从目标顶点4出发,搜索得到的一条超边集合bc

target,4

。目标顶点4的avs

target,4

为001011110,需要判断值为1的顶点,即邻接顶点3,5,6,7,8是否能构成一个超边,首先从邻接顶点3开始遍历,将邻接顶点3的avs

adjoin,3

=010100011与目标顶点的bc

initial,4

=000100000进行与运算,与运算结果与bc

initial,4

=000100000相等,因此,将bc

initial,4

中对应的3号位赋1,即更新bc

initial,4

=001100000;然后遍历到邻接顶点5,邻接顶

点5的avs

adjoin,5

=000101000与目标顶点的bc

initial,4

=001100000进行与运算,与运算结果000100000与bc

initial,4

=001100000不相等,将ss

initial,4

中对应的5号位赋1,即更新ss

initial,4

=000010000;接下来遍历邻接顶点6,7,8并更新bc

initial,4

或ss

initial,4

;最后当所有邻接顶点遍历结束,得到的超边bc

initial,4

=001100010。

45.在第首轮超边构建结束后,k=1轮的ss

initial,4

=000011100,存在数值为1,则需要进行第k=2轮的并行超边构建,包括:针对每个第1轮的avs

initial,4

,将第1轮的avs

initial,4

对应的初始顶点从无向邻接矩阵中去除,同时更新初始顶点对应的邻接顶点pi的邻接顶点集合avs

adjoin,i

,假设以邻接顶点3为例,则将初始顶点4删除后,邻接顶点3更新的邻接顶点集合avs

adjoin,3

=011000011,表示邻接顶点3与顶点2、8、9具有连接关系,以更新后邻接顶点集合avs

adjoin,i

中每个邻接顶点pi作为第k+1轮的初始顶点,执行第k+1轮的超边构建步骤,假设以邻接顶点3为初始顶点例,则需要按照步骤(a)-步骤(c)计算初始顶点与对应的邻接顶点2、8、9之前的连边情况。

46.实施例中,结果输出模块用于将构建的所有超边按顺序传输至计算机系统。由于输出通道只有1个,因此,将并行计算的所有超边按照轮次顺序将每轮次构建的超边进行输出,在每个轮次内,按照初始顶点的序号顺序输出,即依次输出bc

initial,1

,bc

initial,2

,bc

initial,3

,

…

,bc

initial,n

至计算机系统。计算机系统在接收所有超边后,依据所有超边构建超图。

47.实施例还提供了一种基于fpga的并行超图构建方法,该并行超图构建方法图1所示的并行超图构建装置,包括以下步骤:

48.步骤1,计算机系统向fpga发送表示普通图的无向邻接矩阵;

49.步骤2,fpga接收无向邻接矩阵并存储后,依据无向邻接矩阵生成每个目标顶点对应的邻接顶点集合,并行依据邻接顶点集合构建每个目标顶点对应的超边,并将所有超边传输至计算机系统;

50.步骤3,计算机系统接收fpga发送的所有超边,并依据所有超边构建超图。

51.该基于fpga的并行超图构建方法与上述基于fpga的并行超图构建装置属于同一个发明构思,每个步骤的具体实现过程和效果详见并行超图构建装置,在此不再赘述。

52.上述实施例提供的基于fpga的并行超图构建方法和装置,通过fpga超边的并行计算,将超边构建的时间复杂度转化到空间复杂度来降低运算时间开销,进而实现精确超图的快速构建。

53.以上所述的具体实施方式对本发明的技术方案和有益效果进行了详细说明,应理解的是以上所述仅为本发明的最优选实施例,并不用于限制本发明,凡在本发明的原则范围内所做的任何修改、补充和等同替换等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1