一种高精准ADC的版图结构设计方法与流程

一种高精准adc的版图结构设计方法

技术领域

1.本发明涉及集成电路开发技术领域,尤其涉及一种高精准adc的版图结构设计方法。

背景技术:

2.模拟数字转换器,即a/d转换器(analog-to-digital converter),简称adc,是一种将模拟的连续信号转换为数字形式的离散信号的一类设备,广泛应用于通信领域。因高精度、低功耗的特点,sigma-delta adc在adc中脱颖而出,采用过采样、噪声整形以及数字滤波技术,降低对模拟电路的设计要求,实现了其他类型adc无法达到的高精度和低功耗。然而版图的布局连线方式直接影响sigma-delta adc的性能指标,所以为了确保sigma-delta adc的高转换精度,其版图的布局布线的要求也越来越高。一般版图布局不合理,模拟信号和数字信号相互干扰,走线繁琐,寄生电阻大,匹配性差,从而导致sigma-delta adc的性能不理想。

技术实现要素:

3.本发明提供了一种高精准adc的版图结构设计方法,尤其适用于sigma-delta adc的版图设计,实现了sigma-delta adc高精度设计。

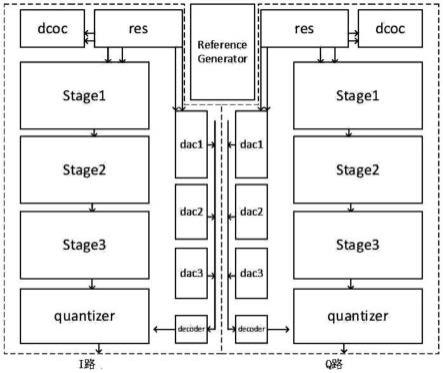

4.为了实现本发明的目的,本设计所采用的技术方案是:一种高精准adc的版图结构设计方法,adc的版图结构包括基准电流和参考电压模块reference generator、i路模块和q路模块、i路模块和q路模块采用左右对称的布局结构,基准电流和参考电压模块reference generator用于分别为i路模块和q路模块提供基准电流和参考电压模块,基准电流和参考电压模块reference generator位于i路模块版图和q路模块版图的中间。

5.作为本发明的优化方案,i路模块和q路模块均包括直流失调校准电路dcoc、抗混叠滤波器res、多级模拟sigma-delta调制器、多级数模转换器、译码器decoder和量化器quantizer,直流失调校准电路dcoc和抗混叠滤波器res位于版图的顶部,抗混叠滤波器res将滤波后的信号输送到直流失调校准电路dcoc进行直流失调校准,抗混叠滤波器res将滤波后的信号分别输送到多级模拟sigma-delta调制器和多级数模转换器,经过多级数模转换器的信号输送至译码器decoder,再经过译码器decoder后也输送至量化器quantizer;多级模拟sigma-delta调制器输出的信号也输送至量化器quantizer,最后量化器quantizer直接输出。

6.作为本发明的优化方案,多级模拟sigma-delta调制器为三级模拟sigma-delta调制器,三级模拟sigma-delta调制器包括依次串联连接的第一级模拟sigma-delta调制器stage1、第二级模拟sigma-delta调制器stage2和第三级模拟sigma-delta调制器stage3。

7.作为本发明的优化方案,第一级模拟sigma-delta调制器stage1包括电平转换器levelshift、第一电容、差分运放amp和第二电容,所述的第一电容用于隔离电平转换器levelshift和差分运放amp,所述的第二电容用于隔离差分运放amp和多级数模转换器。

8.本发明具有积极的效果:本发明i路模块和q路模块采用iq左右对称的布局结构,提高了版图的匹配性,减小工艺失配。模拟电路和数字电路信号通路简短通畅,有效的减小了走线寄生和版图的面积,巧妙地利用电容将数字电路与模拟电路隔离开来,避免模块之间的相互干扰,提高了数模电路的可靠性,从而实现sigma-delta adc高精度的设计目标。

附图说明

9.下面结合附图和具体实施方式对本发明作进一步详细的说明。

10.图1为本发明的整体版图布局结构示意图;

11.图2是本发明i路模块和q路模块的版图布局示意图;

12.图3是本发明第一级模拟sigma-delta调制器stage1的版图布局示意图。

具体实施方式

13.如图1所示,本发明公开了一种高精准adc的版图结构设计方法,adc的版图结构包括基准电流和参考电压模块reference generator、i路模块和q路模块、i路模块和q路模块采用左右对称的布局结构,基准电流和参考电压模块reference generator用于分别为i路模块和q路模块提供基准电流和参考电压模块,基准电流和参考电压模块reference generator位于i路模块版图和q路模块版图的中间。其中,i路模块和q路模块采用左右对称的布局结构,采用具有实时同步功能的group设计方式,不仅设计操作简单效率高,而且可以确保iq(i路模块和q路模块)两路版图的高度匹配性,减小了工艺失配。基准电流和参考电压模块reference generator位于i路模块版图和q路模块版图的中间,从而保证输出到iq两路的信号寄生的一致性。

14.如图2所示,i路模块和q路模块均包括直流失调校准电路dcoc、抗混叠滤波器res、多级模拟sigma-delta调制器、多级数模转换器、译码器decoder和量化器quantizer,直流失调校准电路dcoc和抗混叠滤波器res位于版图的顶部,抗混叠滤波器res将滤波后的信号输送到直流失调校准电路dcoc进行直流失调校准,抗混叠滤波器res将滤波后的信号分别输送到多级模拟sigma-delta调制器和多级数模转换器(dac1、dac2、dac3),经过多级数模转换器的信号输送至译码器decoder,再经过译码器decoder后也输送至量化器quantizer;多级模拟sigma-delta调制器输出的信号也输送至量化器quantizer,最后量化器quantizer直接输出。整体布局信号上入下出,模拟信号和数字信号沿着各自的通路向下传输,信号通路简短通畅,有效的减小了不必要的走线寄生。

15.多级模拟sigma-delta调制器为三级模拟sigma-delta调制器,三级模拟sigma-delta调制器包括依次串联连接的第一级模拟sigma-delta调制器stage1、第二级模拟sigma-delta调制器stage2和第三级模拟sigma-delta调制器stage3。

16.如图3所示,第一级模拟sigma-delta调制器stage1包括电平转换器levelshift、第一电容、差分运放amp和第二电容,第一电容用于隔离电平转换器levelshift(缩写ls)和差分运放amp,第二电容用于隔离差分运放amp和多级数模转换器。差分运放amp比较敏感,所以用电容将其与电平转换器levelshift和多级数模转换器(dac1、dac2、dac3)之间隔离开,进一步避免模块之间的相互干扰,从而有效提高了数模电路的可靠性。

17.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行了进一步详

细说明,所应理解的是,以上所述仅为本发明的具体实施例而已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1