误差校正装置及方法与流程

1.本发明涉及一种误差校正,且特别是还涉及一种误差校正装置及方法。

背景技术:

2.神经网络是人工智能(artificial intelligence,ai)中的一个重要主题,并是通过仿真人类脑细胞的运作来进行决策。值得注意的是,人类脑细胞中存在着许多神经元(neuron),而这些神经元会通过突触(synapse)来互相连结。其中,各神经元可经由突触接收讯号,且此讯号经转化后的输出会再传导到另一个神经元。各神经元的转化能力不同,且人类通过前述讯号传递与转化的运作,可形成思考与确定的能力。神经网络即是根据前述运作方式来得到对应能力。神经网络经常被应用在图像辨识中。而在各神经元的运作中,输入分量与对应突触的权重相乘(可能加上偏置)后将经非线性函数(例如,激励(activation)函数)运算而输出,从而撷取图像特征。

3.另一方面,虽然市场上已有通过模拟电路实现神经网络相关运算的加速器,但模拟电路无可避免地可能有诸如数字至模拟转换(digital-to-analog conversion,dac)偏置(offset)、放大器失真等问题,还在增益、偏置及电压上有误差。

技术实现要素:

4.本发明实施例是针对一种误差校正装置及方法,在数字上实现误差侦测及校正。

5.根据本发明的实施例,误差校正方法适用于校正机器学习加速器,且机器学习加速器利用模拟电路实现运算。误差校正方法包括(但不仅限于)下列步骤:确定神经网络中的一个或更多个运算层的输出值与对应的正确值之间的误差。这些运算层是由模拟电路实现运算。根据误差生成校正节点。校正节点位于那些运算层的下一层。校正节点用于最小化误差。校正节点是通过数字电路实现。

6.根据本发明的实施例,误差校正装置包括(但不仅限于)存储器及处理器。存储器用以存储程序代码。处理器耦接存储器。处理器经配置用以加载且执行程序代码以确定神经网络中的一个或更多个运算层的输出值与对应的正确值之间的误差,并根据误差生成校正节点。那些运算层是由模拟电路实现运算,且机器学习加速器利用这模拟电路实现运算。校正节点位于那些运算层的下一层。校正节点用于最小化误差。校正节点是通过数字电路实现。

7.基于上述,根据本发明实施例的误差校正装置及方法,基于模拟电路运算所造成的误差生成神经网络中的一个校正节点,以校正这误差,并使误差最小化。藉此,可提升系统运算效率,并改善错误率。

附图说明

8.包含附图以便进一步理解本发明,且附图并入本说明书中并构成本说明书的一部分。附图说明本发明的实施例,并与描述一起用于解释本发明的原理。

9.图1是根据本发明一实施例的系统架构图;

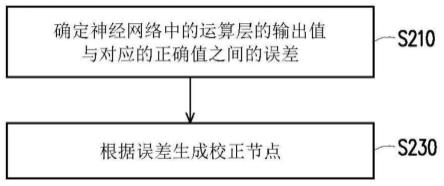

10.图2是根据本发明一实施例的误差校正方法的流程图;

11.图3是根据本发明一实施例的神经网络的示意图;

12.图4是根据本发明一实施例的增加校正节点的神经网络的示意图。

13.附图标号说明

14.50:机器学习加速器;

15.51:模拟电路;

16.100:误差校正装置;

17.110:存储器;

18.130:处理器;

19.s210~s230:步骤;

20.in:输入;

21.cl:运算层;

22.ou:输出;

23.cn:校正节点;

24.m:乘法器;

25.a:加法器。

具体实施方式

26.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同组件符号在图式和描述中用来表示相同或相似部分。

27.图1是根据本发明一实施例的系统架构图。请参照图1,这系统1包括(但不仅限于)机器学习加速器50及误差校正装置100。

28.机器学习加速器50可以是计算机系统、芯片、显示适配器、特殊应用集成电路(application-specific integrated circuit,asic)、非挥发性(nonvolatile)存储器(例如,相变半导体(phase change memory,pcm)、可变电阻式存储器(resistive ram,reram)或磁阻式随机存取存储器(magnetoresistive random access memory,mram)。机器学习加速器50可实现诸如卷积神经网络(convolutional neural network,cnn)、递归神经网络(recurrent neural network,rnn)、多层感知器(multi-layer perceptron,mlp)、支持向量机(support vector machine,svm)及/或其他算法。

29.在一实施例中,机器学习加速器501包括模拟电路51,并利用模拟电路51实现运算。这模拟电路51可能是由放大器、模拟至数字转换器(adc)、数字至模拟转换器(dac)、存储器、电阻、电容及/或其他电子组件所组成。例如,输入的数字讯号通过dac转换成多阶电压准位的模拟讯号,且模拟讯号存储于存储器中。当需要执行乘积累加运算时,可利用奥姆定律将电压数值转换成电流,并输出到adc,即实现乘积累加运算。又例如,reram的细胞位线(bit line,bl)与来源线(source line,sl)间的跨压作为输入值(例如,特征值),权重则以纵向的方式存储于存储器细胞中;细胞的电流总和可累积于电容,再将数个电容上的电压转换成数字讯号并加以运算即为乘积累加运算的结果。

30.误差校正装置100可以是桌面计算机、笔记本电脑、智能型手机、平板计算机、服务

器或其他运算装置。

31.误差校正装置100包括(但不仅限于)存储器110及处理器130。

32.存储器110可以是静态或动态随机存取存储器(random access memory,ram)、只读存储器(read-only memory,rom)、快闪存储器(flash memory)、寄存器(register)、组合逻辑电路(combinational circuit)或上述组件的组合。

33.在一实施例中,存储器110用于存储图像相关的数据、对图像进行特征撷取的乘积累加运算(multiply accumulate,mac)所用的权重、激励(activation)运算、池化(pooling)运算及/或其他神经网络运算所用的数值。在其他实施例中,应用者可根据实际需求而确定存储器110所存储数据的类型。在一实施例中,存储器110用以存储程序代码、软件模块、组态配置、数据或档案(例如,参数、误差、数值、电性特性等),并待后续实施例详述。

34.处理器130耦接存储器110。处理器130可以是由多任务器、加法器、乘法器、编码器、译码器、或各类型逻辑闸中的一者或更多者所组成的电路,并可以是中央处理单元(central processing unit,cpu)、图形处理单元(graphic processing unit,gpu),或是其他可程序化的一般用途或特殊用途的微处理器(microprocessor)、数字信号处理器(digital signal processor,dsp)、可程序化控制器、现场可程序化逻辑门阵列(field programmable gate array,fpga)、特殊应用集成电路(application-specific integrated circuit,asic)、神经网络加速器或其他类似组件或上述组件的组合。在一实施例中,处理器130经配置用以执行误差校正装置100的所有或部份作业,且可加载并执行存储器110所存储的各软件模块、程序代码、档案及数据。在一些实施例中,处理器130的运作可通过软件实现。

35.下文中,将搭配误差校正装置100中的各项组件或电路说明本发明实施例所述的方法。本方法的各个流程可依照实施情形而调整,且并不仅限于此。

36.图2是根据本发明一实施例的误差校正方法的流程图。请参照图2,处理器130确定神经网络中的一个或更多个运算层的输出值与对应的正确值之间的误差(步骤s210)。具体而言,神经网络可包括一个或更多个运算层。这运算层可能是卷积层、激励层、池化层、或其他神经网络相关层。这些运算层是由模拟电路51实现运算。

37.举例而言,图3是根据本发明一实施例的神经网络nn的示意图。请参照图3,这神经网络nn包括一个运算层cl。例如,运算层cl是卷积层。输入in(例如,张量)经运算层cl卷积运算即得到输出ou(例如,张量)。而模拟电路51实现这运算层的运算。

38.在一实施例中,处理器130可选择第1个运算层至第m个运算层的输出值,其中m为正整数。在另一实施例中,处理器120可选择第m个运算层至最后运算层的输出值。再一实施例中,处理器120可选择第m个运算层的输出值。

39.关于输出值的获得,在一实施例中,处理器130可获得模拟电路51的电性特性。电性特性相关于模拟电路51中的任一个电子组件的电压、电流、阻抗、增益、偏置、时序或其他特性。处理器130可根据这电性特性仿真模拟电路51。此外,处理器130模拟运算层的输出值。换句而言,处理器13根据电性特性估测模拟电路51将输入样本输入一个或更多个运算层后所得输出值。这输入样本可以是图像、声音、或各类型的感测值。

40.在另一实施例中,处理器130可经由输入接口接收来自机器学习加速器50的输出

值。这输入接口可以是通讯收发器(例如,基于wi-fi、以太网、或蓝芽)、传输接口(例如,usb、或i2c)或输入设备(例如,键盘、鼠标或触摸板)。当模拟电路51运作时或运作后,机器学习加速器50可检测并存储各运算层、及/或特定的一个或更多个运算层的输出值,且通过输入接口传送至误差校正装置100。

41.另一方面,正确值是经模拟得出的或已事先存储的,并是假设模拟电路51是没有任何异常(例如,错误、偏置或失真)的情况下输入样本经运算层可得出的输出值。

42.此外,来自模拟电路51的输出值或基于电性特性模拟的输出值与正确值之间的误差可通过差值、均方误差(mean square error,mse)、均方根误差(root-mean-square error,rmse)、最小均方误差(least-mean-square error,lmse)、余弦相似性、余弦距离或其他误差相关函数得出。以均方误差为例,基于电性特性模拟的输出值形成第一向量,正确值形成第二向量。处理器130可计算两向量中各对应元素的差值的平方值,并计算这些平方值的平均值。

43.请参照图2,处理器130根据输出值与正确值之间误差生成校正节点(步骤s230)。具体而言,这校正节点位于前述一个或更多个运算层的下一层。举例而言,图4是根据本发明一实施例的增加校正节点的神经网络nn的示意图。请参照图3及图4,与图3不同处在于,图4的运算层cl与输出ou之间增加校正节点cn。

44.值得注意的是,校正节点用于最小化误差。也就是说,虽然运算层的输出值与正确值之间有误差,但这输出值输入校正节点所得出的校正值与正确值之间的误差将变小甚至为零。或者,校正节点用于补偿误差。

45.在一实施例中,处理器13可根据误差确定运算组合。这运算组合是由一个或更多个运算符所形成。运算符可以是算术运算子、赋值运算符、比较运算符或其他类型的运算符。也就是说,运算组合可以是一种函数。运算组合的输出值即为误差的校正结果,且藉由输入运算层的输出值至运算组合以减少误差。也就是说,校正结果接近或等于正确值。

46.在一实施例中,处理器13可根据运算组合对应的函数形成目标函数。其中,目标函数是最小化这运算组合对应的函数与正确值的误差函数。例如,误差函数为rms误差,且rms误差数学的表示式为:

[0047][0048]

为校正节点的输出值,o

analog

为运算层的输出值,ai、bi为常数,且i、n为正整数。i代表第i类型的输入样本,n代表第n输入样本,且为第i类型的第n输入样本对应的正确值。此外,运算组合对应的函数为:

[0049][0050]

在一实施例中,运算组合包括乘法器及加法器。以图4为例,校正节点cn包括乘法器m及加法器a。即,运算层cl的输出值经乘法器m与第一值相乘再通过加法器a与第二值相加。处理器13可确定乘法器及加法器的输入值(即,第一值及第二值)。以函数(2)为例,ai为第一值,且bi为第二值。而这两值可以是前述目标函数的最佳解或任一解。

[0051]

在其他实施例中,运算组合可能是其他运算符的组合,且处理器130可基于运算组

合与正确值所形成的误差函数来得出得运算符的输入值。

[0052]

此外,校正节点是通过数字电路实现。数字电路可以是由多任务器、加法器、乘法器、编码器、译码器、或各类型逻辑闸中的一者或更多者所组成的数字形式的电路,也可以是处理器、芯片、集成电路或微控制器。或者,校正节点的功能可通过软件实现。这数字电路可嵌入在机器学习加速器51、误差校正装置100或其他外部装置或电路。由于模拟电路51仍存在电性相关错误,因此通过数字电路校正可确保误差的降低。

[0053]

在实际应用情境中,处理器130可针对机器学习加速器51的测试、出厂及/或使用阶段选择特定类型的大量输入样本,并据以确定这些输入样本合适的校正节点及其参数。例如,运算组合的运算符及其输入值。也就是说,校正节点可根据应用阶段而动态变更。

[0054]

综上所述,在本发明实施例的误差校正装置及方法中,基于模拟电路所实现运算层的输出值与正确值之间的误差确定神经网络中的校正节点,并通过数字电路实现的校正节点将运算层的输出值校正至接近或等于正确值。藉此,可补偿模拟电路中的电子组件的异常或失真。

[0055]

最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1