一种基于芯粒的2.5维集成电路的多约束阻抗优化方法

1.本发明属于集成电路技术领域,具体涉及一种基于芯粒的2.5维集成电路的多约束阻抗优化方法。

背景技术:

2.在过去十年中,集成电路小规模化的过程在逐渐放缓,因此,业内已开始寻求“超越摩尔”方案的替代解决方案,像2.5维集成电路(2.5-d ic)和3维集成电路(3-d ic)这样的芯片堆叠技术近些年发展迅速。同时,这些多芯片系统是单芯片系统(也称为2维系统)经济效益最大化的替代品,因为将一个芯片分解为多个芯片可以缓解大型2维芯片良品率低、产能不足的问题。在2.5维集成电路中,一个单独的soc(system-on-chip)被划分为多个功能模块,称为“芯粒”,再把每个芯粒集成在插入器中。芯粒之间的所有互连与信号传输都在插入器中进行。

3.目前,在2.5维集成电路中,随着数据量的增加和频率的升高,同步开关噪声对电路的影响不容忽视。降低系统阻抗是消除同步开关噪声(simultaneous switching noise,简称ssn)最有效、最直观的方法,而去耦电容器又是降低电源分配网络阻抗最方便、最有效的解决方案。在传统的板级和三维集成电路电源分配网络(power distribution network,简称pdn)工程中,有各种最优解耦设计方法,这些方法讨论了电容器的布置以降低系统阻抗。例如,h.park等人在文章“deep reinforcement learning-based optimal decoupling capacitor design method for silicon interposer-based2.5-d/3-d ics,”(doi:10.1109/tcpmt.2020.2972019.)中,s.piersanti等人在文章“decoupling capacitors placement for a multichip pdn by anature-inspired algorithm,”(doi:10.1109/temc.2017.2770089)中讨论了3维集成电路插入器和片上的去耦电容分布,i.erdin等人在文章“multi-objective optimization of decoupling capacitors for placement and component value,”(doi:10.1109/tcpmt.2019.2930565)中,j.wang等人在文章“multiport pdn optimization with the newton

–

hessian minimization method,”(doi:10.1109/tmtt.2021.3057236)中讨论了板级去耦电容器的分布。然而,由于芯粒的存在,对于2.5维集成电路,仅考虑电容器的布置则导致系统性能不佳。

技术实现要素:

4.为了解决现有技术中存在的上述问题,本发明提供了一种基于芯粒的2.5维集成电路的多约束阻抗优化方法。本发明要解决的技术问题通过以下技术方案实现:

5.一种基于芯粒的2.5维集成电路的多约束阻抗优化方法,包括以下步骤:

6.构建包含多个寄生参数的2.5维集成电路的等效电路模型,获取等效电路模型的阻抗矩阵;所述阻抗矩阵为工作频率集合γ对应的实际阻抗zf的集合;

7.根据目标阻抗z

target,f

和所述阻抗矩阵构建阻抗目标函数;所述目标阻抗z

target,f

为工作频率对应的芯粒负载侧所允许的最大自阻抗;

8.根据所述2.5维集成电路的芯粒的位置和芯粒上的端口的位置构建第一约束、第二约束和第三约束;其中,所述第一约束指示基于芯粒之间的端口之间的多个互连线的长度之和的最小化约束的约束;所述第二约束指示基于预设的互连线的最大长度约束的单根互连线长度约束;所述第三约束指示基于相邻两个芯粒之间的最小距离约束的距离约束;

9.根据所述阻抗目标函数、所述第一约束、所述第二约束和所述第三约束构建混合目标函数;

10.根据所述混合目标函数和所述等效电路模型的pdn参数确定所述混合目标函数的最小值和对应的芯粒的目标位置、插入器中的目标电容数量以及目标电容的位置。

11.在本发明的一个实施例中,所述阻抗目标函数通过公式(3)表示:

[0012][0013]

其中,ψ1表示工作频率集合γ中对应的实际阻抗zf与目标阻抗z

target,f

之差的总和,当实际阻抗zf始终小于目标阻抗z

target,f

时,ψ1=0;ψ2表示插入器中放置的去耦电容的数量;ψ3是表示阻抗矩阵中所有实际阻抗zf的总和;分别表示ψ1,ψ2,ψ3的权重系数;

[0014][0015]

ψ2=ncꢀꢀꢀ

(5)

[0016][0017]

且所述阻抗目标函数满足公式(7)-(13)的约束:

[0018][0019][0020][0021][0022][0023]cunit

≥0

ꢀꢀꢀ

(12)

[0024]

nc∈n

+

ꢀꢀꢀ

(13)

[0025]

其中,xi,yi表示第i个芯粒的中点处的坐标,xj,yj表示第j个芯粒的中点处的坐标,ai,βi表示第i个芯粒在横坐标轴方向和纵坐标轴方向的长度,aj,βj表示第j个芯粒在横坐标轴方向和纵坐标轴方向的长度,a,b表示插入器在横坐标轴方向和纵坐标轴方向的长度;c

unit

表示插入器中放置的去耦电容的电容值;n

+

表示正整数。

[0026]

在本发明的一个实施例中,所述第一约束表示为公式(14):

[0027][0028]

其中,λ1表示第一约束,表示第i个芯粒上的第p个端口和第j个芯粒上第q个端口之间的互连线的长度,q表示2.5维集成电路所有芯粒上所有端口的集合;

[0029][0030]

x

i,p

,y

i,p

表示第i个芯粒上第p个端口的坐标,x

j,q

,y

j,q

表示第j个芯粒上第q个端口的坐标。

[0031]

在本发明的一个实施例中,所述第二约束表示为公式(16):

[0032][0033]

其中,λ2表示第二约束,表示预设的互连线的最大长度。

[0034]

在本发明的一个实施例中,所述第三约束表示为公式(17):

[0035][0036]

其中,λ3表示第三约束;

[0037][0038][0039]

k表示相邻两个芯粒之间的最小距离约束,表示在横坐标轴方向上最小距离约束κ的惩罚,表示在纵坐标轴方向上最小距离约束κ的惩罚;

[0040]

若则χ1,χ2=0;

[0041]

若则χ1,χ2=0;

[0042]

若则χ1=1,χ2=0;

[0043]

若则χ1=0,χ2=1。

[0044]

在本发明的一个实施例中,所述混合目标函数表示为公式(20):

[0045][0046]

其中,λ表示惩罚函数,θ表示惩罚函数的权重;

[0047][0048]

分表示λ1,λ2,λ3的权重系数。

[0049]

在本发明的一个实施例中,所述根据所述混合目标函数和所述等效电路模型的pdn参数确定所述混合目标函数的最小值和对应的目标芯粒的位置、插入器中的目标电容

数量以及目标电容的位置,包括:

[0050]

根据所述混合目标函数和所述等效电路模型的pdn参数在pso算法中更新粒子的速度和位置;所述粒子包括芯粒的位置、插入器中的电容数量和电容的位置;

[0051]

通过metropolis准则更新边界外的粒子;

[0052]

在pso算法中更新粒子的最优位置和所述混合目标函数的最优值;

[0053]

在de算法中对染色体执行突变操作;

[0054]

在de算法中对染色体执行交叉操作;

[0055]

通过metropolis准则更新边界外的染色体;

[0056]

在pso算法中更新粒子的最优位置和所述混合目标函数的最优值,直至达到终止条件时,输出所述混合目标函数的目标函数值和对应的芯粒的目标位置、插入器中的目标电容数量以及目标电容的位置;其中,所述目标函数值为所述混合目标函数的最小值。

[0057]

本发明的有益效果:

[0058]

本发明通过阻抗目标函数、第一约束、第二约束和第三约束构建混合目标函数,阻抗目标函数是关于芯粒位置、电容器布局、实际阻抗以及目标阻抗的非线性函数,通过确定混合目标函数的最小值,能够得到对应的芯粒和电容的布局,从而得到2.5维集成电路的最佳布局,本发明的优化方法降低了系统阻抗,进一步减小了系统的同步开关噪声,提升了2.5维集成电路的性能。

[0059]

以下将结合附图及实施例对本发明做进一步详细说明。

附图说明

[0060]

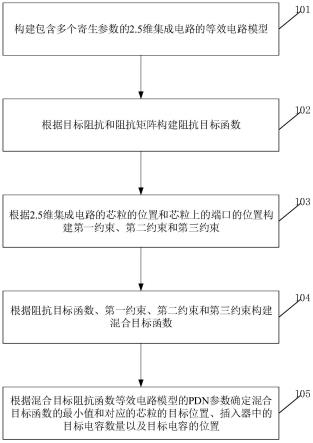

图1是本发明实施例提供的一种基于芯粒的2.5维集成电路的多约束阻抗优化方法的流程示意图;

[0061]

图2a是本发明实施例提供的芯粒所使用的pdn结构;

[0062]

图2b是本发明实施例提供的插入器所使用的pdn结构;

[0063]

图2c是本发明实施例提供的tsv阵列所使用的pdn结构;

[0064]

图2d是本发明实施例提供的等效电路模型;

[0065]

图3是本发明实施例提供的目标阻抗和工作频率的关系示意图;

[0066]

图4a是本发明实施例提供的第一约束的示意图;

[0067]

图4b是本发明实施例提供的第二约束的示意图;

[0068]

图4c是本发明实施例提供的第三约束的示意图;

[0069]

图5是本发明实施例提供的mdp算法的流程图;

[0070]

图6a是本发明实施例仿真实验的2.5维pdn的结构的剖面图;

[0071]

图6b是本发明实施例仿真实验的2.5维pdn的结构的俯视图;

[0072]

图7是使用具体实例对四种算法的迭代效率对比;

[0073]

图8是本发明实施例仿真实验的优化结果示意图。

具体实施方式

[0074]

下面结合具体实施例对本发明做进一步详细的描述,但本发明的实施方式不限于此。

[0075]

实施例一

[0076]

如图1所示,一种基于芯粒的2.5维集成电路的多约束阻抗优化方法,包括以下步骤:

[0077]

步骤101,构建包含多个寄生参数的2.5维集成电路的等效电路模型,获取等效电路模型的阻抗矩阵;阻抗矩阵为工作频率集合γ对应的实际阻抗zf的集合;

[0078]

步骤102,根据目标阻抗z

target,f

和阻抗矩阵构建阻抗目标函数;目标阻抗z

target,f

为工作频率对应的芯粒负载侧所允许的最大自阻抗;

[0079]

步骤103,根据2.5维集成电路的芯粒的位置和芯粒上的端口的位置构建第一约束、第二约束和第三约束;其中,第一约束指示基于芯粒之间的端口之间的多个互连线的长度之和的最小化约束的约束;第二约束指示基于预设的互连线的最大长度约束的长度约束;第三约束指示基于相邻两个芯粒之间的最小距离约束的距离约束;

[0080]

步骤104,根据阻抗目标函数、第一约束、第二约束和第三约束构建混合目标函数;

[0081]

步骤105,根据混合目标函数等效电路模型的pdn参数确定混合目标函数的最小值和对应的芯粒的目标位置、插入器中的目标电容数量以及目标电容的位置。

[0082]

本发明通过阻抗目标函数、第一约束、第二约束和第三约束构建混合目标函数,混合目标函数是关于芯粒位置、电容器布局、实际阻抗以及目标阻抗的非线性函数,通过确定对混合目标函数的最小值,得到对应的芯粒和电容的布局,从而得到2.5维集成电路的最佳布局,本发明的优化方法降低了系统阻抗,进一步减小了系统的同步开关噪声,提升了2.5维集成电路的性能。

[0083]

实施例二

[0084]

一种基于芯粒的2.5维集成电路的多约束阻抗优化方法,包括以下步骤:

[0085]

步骤201,构建包含多个寄生参数的2.5维集成电路的等效电路模型,获取等效电路模型的阻抗矩阵;阻抗矩阵为工作频率集合γ对应的实际阻抗zf的集合。

[0086]

2.5维集成电路的完整pdn由插入器(interposer)中的pdn(power distribution network,电源分布网络)、芯粒中的pdn、硅通孔(through silicon via,简称tsv)阵列、c4焊球阵列、微焊球阵列和去耦电容等,并对2.5维集成电路各部分进行建模,再通过一种分层次的级联方法,通过矩阵相乘操作,获取整个电路的z参数矩阵,如图2a、如图2b、如图2c和如图2d所示。具体建模过程参见现有技术:j.kim et al.,“chip-package hierarchical power distribution network modeling and analysis based on a segmentation method,”in ieee transactions on advanced packaging,vol.33,no.3,pp.647-659,aug.2010中的内容。z参数矩阵为等效电路模型的阻抗矩阵。其中,插入器也即是转接板。

[0087]

通过对2.5维集成电路进行约束分析构建混合目标函数,具体地,包括步骤202-步骤204:

[0088]

步骤202,根据目标阻抗z

target,f

和阻抗矩阵构建阻抗目标函数;目标阻抗z

target,f

为工作频率对应的芯粒的负载侧所允许的最大自阻抗。

[0089]

目标阻抗由两部分组成,如图3所示。平坦区域基于公式(1),在点f

knee

之后为斜坡区域,目标阻抗曲线以20db/dec的比率增加。

[0090]

[0091][0092]

其中,z

target

表示目标阻抗的平坦区域,v

ripple

表示芯粒上的负载的波纹电压,f

knee

表示拐点频率,i表示芯粒上的负载的工作电流,tr表示等效电路模型的噪声信号周期。

[0093]

在步骤201中,整个系统的阻抗采用了级联方法建模,阻抗目标函数ψ通过公式(3)表示:

[0094][0095]

其中,ψ1表示工作频率集合γ中对应的实际阻抗zf与目标阻抗z

target,f

之差的总和,当实际阻抗zf始终小于目标阻抗z

target,f

时,ψ1=0;ψ2表示插入器中放置的去耦电容的数量;ψ3是表示阻抗矩阵中所有实际阻抗zf的总和;

[0096]

分别表示ψ1,ψ2,ψ3的权重系数;

[0097][0098]

ψ2=ncꢀꢀꢀ

(5)

[0099][0100]

公式(7)-(13)是分析过程中的约束,以保持芯粒放置不超出插入器边界、防止芯粒放置重叠、确保坐标值为正值等。

[0101][0102][0103][0104][0105][0106]cunit

≥0

ꢀꢀꢀ

(12)

[0107]

nc∈n

+

ꢀꢀꢀ

(13)

[0108]

其中,xi,yi表示第i个芯粒的中点处的坐标,xj,yj表示第j个芯粒的中点处的坐标,αi,βi表示第i个芯粒在横坐标轴方向(x方向)和纵坐标轴方向(y方向)的长度,aj,βj表示第j个芯粒在横坐标轴方向和纵坐标轴方向的长度,芯粒在横坐标轴方向和纵坐标轴方向的长度也即是芯粒的长和宽,a,b表示插入器在横坐标轴方向和纵坐标轴方向的长度,也即是插入器的长和宽;c

unit

表示插入器中放置的去耦电容的电容值;n

+

表示正整数。坐标包括横坐标和纵坐标,坐标也即是位置。

[0109]

步骤203,根据2.5维集成电路的芯粒的位置和芯粒上的端口的位置构建第一约

束、第二约束和第三约束。

[0110]

首先,对于2.5维芯片系统,多个芯粒放置在插入器上,芯粒间通过由插入器中的重新分布层(rdl)进行通信。芯粒放置过程中的主要目标是最小化芯粒间的总线长,以降低制造成本,而芯粒的放置位置直接影响芯粒间布线的总线长。因此在阻抗优化过程中,导线总长度是一个非常必要的约束条件。

[0111]

硅插入器内的布线平面可以视为基于网格的矩形布线平面(设为曼哈顿布线法)。任意两个芯粒之间的线长以及布线总长度可以表示为(14)和(15)。任意两个芯粒之间的端口之间的布线为互连线,所有互连线的长度之和为布线总长度。λ1也可以理解为基于布线总长度最小化约束的惩罚。

[0112][0113]

其中,第一约束λ1表示基于布线总长度最小化约束的约束,λ1也即是布线总长度。表示第i个芯粒上的第p个端口和第j个芯粒上第q个端口之间的互连线的长度,该互连线的长度也即是曼哈顿布线距离,q表示2.5维集成电路所有芯粒上所有端口的集合;

[0114][0115]

x

i,p

,y

i,p

表示第i个芯粒上第p个端口的坐标,该芯粒通过rdl连接到另一个芯粒,x

j,q

,y

j,q

表示第j个芯粒上第q个端口的坐标。

[0116]

其次,除了上述所提的影响成本的布线总长度外,在2.5维集成电路系统中,单根导线的长度也会影响信号传输。单根导线不应太长,以满足传播时间约束和上升时间约束。因此,在对芯粒进行布局时,单根互连线的长度也是一个重要的限制。为预设的互连线的最大长度,该最大长度为单根互连线的长度,根据实际需要进行预先的设置即可。第二约束指示基于预设的互连线的最大长度约束的单根互连线长度约束,简称单线长度约束。λ2也可以理解为基于的单线长度惩罚。第二约束λ2表示为公式(16):

[0117][0118]

在2.5维电路系统中,随着越来越多的芯粒集成在单个插入器上,紧凑的多芯粒布局将导致散热问题。为了满足关键的热要求,相邻芯粒之间的最小距离设置为k。(17)、(18)、(19)表示由散热问题产生的距离约束方程。λ3表示基于相邻两个芯粒之间的最小距离约束的距离约束。λ3也可也理解为基于最小相邻距离约束的距离惩罚。

[0119]

第三约束λ3表示为公式(17):

[0120][0121]

其中,

[0122]

[0123][0124]

k表示相邻两个芯粒之间的最小距离约束,表示在横坐标轴方向上最小距离约束k的惩罚,表示在纵坐标轴方向上最小距离约束k的惩罚;同时:

[0125]

若则χ1,χ2=0;

[0126]

若则χ1,χ2=0;

[0127]

若则χ1=1,χ2=0;

[0128]

若则χ1=0,χ2=1。

[0129]

为了更好地理解,在图4a、图4b、图4c中示出了三种约束。图中的1、2、3表示不同的芯粒,芯粒之间通过互连线连接,虚线部分表示三种约束。

[0130]

步骤204,根据阻抗目标函数、第一约束、第二约束和第三约束构建混合目标函数;混合目标函数表示为公式(20):

[0131][0132]

其中,λ表示惩罚函数,θ表示惩罚函数的权重;

[0133][0134]

分表示λ1,λ2,λ3的权重系数。

[0135]

ψ是一个关于芯粒位置、电容器布局、实际阻抗以及目标阻抗的非线性函数。为了在阻抗优化过程中,约束布局过程对2.5维系统造成的其他负面影响,考虑了约束λ1,λ2,λ3,并在(21)中采用了惩罚函数λ,因此,结合ψ和λ,公式(20)中的表示一个新的混合目标函数,其中包含阻抗目标函数和惩罚函数。的优化过程对于找到2.5-d系统的最佳布局,同时在布局、实际阻抗、目标阻抗和约束之间进行权衡是有意义的。

[0136]

步骤205,根据混合目标函数等效电路模型的pdn参数确定混合目标函数的最小值和对应的芯粒的目标位置、插入器中的目标电容数量以及目标电容的位置。

[0137]

现有技术中,存在很多优秀的元启发式算法,而单一的元启发式算法各有其优缺点。在粒子群算法(particle swarm optimization,简称pso)中,每个粒子都在不断地搜索,并且受到其他粒子的影响。在迭代过程中,每个粒子通过两个极值进行更新,一个是粒子自身找到的最优解,称为局部极值,另一个是整个种群找到的最优解,称为全局极值。对于传统的pso算法,如果一些粒子过早陷入局部极值,整个粒子群将快速收敛,这种现象称为早熟现象。在差分进化(differential evolution,简称de)算法中,通过变异、交叉和选择操作,可以得到高度差异化的个体。差分进化粒子群优化算法(depso)将de算法和pso算法相结合得到的算法具有更加多样化的种群。请注意,无论是pso、de还是depso算法,在种群更新后,某些粒子可能超过边界条件。对于这些边界外粒子,通常的操作是随机重新更新它们,或直接为它们指定边界值,而这浪费了原有算法的更新机制。

[0138]

模拟退火(simulated annealing,简称sa)算法以一定的概率接受退化解,这提高

了得到全局最优解的可靠性。metropolis抽样准则是sa的核心,它以概率来接受新解,而不是遵循完全确定性的规则。因此,depso的基础上,利用metropolis方法处理边界外粒子,可以进一步优化算法。

[0139]

因此,可以通过结合pso、de与sa中的metropolis准则组成基于metropolis的差分粒子群优化算法(metropolis-based differential particle swarm optimization,简称mdp),通过mdp算法寻找混合目标函数的最小值,可以表示为表达式mdp算法输出该最小值对应的芯粒的目标位置、插入器中的目标电容数量以及目标电容的位置,以实现基于芯片的2.5维集成电路的阻抗优化。采用mdp方法迭代时,可以得到混合目标函数的多个值,的值越小越好。

[0140]

如图5所示,步骤205的具体步骤包括:

[0141]

步骤2051,输入混合目标函数和等效电路模型的pdn参数;

[0142]

步骤2052,初始化mdp;

[0143]

步骤2053,初始化种群和退火温度;

[0144]

步骤2054,根据混合目标函数和等效电路模型的pdn参数在pso算法中更新粒子的速度和位置;粒子包括芯粒的位置、插入器中的电容数量和电容的位置;等效电路模型的pdn参数包括芯粒pdn的线宽、间距、最小单元、个数,插入器上的pdn的线宽、间距、最小单元格的个数,tsv的直径、间距、高度、个数,焊球的直径、间距、高度、个数等参数。

[0145]

步骤2055,通过metropolis准则更新边界外的粒子;

[0146]

步骤2056,边界外的粒子更新之后,在pso算法中更新粒子的最优位置和混合目标函数的最优值;

[0147]

步骤2057,更新粒子最优位置和最优值之后,在de算法中对染色体执行突变操作;在de算法算法中染色体也即是pso算法中的粒子。

[0148]

步骤2058,突变操作之后在de算法中对染色体执行交叉操作;

[0149]

步骤2059,交叉操作之后通过metropolis准则更新边界外的染色体;

[0150]

步骤2060,边界外的染色体更新完成之后,在pso算法中更新粒子的最优位置和混合目标函数的最优值;

[0151]

步骤2061,判断是否满足终止条件;

[0152]

本步骤中,也即是判断是否达到最大迭代次数。

[0153]

步骤2062,若是,输出混合目标函数的目标函数值和对应的芯粒的目标位置、插入器中的目标电容数量以及目标电容的位置;

[0154]

若否,则返回步骤2054,继续执行步骤2054-步骤2060,直至满足终止条件。

[0155]

其中,目标函数值为混合目标函数的最小值。此时,输出的的目标函数值对应的芯粒的目标位置、插入器中的目标电容数量以及目标电容的位置也即是2.5维集成电路的最优布局方案。

[0156]

本发明中,采用了一个基于芯粒的2.5维集成电路实例对本发明实施例的优化方法进行测试,测试结构的参数如表格1,其结构图如图6a和图6b所示。

[0157]

首先我们先测试mdp算法与pso、de、depso算法的比较,将参数设置为θ=1.5,k=3μm,每个芯片之间

可以包括第一和第二特征直接接触,也可以包括第一和第二特征不是直接接触而是通过它们之间的另外的特征接触。而且,第一特征在第二特征“之上”、“上方”和“上面”包括第一特征在第二特征正上方和斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”包括第一特征在第二特征正下方和斜下方,或仅仅表示第一特征水平高度小于第二特征。

[0165]

在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不必须针对的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。此外,本领域的技术人员可以将本说明书中描述的不同实施例或示例进行接合和组合。

[0166]

以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1