一种PXIe总线系统定时模块设计的方法

一种pxie总线系统定时模块设计的方法

技术领域

1.本发明属于的同步触发技术领域;具体涉及一种pxie总线系统定时模块设计的方法。

背景技术:

2.在航空、航天和精密仪器测试等领域中,整体测试系统通常所需同时监控的i/o十分庞大,所需处理的测试数据也相当复杂,因此,单一模块仪器已不能满足复杂的数据采集和处理,多模块协调配合处理显得尤为重要,pxie总线技术中系统定时模块为多模块之间的协同合作提供了可能。在pxi系统中,机箱内部利用背板上路由的10mhz时钟和星型触发器提供的星型触发线可以实现机箱内部的同步触发,但是这具有一定的局限性,它的同步触发精度相较于pxie中定义的差分时钟和触发信号并不高,并且仅限于单个机箱内各个模块,不适用于多机箱同时工作的测试场景。随着技术的发展,pxi将pcie总线技术引入到pxi标准中,相应地制定了pxie(pci express extensions for instrumentation)总线规范,pxie硬件规范中新定义的系统定时模块很好地解决了pxie机箱中多模块实现高精度同步触发的问题,本方法基于pxie规范,设计一款符合pxie硬件规范的系统定时模块。本方法设计了4路pcie链路通过背板与系统控制器通信,设计的系统定时模块能提供高精度时钟和高精度的差分触发信号,能够实现pxie系统中各外设模块同步触发的功能,并且如果考虑二次开发,该方法还能实现多机箱同步触发功能。

3.该方法的特点主要有:

4.1)、采用高精度的晶振生成10mhz的板载时钟,该时钟一方面供给板载fpga使用,另一方面可以通过时钟输出电路输出,作为其他机箱的外部时钟输入,保证了时钟的同源,该方法也设计了相应的外部时钟输入电路以保证可以接收外部时钟;

5.2)、接收来自主控制器的触发命令,满足不同精度的触发方式,可利用pxi_trig、pxi_star和pxie_dstar三种触发线实现不同精度的触发,该触发也可以通过smb连接器提供给外部需要触发的机箱,保证触发的同源,该方法也设计了相应的外部触发输入电路以保证可以接受外部触发;

6.3)、利用verilog hdl对fpga进行编程可实现pxie系统中单机箱或多机箱内各个模块的同步触发。

技术实现要素:

7.本发明提供了一种pxie总线系统定时模块设计的方法,用以解决现有的pxie机箱高可靠性同步触发的问题。

8.本发明通过以下技术方案实现:

9.一种pxie总线系统定时模块设计的方法,所述定时模块包括电源模块、时钟模块和触发模块;

10.所述电源模块,将背板供给的电压12v转换为整个模块需要使用的电压;

11.所述时钟模块,作用是将外部时钟引入机箱实现同步功能;

12.所述触发模块,作用是提供符合pxie规范的触发信号实现触发功能。

13.一种pxie总线系统定时模块设计的方法,所述电源模块包括定时模块;所述定时模块包括fpga、控制器、xp4、xp3、tp1、tp2、电源模块、10mhz晶振、外部时钟输入、触发输入和触发输出;

14.所述fpga分别与控制器、电源模块、10mhz晶振、外部时钟输入、触发输入和触发输出相连接,所述fpga分别通过双向电压转换与xp4、xp3、tp1和tp2相连接;

15.所述fpga通过4路pcie链路接收到主控制器的命令后,根据命令将板载的10mhz时钟或外部给入的10mhz时钟通过pxi_clk10_in引脚给到背板。

16.一种pxie总线系统定时模块设计的方法,所述电源模块具体为,背板供电12v电压通过dc-dc降压芯片tps51397arjer降压得到1v电压vccint_1v0,并且该芯片转换成功后会给出一个pg_vccint信号表明电压已经成功转换,再将该标志信号作为芯片tps82130silt产生vcc_bram_1v0的使能信号,如此便实现了上电后先产生电压vccint,然后得到电压vcc_bram,其他信号以此类推,最后便实现了各信号上电的先后顺序。

17.一种pxie总线系统定时模块设计的方法,所述时钟模块包括板载时钟和外部时钟输入电路,所述板载时钟使用10mhz的温补晶振来生成,所述板载时钟包括温补晶振x1,所述温补晶振x1的1号端与电阻r36的一端相连接,所述温补晶振x1的4号端分别与电阻r36的另一端、电容c66的一端和电感l3的一端相连接,所述电感l3的另一端分别与电容c67的一端和工作电压vcc_3v3相连接,所述电容c67的另一端和电容c66的另一端相连接后接地;

18.所述温补晶振x1的3号端与电容c70的一端相连接,所述电容c70的另一端分别与电阻r37的一端和电阻r38的一端相连接,所述电阻r38的另一端接地,所述电阻r37的另一端分别与电阻r39的一端和fpga的bank 13上引脚10m_local相连接,所述电阻r39的另一端接地。

19.一种pxie总线系统定时模块设计的方法,所述外部时钟输入电路包括同轴连接器j1,所述同轴连接器j1的1号端与电容c71的一端相连接,所述电容c71的另一端分别与静电放电保护器d2的一端、串联2个静电放电保护器dn1、电阻r41的一端和电阻r41的一端相连接,静电放电保护器

20.所述电阻r41的另一端接地,所述电阻r40的另一端分别与电感l4的一端和电容c72的一端相连接,所述电感l4的另一端分别与电容c73的一端和fpga的bank 13上引脚10m_ext相连接,所述电容c73的另一端接地。

21.一种pxie总线系统定时模块设计的方法,所述触发模块包括触发输入电路和触发输出电路。

22.所述触发输入电路包括同轴连接器j8,所述同轴连接器j8的1号端与电阻r125的一端相连接,所述电阻r125的另一端分别与串联2个静电放电保护器dn3、二极管d6的正极、bav99wkjg的负极和芯片u17的1号端相连接,所述二极管d6的负极与工作电压vcc_3v3相连接,所述bav99wkjg的正极接地,

23.所述芯片u17的2号端与芯片u17的3号端相连接后接地,所述芯片u17的5号端与工作电压vcc_3v3相连接,所述芯片u17的6号端与fpga的bank 13上引脚sys_trig_in相连接;

24.所述触发输出电路包括同轴连接器j7,所述同轴连接器j7的1号端与电阻r124的

一端相连接,所述电阻r124的另一端分别与串联2个静电放电保护器dn2、二极管d4的正极、bav99wkjg的负极和芯片u16的6号端相连接,所述二极管d4的负极与工作电压vcc_3v3相连接,所述bav99wkjg的正极接地,

25.所述芯片u16的2号端与芯片u17的3号端相连接后接地,所述芯片u17的5号端与工作电压vcc_3v3相连接,所述芯片u17的1号端与fpga的bank 13上引脚sys_trig_out相连接。

26.一种pxie总线系统定时模块设计的方法,所述触发模块的触发线包括pxi_trig、pxi_star和pxie_dstar,pxi_trig,

27.pxi_trig信号电平转换电路包括芯片u11,所述芯片u11的1号端连接pxi_trig0_c,所述芯片u11的2号端分别连接电容c267和工作电压vcc_5v,所述芯片u11的3号端连接pxi_trig1_c,所述芯片u11的4号端连接pxi_trig2_c,所述芯片u11的5号端连接pxi_trig3_c,所述芯片u11的6号端连接pxi_trig4_c,所述芯片u11的7号端连接pxi_trig5_c,所述芯片u11的8号端连接pxi_trig6_c,所述芯片u11的9号端连接pxi_trig7_c,所述芯片u11的10号端连接电阻r114后再接工作电压vcc3v3_sys;

28.所述芯片u11的11号端接地,所述芯片u11的12号端连接pxi_trig7_f,所述芯片u11的13号端连接pxi_trig6_f,所述芯片u11的14号端连接pxi_trig5_f,所述芯片u11的15号端连接pxi_trig4_f,所述芯片u11的16号端连接pxi_trig3_f,所述芯片u11的17号端连接pxi_trig2_f,所述芯片u11的18号端连接pxi_trig1_f,所述芯片u11的19号端连接电容c266和工作电压vcc3v3_sys,所述芯片u11的20号端连接pxi_trig0_f;

29.所述pxi_star信号电平转换电路包括芯片u12,所述芯片u12的1号端连接pxie_star_0_j,所述芯片u12的2号端分别连接电容c264和工作电压vcc_5v,所述芯片u12的3号端连接pxie_star_1_j,所述芯片u12的4号端连接pxie_star_2_j,所述芯片u12的5号端连接pxie_star_3_j,所述芯片u12的6号端连接pxie_star_4_j,所述芯片u12的7号端连接pxie_star_5_j,所述芯片u12的10号端连接电阻r111后再接工作电压vcc3v3_sys;

30.所述芯片u12的11号端接地,所述芯片u12的14号端连接pxie_star_5,所述芯片u12的15号端连接pxie_star_4,所述芯片u12的16号端连接pxie_star_3,所述芯片u12的17号端连接pxie_star_2,所述芯片u12的18号端连接pxie_star_1,所述芯片u12的19号端连接电容c265和工作电压vcc3v3_sys,所述芯片u12的20号端连接pxie_star_0。

31.一种pxie总线系统定时模块设计的方法,所述主控制器通过pcie接口与集成了pcie的ip核xdma ip相连接,所述xdma ip分别与互联矩阵ip核axi interconnect ip和缓冲器utility buffer ip相连接,所述axi interconnect ip与系统定时模块相连接,所述utility buffer ip与参考时钟相连接。

32.所述系统定时模块包括寄存器1和寄存器2,所述寄存器1通过时钟逻辑模块进行时钟分发,所述寄存器2通过触发逻辑模块进行触发分配。

33.一种pxie总线系统定时模块设计的方法,所述系统定时模块具体为,主控制器给出一个8位的信号slot[7:0],寄存器1的低8位信号对应8位的slot表示需要同步的模块槽位;

[0034]

主控制器给出一个8位的信号trig_index[7:0],寄存器2的低8位信号对应8位的trig_index,表示使用的trig触发线号。

[0035]

时钟逻辑和触发逻辑完成后需要将该模块功能封装成具有axi接口的ip核以实现与xdma的连接,ip核封装完毕后设计pcie接口逻辑部分,该部分便是配置xdmaip核并将其与系统定时模块ip核相连实现控制器通过pcie链路对模块功能进行控制,这也是本方法功能实现的最后一步。

[0036]

一种pxie总线系统定时模块设计的方法,所述测量机箱同步触发装置包括主控器、xdma ip、系统定时模块ip核、axi interconnect ip、utility buffer ip和参考时钟,所述主控器通过pcie接口与xdma ip相连接,所述xdma ip与axi interconnect ip和utility buffer ip相连接,所述utility buffer ip与参考时钟相连接,所述axi interconnect ip与系统定时模块ip核相连接;

[0037]

所述系统定时模块ip核包括寄存器1和寄存器2,所述寄存器1通过时钟逻辑模块与时钟分发相连接,所述寄存器2通过触发逻辑模块与触发分配相连接。

[0038]

本发明的有益效果是:

[0039]

本发明采用高精度的晶振生成10mhz的板载时钟,该时钟一方面供给板载fpga使用,另一方面可以通过时钟输出电路输出,作为其他机箱的外部时钟输入,保证了时钟的同源,本发明具有相应的外部时钟输入电路以保证可以接收外部时钟。

[0040]

本发明接收来自主控制器的触发命令,满足不同精度的触发方式,可利用pxi_trig、pxi_star和pxie_dstar三种触发线实现不同精度的触发,该触发也可以通过smb连接器提供给外部需要触发的机箱,保证触发的同源,本发明具有相应的外部触发输入电路以保证可以接受外部触发。

[0041]

本发明利用verilog hdl对fpga进行编程可实现pxie系统中单机箱或多机箱内各个模块的同步触发。

附图说明

[0042]

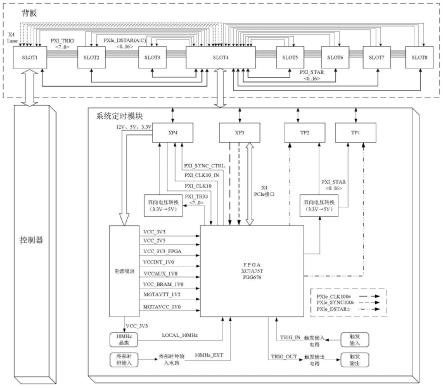

附图1是本发明的硬件实现框图。

[0043]

附图2是本发明上电顺序图。

[0044]

附图3是本发明12v电压转3.3v电压的电路图。

[0045]

附图4是本发明3.3v电压转1.8v电压的电路图。

[0046]

附图5是本发明时钟生成电路图。

[0047]

附图6是本发明外部时钟输入电路连接图。

[0048]

附图7是本发明pxi_trig信号电平转换电路图。

[0049]

附图8是本发明pxi_star信号电平转换电路图。

[0050]

附图9是本发明触发输入电路图。

[0051]

附图10是本发明触发输出电路图。

[0052]

附图11是本发明同步和触发方法固件实现框图。

[0053]

附图12是本发明时钟逻辑框图。

[0054]

附图13是本发明触发逻辑框图。

[0055]

附图14是本发明整体逻辑框图。

具体实施方式

[0056]

下面将结合本发明实施例中的附图对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0057]

一种pxie总线系统定时模块设计的方法,所述定时模块包括电源模块、时钟模块和触发模块;

[0058]

所述电源模块,将背板供给的电压12v转换为整个模块需要使用的电压;

[0059]

所述时钟模块,作用是作用是将外部时钟引入机箱实现同步功能;

[0060]

所述触发模块,作用是提供符合pxie规范的触发信号实现触发功能。

[0061]

一种pxie总线系统定时模块设计的方法,所述电源模块包括定时模块;所述定时模块包括fpga、控制器、xp4、xp3、tp1、tp2、电源模块、10mhz晶振、外部时钟输入、触发输入和触发输出;

[0062]

所述fpga分别与控制器、电源模块、10mhz晶振、外部时钟输入、触发输入和触发输出相连接,所述fpga分别通过双向电压转换与xp4、xp3、tp1和tp2相连接;

[0063]

所述fpga通过4路pcie链路接收到主控制器的命令后,根据命令将板载的10mhz时钟或外部给入的10mhz时钟通过pxi_clk10_in引脚给到背板。

[0064]

背板将该时钟作为pxi_clk10路由至需要同步的槽位,与此同时如果需要多机箱同步,该10mhz还可通过10m_out输出给参与同步的机箱以保证时钟的同源;时钟分发完毕后,该发明再将触发信号通过pxi_trig、pxi_star和pxie_dstar这三种不同精度的触发线路由至需要触发的槽位,可根据实际需要具体选择,该触发信号可来自机箱内部,也可来自机箱外部,同时也可将该触发信号通过触发输出电路输出至需要触发的机箱以保证触发的同源;这样便实现了多机箱的同步和触发。该方法的供电部分有上电顺序要求,其中fpga内核推荐的上电顺序为vccint

‑‑

》vccbram

‑‑

》vccaux

‑‑

》vcco,gtp推荐的上电顺序为vccint

‑‑

》vmgtavcc

‑‑

》vmgtavtt。

[0065]

一种pxie总线系统定时模块设计的方法,(图2)所述电源模块具体为,背板供电12v电压通过dc-dc降压芯片tps51397arjer降压得到1v电压vccint_1v0,并且该芯片转换成功后会给出一个pg_vccint信号表明电压已经成功转换,再将该标志信号作为芯片tps82130silt产生vcc_bram_1v0的使能信号,如此便实现了上电后先产生电压vccint,然后得到电压vcc_bram,其他信号以此类推,最后便实现了各信号上电的先后顺序;

[0066]

其中fpga内核推荐的上电顺序为vccint

‑‑

》vccbram

‑‑

》vccaux

‑‑

》vcco,高速接口gtp推荐的上电顺序为vccint

‑‑

》vmgtavcc

‑‑

》vmgtavtt。

[0067]

所述电源模块还包括3.3v电压电路和1.8v电压电路

[0068]

设计采用了两种方式得到3.3v电压,一种是通过xp4连接器直接从背板接入3.3v供电,另外一种是通过xp4连接器从背板接入12v电压,然后通过电压转换芯片转换得到3.3v电压,这两种方法都需要使用,第一种得到的3.3v直接供给触发线的双向电平转换器使用,第二种得到的3.3v一部分给fpga使用,一部分给时钟和触发电路使用。

[0069]

设计中使用型号为tps54531ddar的dc/dc转换器实现12v电压转3.3v电压,其电路连接方式见图3。tps54531ddar的输出电压为3.3v,具有过压瞬态保护电路可限制启动和瞬

变期间的电压过冲,这样保证了整个设计工作电压的稳定。

[0070]

如图3所示,芯片u2的1号端与电容c1的一端相连接,所述芯片u2的2号端分别与电阻r3的一端、电容c16的一端、电容c15的一端、电容c14的一端和工作电压vcc12v_sys相连接,所述电容c16的另一端分别与电容c15的另一端、电容c14的另一端和接地端相连接,所述芯片u2的2号端分别与电阻r3的另一端和电阻r10的一端相连接,所述电阻r10的另一端接地,所述芯片u2的4号端与电容c20相连接后接地,所述芯片u2的8号端分别与电容c1的另一端、稳压二极管d1的负极和电感l1的一端,所述芯片u2的7号端分别与稳压二极管d1的正极、电容c2的一端、电容c3的一端、电容c4的一端和接地端相连接,所述电感l1的另一端分别与电容c2的另一端、电容c3的另一端、电容c4的另一端、电阻r1的一端、电容c5的一端和工作电压vcc_3v3,所述电阻r1的另一端与电阻r4的一端相连接,所述电阻r4的另一端分别与芯片u2的5号端和电阻r11的一端相连接,所述电阻r11的另一端接地;

[0071]

所述芯片u2的6号端分别与电容c18的一端和电容c21的一端相连接,所述电容c18的另一端与电阻r9的一端相连接,所述电阻r9的另一端与电容c21的另一端相连接后接地;

[0072]

所述芯片u2的9号端接地。

[0073]

1.8v电压电路

[0074]

tps82130silt是一款17v输入3a的降压转换器,可实现轻负载效率的省电模式,可实现最低压降的100%占空比,具体使用如图4所示。其中fb引脚为反馈基准引脚,连接到该引脚的外部电阻对输出电压进行编程,计算公式满足如下公式:

[0075][0076]

电路中电阻对应关系为:r

17

对应公式中的r1,r

19

对应公式中的r2,为了得到1.8v的电压,需要选用电阻阻值r

17

=124kω,r

19

=100kω,则输出电压按照公式(1)计算得1.792v,近似于1.8v。

[0077]

如图4所示,芯片u7的1号端连接pg_vccint,所述芯片u7的1号端与电容c25的一端、电容c26的一端和工作电压vcc12v_sys相连接,所述电容c25的另一端与电容c26的另一端相连接后接地,所述芯片u7的8号端与电容c21相连接后接地,所述芯片u7的3号端与芯片u7的9号端相连接后接地;

[0078]

所述芯片u7的4号端分别与芯片u7的5号端、电阻r30的一端、电容c57的一端、电容c34的一端和工作电压vccbram_1v0相连接;所述电容c57的另一端、电容c34的另一端相连接后接地,所述芯片u7的6号端分别与电阻r30的另一端和电阻r32的一端相连接,所述电阻r32的另一端接地,所述芯片u7的7号端与敌人在r32相连接后再接工作电压vcc_3v3。

[0079]

一种pxie总线系统定时模块设计的方法,所述时钟模块包括板载时钟和外部时钟输入电路,所述板载时钟使用10mhz的温补晶振来生成,所述板载时钟包括温补晶振x1,所述温补晶振x1的1号端与电阻r36的一端相连接,所述温补晶振x1的4号端分别与电阻r36的另一端、电容c66的一端和电感l3的一端相连接,所述电感l3的另一端分别与电容c67的一端和工作电压vcc_3v3相连接,所述电容c67的另一端和电容c66的另一端相连接后接地;

[0080]

所述温补晶振x1的3号端与电容c70的一端相连接,所述电容c70的另一端分别与电阻r37的一端和电阻r38的一端相连接,所述电阻r38的另一端接地,所述电阻r37的另一端分别与电阻r39的一端和fpga的bank 13上引脚10m_local相连接(如图5所示),所述电阻

r39的另一端接地。

[0081]

一种pxie总线系统定时模块设计的方法,如图6所示,所述外部时钟输入电路包括同轴连接器j1,所述同轴连接器j1的1号端与电容c71的一端相连接,所述电容c71的另一端分别与静电放电保护器d2的一端、串联2个静电放电保护器dn1、电阻r41的一端和电阻r41的一端相连接,静电放电保护器

[0082]

所述电阻r41的另一端接地,所述电阻r40的另一端分别与电感l4的一端和电容c72的一端相连接,所述电感l4的另一端分别与电容c73的一端和fpga的bank 13上引脚10m_ext相连接,所述电容c73的另一端接地。

[0083]

温补晶振搭建的电路在温度变化时,振荡回路中的负载电容会随温度变化而变化,来补偿石英晶体振荡器由于环境温度变化所产生的频率偏移,从而使得产生的时钟精度提高。

[0084]

一种pxie总线系统定时模块设计的方法,(图9、10)所述触发模块包括触发输入电路和触发输出电路,

[0085]

所述触发输入电路包括同轴连接器j8,所述同轴连接器j8的1号端与电阻r125的一端相连接,所述电阻r125的另一端分别与串联2个静电放电保护器dn3、二极管d6的正极、bav99wkjg的负极和芯片u17的1号端相连接,所述二极管d6的负极与工作电压vcc_3v3相连接,所述bav99wkjg的正极接地,

[0086]

所述芯片u17的2号端与芯片u17的3号端相连接后接地,所述芯片u17的5号端与工作电压vcc_3v3相连接,所述芯片u17的6号端与fpga的bank 13上引脚sys_trig_in相连接;

[0087]

所述触发输出电路包括同轴连接器j7,所述同轴连接器j7的1号端与电阻r124的一端相连接,所述电阻r124的另一端分别与串联2个静电放电保护器dn2、二极管d4的正极、bav99wkjg的负极和芯片u16的6号端相连接,所述二极管d4的负极与工作电压vcc_3v3相连接,所述bav99wkjg的正极接地,

[0088]

所述芯片u16的2号端与芯片u17的3号端相连接后接地,所述芯片u17的5号端与工作电压vcc_3v3相连接,所述芯片u17的1号端与fpga的bank 13上引脚sys_trig_out相连接。

[0089]

一种pxie总线系统定时模块设计的方法,所述触发模块的触发线包括pxi_trig、pxi_star和pxie_dstar,pxi_trig,所述pxi_trig信号是由pfga的bank13产生,电压为3.3v,故需要一个双向电平转换器来实现与背板电压之间的转换,转换电路如图7所示:

[0090]

pxi_trig信号电平转换电路包括芯片u11,所述芯片u11的1号端连接pxi_trig0_c,所述芯片u11的2号端分别连接电容c267和工作电压vcc_5v,所述芯片u11的3号端连接pxi_trig1_c,所述芯片u11的4号端连接pxi_trig2_c,所述芯片u11的5号端连接pxi_trig3_c,所述芯片u11的6号端连接pxi_trig4_c,所述芯片u11的7号端连接pxi_trig5_c,所述芯片u11的8号端连接pxi_trig6_c,所述芯片u11的9号端连接pxi_trig7_c,所述芯片u11的10号端连接电阻r114后再接工作电压vcc3v3_sys;

[0091]

所述芯片u11的11号端接地,所述芯片u11的12号端连接pxi_trig7_f,所述芯片u11的13号端连接pxi_trig6_f,所述芯片u11的14号端连接pxi_trig5_f,所述芯片u11的15号端连接pxi_trig4_f,所述芯片u11的16号端连接pxi_trig3_f,所述芯片u11的17号端连接pxi_trig2_f,所述芯片u11的18号端连接pxi_trig1_f,所述芯片u11的19号端连接电容

c266和工作电压vcc3v3_sys,所述芯片u11的20号端连接pxi_trig0_f;

[0092]

所述pxi_star信号是由pfga的bank16产生,电压为2.5v,也需要一个双向电平转换器来实现与背板电压之间的转换,转换电路如图8所示:

[0093]

所述pxi_star信号电平转换电路包括芯片u12,所述芯片u12的1号端连接pxie_star_0_j,所述芯片u12的2号端分别连接电容c264和工作电压vcc_5v,所述芯片u12的3号端连接pxie_star_1_j,所述芯片u12的4号端连接pxie_star_2_j,所述芯片u12的5号端连接pxie_star_3_j,所述芯片u12的6号端连接pxie_star_4_j,所述芯片u12的7号端连接pxie_star_5_j,所述芯片u12的10号端连接电阻r111后再接工作电压vcc3v3_sys;

[0094]

所述芯片u12的11号端接地,所述芯片u12的14号端连接pxie_star_5,所述芯片u12的15号端连接pxie_star_4,所述芯片u12的16号端连接pxie_star_3,所述芯片u12的17号端连接pxie_star_2,所述芯片u12的18号端连接pxie_star_1,所述芯片u12的19号端连接电容c265和工作电压vcc3v3_sys,所述芯片u12的20号端连接pxie_star_0。

[0095]

一种pxie总线系统定时模块设计的方法,主控制器通过m_axi_lite接口访问系统定时模块ip核内部的状态寄存器,并根据分配的地址以及偏移来修改寄存器的值,时钟模块逻辑和触发模块逻辑会根据该寄存器的值输出时钟和触发信号,从而实现整个系统定时模块的功能,本发明便是用axi4-lite接口实现对状态寄存器的配置来实现系统定时模块的功能。本发明使用两个32位的状态寄存器来接收主控制器的信号,寄存器1的值用来控制系统定时模块输出时钟信号,寄存器2的值用来控制系统定时模块输出触发信号。

[0096]

所述主控制器通过pcie接口与fpga的集成了pcie的ip核xdmaip相连接,所述xdmaip分别与互联矩阵ip核axiinterconnectip和缓冲器utilitybufferip相连接,所述axi interconnectip与系统定时模块相连接,所述utilitybufferip与参考时钟相连接。

[0097]

所述系统定时模块包括寄存器1和寄存器2,所述寄存器1通过时钟逻辑模块进行时钟分发,所述寄存器2通过触发逻辑模块进行触发分配。

[0098]

一种pxie总线系统定时模块设计的方法,以同步8个模块为例设计的时钟逻辑框图如图12所示:所述系统定时模块具体为,主控制器给出一个8位的信号slot[7:0],寄存器1的低8位信号对应8位的slot表示需要同步的模块槽位;例如slot=1001_0010表示系统定时模块需要向槽位8、5和槽位2发送10mhz的同步时钟,系统定时模块给出时钟后的同时给出一个flag标志信号表示时钟已经分发完毕;

[0099]

各外设模块收到系统定时模块分发的10mhz时钟后便实现了同步,此时还需要主控制器控制系统定时模块给出触发信号;

[0100]

设计的触发逻辑框图如图13所示:主控制器给出一个8位的信号trig_index[7:0],寄存器2的低8位信号对应8位的trig_index,表示使用的trig触发线号。例如trig_index=0001_0000表明整个系统使用第五根trig触发线传输触发信号,规范里规定pxi_trig触发线是通过上拉电阻与电源相接的,因此可设计当主控制器给出触发命令后,系统定时模块根据所要使用的触发线号将对应的触发线电平拉低,外设模块检测到该低电平后便可开始工作。

[0101]

时钟逻辑和触发逻辑完成后需要将该模块功能封装成具有axi接口的ip核以实现与xdma的连接,ip核封装完毕后设计pcie接口逻辑部分,该部分便是配置xdmaip核并将其与系统定时模块ip核相连实现控制器通过pcie链路对模块功能进行控制,这也是本方法功

能实现的最后一步。

[0102]

一种pxie总线系统定时模块设计的方法,所述测量机箱同步触发装置包括主控器、xdma ip、系统定时模块ip核、axi interconnect ip、utility buffer ip和参考时钟,所述主控器通过pcie接口与xdma ip相连接,所述xdma ip与axi interconnect ip和utility buffer ip相连接,所述utility buffer ip与参考时钟相连接,所述axi interconnect ip与系统定时模块ip核相连接;

[0103]

所述系统定时模块ip核包括寄存器1和寄存器2,所述寄存器1通过时钟逻辑模块与时钟分发相连接,所述寄存器2通过触发逻辑模块与触发分配相连接。

[0104]

利用系统定时模块ip核与xdma搭建功能测试bd图的示意图如图14所示,utility buffer为参考时钟缓冲ip核,因为是通过pcie链路来与主机进行通信,因此需要将其配置为收发器差分时钟缓冲,xdma需要将其pcie通道数配置为x4即4个lane,axi的时钟频率为250mhz,并且将其配置为带有axi_lite接口的xdma用来实现后续对寄存器的读写,自动连线后生成了一个axi interconnect模块,这个模块是用来连接axi内存映射的主设备和从设备,也就是通过这个模块,xdma的m_axi_lite接口与系统定时模块ip核的s00_axi连接在一起。主机的pcie接口提供的参考时钟pcie_ref经过差分缓冲器给到xdma,xdma再给出时钟给后续模块,复位信号也是如此,都是由主机提供。系统定时模块ip核的输出一方面通过ila来进行观察,另一方面通过引脚分配将时钟信号和触发信号给到板卡的对应引脚输出。

[0105]

本方法在pxie机箱中应用的具体实施方法如下:

[0106]

1)、板卡上电,进行硬件初始化;

[0107]

2)、加载pcie接口驱动,通过驱动程序设置本方法的控制逻辑提供的配置寄存器。也可通过fpga内其他逻辑配置该寄存器,寄存器主要提供同步模块数量和具体槽位的信息;

[0108]

3)数据解析:接收到控制器给的命令后对本方法控制逻辑的配置寄存器值进行解析,得到需要同步的模块的相关信息。

[0109]

4)时钟分发:得到需要同步的模块信息后将板载时钟一方面通过pxi_clk10_in引脚输出至背板,背板上的多路选择器选择该时钟作为同步时钟pxi_clk10,该时钟再通过背板上的扇出芯片扇出至各个槽位;另一方面板载时钟通过10m_out这个引脚输出至外部机箱使用,外部机箱的配置与单个机箱类似,时钟同源保证了各模块的同步。

[0110]

5)、触发分发:触发的分发是在时钟分发完毕后进行的,本方法接收到主控制器给的触发命令后一方面将该触发信号放在对应的触发线上,通过背板路由至各个需要触发的槽位;另一方面将该触发信号通过smb连接器输出至外部机箱使用,这样保证了触发的同源,配合同步的时钟实现多个模块的同步触发。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1