电路版图的拆分验证方法、双重图形光刻方法、存储介质与流程

1.本发明涉及集成电路的物理设计规则验证(drc)的技术领域,尤其涉及一种电路版图进行双重版图的拆分及验证。

背景技术:

2.集成电路(integrated circuits,ic),自1958年美国德克萨斯仪器公司(ti)的jack kilby和仙童公司的robert noyce发明出来至今,每个芯片上可容纳的晶体管数目,一直都在以摩尔定律(moore’s law)的速度快速地增长,从最初的几个晶体管已经迅速增长到了如今的570多亿个晶体管,同时,每片ic中标准单元的特征尺寸也在不断的减小,当今最先进的技术节点,已经达到了5nm以下。但问题也随之而来。由于新的制造工艺越来越逼近物理极限,即使有新工艺和新材料的加持,先进特征尺寸器件的制造也面临越来越严峻的困难与挑战。

3.为满足芯片更小特征尺寸和不断提升的性能等要求,引入了多重图形光刻(multiple patterning lithography)工艺,并且多重图形光刻被视为在当前制造工艺水平下,在技术上切实可行的先进工艺节点制造手段。这种工艺是将原来在同一版图上的版图图形分成多组多次进行曝光,使得原本相距较近的版图图形分到不同的掩膜版上,而同一掩膜板中版图图形之间间距变大,减小了掩膜板相邻图形之间的光刻干涉效应,进而提高版图图形密度。其中双重曝光图形技术(double patterning technology,以下简称dpt)作为多重图形光刻中最常用的光刻工艺,其是将版图图形分为两组,用两张掩膜板来承载两组版图图形,并分两次曝光来提高光刻后的解析度。双重图形光刻相较传统的曝光工艺,其图形密度能够提升约一倍。

4.双重图形光刻工艺其最大的挑战在于如何划分版图图形,使得版图图形能够以最小的光刻干涉,分配在两张掩膜板上。在版图分解的过程中,也会存在无法分解的图形组合,即不论这些图形如何进行配色,都无法实现所有相邻图形的颜色不相同,这样的图形组合被称作无解冲突。

5.因此,如何提供一种能够找到电路版图中的所有无解冲突的方案,使得电路版图可以进行改进、避免无解冲突的方法是业界亟待解决的技术问题。

技术实现要素:

6.为了解决现有技术中电路版图的设计问题不能有效被发现的技术问题,本发明提出了电路版图的拆分验证方法、双重图形光刻方法、存储介质。

7.本发明提出的电路版图的拆分验证方法,包括:

8.步骤1,扫描解析电路版图得到电路版图中的所有图形并进行预处理;

9.步骤2,将预处理后的所有图形插入到网格中,得到包含所有图形的图形列表,以及存储网格地址以及网格内的图形的网格索引;

10.步骤3,采用深度优先遍历算法对图形列表进行遍历,在遍历的过程中根据掩膜分

配规则将未分配掩膜的图形分配至双层掩膜当中的对应的掩膜上,同时根据间距规则查找已分配掩膜的图形之间是否存在相同掩模间距违规的情况,若存在,则将间距违规的两个图形记录为一对冲突节点;

11.步骤4,查找每一对冲突节点的冲突环,并报告所有冲突环。

12.进一步,所述步骤2具体包括:

13.步骤2.1,找到当前处理的图形的最小覆盖矩形,记录最小覆盖矩形所涉及的网格地址;

14.步骤2.2,遍历每一个网格地址涉及的网格矩形是否与当前处理的图形发生了碰撞,若发生了碰撞,则将当前处理的图形与对应的网格地址进行关联。

15.进一步,所述步骤3具体包括:

16.步骤3.1,对图形列表进行遍历,若遍历到的当前图形未被分配掩膜,则将当前图形分配到双层掩膜当中的一层掩膜中;

17.步骤3.2,根据间距规则搜寻与当前图形的间距违规的所有对比图形,若能够得到当前图形的所有对比图形列表,判断对比图形列表中是否有已经分配掩膜的对比图形,且与当前图形位于同一掩膜,则将当前图形与该对比图形作为一对冲突节点记录到冲突列表中,并执行下一步骤;若当前图形不存在对比图形列表,返回当前图形的上一级图形,重复步骤3.2直至上一级图形的对比图形列表中的图形被遍历完毕,或者返回步骤3.1直至图形列表中的所有图形均被分配掩膜后,再执行步骤4;

18.步骤3.3,对对比图形列表进行遍历,将遍历到的当前对比图形分配到双重掩膜当中的另一层掩膜中,使当前图形与对比图形位于不同的掩膜,将当前对比图形作为当前图形返回步骤3.2。

19.进一步,所述步骤4包括:

20.根据间距规则找到每一对冲突节点中每个图形对应的间距违例列表;

21.采用深度优先遍历方法对一对冲突节点中的两个图形的间距违例列表中的间距违例图形进行同步遍历,并添加到该对冲突节点的冲突环列表中;

22.判断当前遍历的间距违例图形是否也存在于一对冲突节点中另一个图形的间距违例列表中,若存在,则将该间距违例图形加入到该对冲突节点的冲突环列表中,形成闭环。

23.进一步,所述步骤4中多对冲突节点的冲突环的查找通过多个线程并行执行。

24.进一步,所述预处理为消除图形与图形之间的重叠情况,将相互重叠的图形合并为一个图形。

25.进一步,根据间距规则搜寻与当前图形的间距违规的所有对比图形具体为基于边放大查找与当前图形的间距违规的所有对比图形。

26.本发明提出的双重图形光刻方法,在对电路版图进行光刻之前,采用上述技术方案所述的电路版图的拆分验证方法查找所有冲突环,并对电路版图的设计进行改进,直至所述电路版图不存在冲突环,再对电路板进行光刻。

27.本发明提出的计算机可读存储介质,用于存储计算机程序,所述计算机程序运行时执行上述技术方案所述的电路版图的拆分验证方法。

28.本发明通过网格索引来存储图形,图形之间的间距违例关系,只有处理到对应图

形才会查询与此图形存在间距违例的所有图形,用完这些图形的信息即释放内存空间,不会一直存储着,所以与传统算法相比,节省了很多内存空间。本发明在分配掩膜的流程上也进行了优化,搜寻图形的同时就在分配掩模,加快了求解时间;而且采用深度优先的方式进行分配掩膜,相比传统以广度优先的方式进行分配掩膜,最终能够获得更少的冲突对数量,从而减小后续搜寻冲突环的求解时间。本发明基于网格索引,在找到版图中所有分配掩膜产生冲突的图形对后,对于这些冲突对图形,通过多线程来寻找冲突环。尽管重新查询每个图形间距违例图形的信息,需要再次进行查询,但不构建冲突图,也就不需要大量的内存空间来存储图形的间距违例关系,可以通过多线程并行加速求解,大大加快求解时间。

附图说明

29.下面结合实施例和附图对本发明进行详细说明,其中:

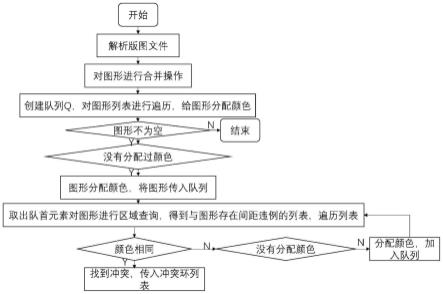

30.图1是本发明的一实施例的流程图。

31.图2是本发明的一实施例查找冲突环的流程图。

32.图3是本发明进行预处理后的电路版图模型。

33.图4是边放大和顶点放大的区别对比图。

34.图5是本发明一实施例的多边形放大的处理流程示意图。

35.图6是本发明一实施例的网格插入的示意图。

36.图7是本发明一实施例找到冲突对的示意图。

37.图8是图7的节点示意图。

38.图9是本发明搜寻冲突环的情况之一示意图。

39.图10是本发明搜寻冲突环的情况之二示意图。

40.图11是本发明搜寻冲突环的情况之三示意图。

41.图12是本发明一实施例的报告所有违例的示意图。

具体实施方式

42.为了使本发明所要解决的技术问题、技术方案及有益效果更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

43.由此,本说明书中所指出的一个特征将用于说明本发明的一个实施方式的其中一个特征,而不是暗示本发明的每个实施方式必须具有所说明的特征。此外,应当注意的是本说明书描述了许多特征。尽管某些特征可以组合在一起以示出可能的系统设计,但是这些特征也可用于其他的未明确说明的组合。由此,除非另有说明,所说明的组合并非旨在限制。

44.光刻技术作为集成电路制造中最复杂、最关键的工艺,大规模集成电路往往要经过十几次光刻才能完成各层图形的全部传递;而光刻所需要的掩模版离不开版图分解,快速且高质量的版图分解,成为影响集成电路性能、成品率及可靠性的关键因素。因此版图分解具有重要的意义和应用价值,将会为集成电路可制造性设计方面带来极大的增益。它的有效性以及速度会为集成电路的规模性生产提高制造芯片的可靠性,使芯片的良品率得到提高,促进企业的经济效益以及社会资源的节约,研究更加高效的算法成为必然。本发明的

终极目标在于通过算法实现快速双重图形划分的同时尽量减少无解冲突的产生。通过本发明的电路版图的拆分验证方法可以对电路版图进行快速双重图形划分,同时找到所有的无解冲突,然后根据本发明找到的无解冲突,可以对电路版图的设计进行改进,从而之后可以实现快速双重图形划分同时减少无解冲突的产生。

45.如图1所示,本发明的电路版图的拆分验证方法,在本方法中,基于自行研究的网格索引结构与图形分配掩膜算法,通过将原始版图所有图形传入网格中,基于网格索引对图形分配掩膜,寻找冲突,然后根据冲突报告出所有违例。

46.其中dpt要求将原始版图中间距小于最小工艺尺寸的图形拆分在两层不同掩膜版上完成光刻。在此过程中,不考虑图形自身与自身之间的违例。本发明以图论中的所研究的简单图表示版图相关情况,简单图是指“四色猜想”定理中所研究的简单图,即图中即不存在环也不存在重边的图,其中环指的是构成一个环的节点图形中其中起始节点图形和末端节点图形为同一节点的边,环等价于图形自身与自身间距小于x

min

,x

min

为最小工艺尺寸,而重边是指相同两节点图形之间存在的边不唯一,即图形与图形之间存在多处位置间距小于x

min

。在简单图中,完全可以用一个节点代表版图中对应的图形,节点之间的边表示版图中对应两个图形之间间距小于x

min

。

47.本发明的电路版图的拆分验证方法先扫描解析电路版图得到电路版图中的所有图形,例如,扫描解析图3左侧所示的位于一个掩膜上的电路版图,可以得到8个不同的矩形图形。

48.扫描得到电路版图中的所有图形之后,需要对图形进行预处理。图形的预处理主要是消除图形与图形之间的重叠情况。例如,图3中最上方的三个矩形之间存在重叠的现象,因而需要把这三个图形合并为一个图形,图3中右下角的三个矩形也存在相互重叠的情况,需要把这三个图形也合并为一个矩形。

49.预处理后,由原来的8个图形就变成了5个图形,如图3所示。

50.在有些电路版图中,如图3中右侧所示的位于另一个掩模(也称之为掩模版)上的电路版图,图形与图形之间可能不存在重叠的情况,那么预处理时就不需要进行消重处理。

51.在一个具体实施例中,根据间距规则搜寻与当前图形的间距违规的所有对比图形具体为基于边放大查找与当前图形的间距违规的所有对比图形。图4示出了点放大和边放大的区别。将多边形图形,放到一个矩形区域中,对图形进行水平或者垂直分解,分解图形至梯形或矩形,然后将分解后的所有图形进行放大,然后将放大后存在重叠的图形进行一个合并,如图5所示。

52.将预处理后的所有图形插入到网格中,得到包含所有图形的图形列表,以及存储网格地址以及网格内的图形的网格索引,此时图形与图形之间不存在重叠现象。

53.本发明提出的算法的关键是所构建的网格索引结构,每个网格索引是基于一个很长的一维数组来存储信息,这是由于计算机在读取数据上会更大概率读取靠近存储位置的数据,采用一维数组,在读取数据上有着更快的速度。假设网格的横坐标最大为x,纵坐标最大为y,则一维数组的大小为x*y,一维数组的成员类型为图形链表,在一个实施例中,图形链表具体为链式的图形节点,若是对应的网格中不存在图形,则图形链表中的对象为空,若是对应的网格中存在一个或多个图形,那么每一个图形就是一个图形节点(也称之为节点),图形链表即将这些节点通过线条进行链接,将一维数组进行分块,对一维数组的每一

数据块的开始位置都存储着这一数据块结束的地址,经过这样处理,将一维转化为了二维,可以快速到达数组的指定索引位置,也就是到指定的网格位置。具体实施时,申请x大小,成员类型为指针的数组b,b[i]的指针为a[i*y]的地址,以此构造出二维数组b,从而将一维数组a转化为了二维数组b。通过横纵坐标,b[i][j]就可以直接绑定并快速定位到a[i*y+j]位置的网格单元。另外,每个网格都有个单向链表存储在此网格位置的图形信息,一个网格中可能有多个图形的部分或全部,但只要碰到网格就会存储进该网格。如图6,网格b[1][1]存储着图形链表{a,b,c},其中a,b,c即为图形的唯一标识,即图形对象。另外,每个网格都有个单向链表存储在此网格位置的图形信息,例如,一个网格中可能有多个图形的部分或全部,那么该网格的单向链表中存储这些图形信息,图形信息具体为图形的唯一标识。

[0054]

将图形插入到网格中构建网格索引具体为找到当前处理的图形的最小覆盖矩形,记录最小覆盖矩形所涉及的网格地址,如图6所示,梯形b所示涉及到的网格地址范围为(x(1-5),y(1-3)),也称之为格点坐标范围。对于每个网格需要根据格点坐标和网格的长宽,得到网格矩形区域。遍历每一个网格地址涉及的网格矩形是否与当前处理的图形发生了碰撞,若发生了碰撞,则将当前处理的图形与对应的网格地址进行关联,例如网格地址(2,1)的网格矩形与图像b发生了碰撞,则网格地址(2,1)对应的网格链表就需要存储图像b的图像信息,例如网格地址(5,3)的网格矩形没有与图像b发生碰撞,虽然图像b的最小覆盖矩形中最开始也把网格地址(5,3)收录了进来,通过这个步骤发现其实网格(5,3)并没有与图像b发生碰撞,因而网格(5,3)的网格链表中并不需要存储图像b的图像信息。

[0055]

采用深度优先遍历算法对图形列表进行遍历,在遍历的过程中根据掩膜分配规则将未分配掩膜的图形分配至双层掩膜当中的对应的掩膜上,同时根据间距规则查找已分配掩膜的图形之间是否存在相同掩模间距违规的情况,若存在,则将间距违规的两个图形记录为一对冲突节点,最后再查找每一对冲突节点的冲突环,并报告所有冲突环。所有图形经过处理以及插入网格之后,得到一个包含所有图形的图形列表,对图形列表进行遍历,遍历到的图形只有在没有被分配掩膜的情况下才会被处理,对于列表中没被分配掩膜的图形,默认分配两层掩膜中的第一层。对于当前分配了掩膜的图形,首先会按照规则间距扩展来搜寻与该图形存在间距违例的所有图形,由于图形可能不是矩形,而是多边形,对于多边形的扩展,本发明所用的方法是基于边放大,而不是点放大,如图4所示。

[0056]

下面介绍具体的掩膜分配规则。

[0057]

步骤3.1,对图形列表进行遍历,若遍历到的当前图形未被分配掩膜,则将当前图形分配到双层掩膜当中的一层掩膜中;

[0058]

步骤3.2,根据间距规则搜寻与当前图形的间距违规的所有对比图形,若能够得到当前图形的所有对比图形列表,判断对比图形列表中是否有已经分配掩膜的对比图形,且与当前图形位于同一掩膜,则将当前图形与该对比图形作为一对冲突节点记录到冲突列表中,并执行下一步骤;若当前图形不存在对比图形列表,返回当前图形的上一级图形,重复步骤3.2直至上一级图形的对比图形列表中的图形被遍历完毕,或者返回步骤3.1直至图形列表中的所有图形均被分配掩膜后,再执行查找冲突环的步骤。

[0059]

步骤3.3,对对比图形列表进行遍历,将遍历到的当前对比图形分配到双重掩膜当中的另一层掩膜中,使当前图形与对比图形位于不同的掩膜,将当前对比图形作为当前图形返回步骤3.2。

[0060]

在步骤3.2中具体何时重复步骤3.2,何时返回步骤3.1需要看图形所在的级数,假设依据图形列表而被遍历到的图形称之为第一级节点,那么依据深度优先算法,对该第一级节点的对比图形列表进行遍历时,第二级节点可能也存在对比图形列表,第三级节点可能也存在对比图形列表,当第三级节点的对比图形列表被遍历到时,即遍历第四级节点时,如果第四级节点不存在对比图形列表,即某个节点不存在第五级节点时,那么此时返回步骤3.2,还需要遍历下一个第四级节点,直到第四级节点都遍历完毕,之后再返回第三级节点继续遍历第三级节点,以此类推,如果返回到第一级节点时,那么就需要返回到步骤3.1,对图形列表中的图形继续遍历。

[0061]

在上述返回的过程中,如果任意一级节点的对比图像列表中存在已分配掩膜的对比图形(节点),并且该对比图形与该级节点对应的图形在同一个掩膜上,则记录它们为一对冲突节点记录到冲突列表中。

[0062]

上述掩膜分配的过程中,由于本专利是实际分配掩膜的算法,并不是直接分配到掩膜实物上,因而在上述算法过程中,采用的是为图形标注不同颜色来区别具体是分配在那一块掩膜上。

[0063]

对于处理结束的图形,需要进行标记,对图形进行扩展,查询违例图形时会过滤标记的图形,避免已经处理过a-》b,又处理b-》a这种情况。分配掩膜后最终结果如图7所示。用节点图表示流程如图8所示。

[0064]

下面介绍查找冲突环的具体过程。

[0065]

如图2所示,根据间距规则找到每一对冲突节点中每个图形对应的间距违例列表,采用深度优先遍历方法对一对冲突节点中的两个图形的间距违例列表中的间距违例图形进行同步遍历,并添加到该对冲突节点的冲突环列表中,判断当前遍历的间距违例图形是否也存在于一对冲突节点中另一个图形的间距违例列表中,若存在,则将该间距违例图形加入到该对冲突节点的冲突环列表中。本发明可以采用多线程的方式,对冲突对进行并行寻找冲突环,对冲突对中的图形进行边放大间距规则值,即将图形边按法线方向平移xmin值,基于网格索引进行查询,获得两图形的间距违例图形列表,遍历两列表判断有无一致图形,如果有,说明找到一个冲突环,存储此冲突环。如果不是一致图形,则作为下轮搜索的起点,当发现以下条件时结束:超过最大搜索深度;任一图形的间距违例列表为空;两图形一致。

[0066]

在一个实施例中,创建一个存放奇数环上图形的列表,设置搜寻最大层深,搜寻奇数环超过此层深便不再进行查找。将两图形加入列表中,对冲突对两图形都按照规则间距进行扩展,得到二者各自的间距违例列表,对两列表所有图形进行判断,判断两列表中有无一致图形,如果有,说明找到了奇数环,如图9所示;将对应图形加入存放奇数环的列表中,将此奇数环加入存放奇数环的数组中,然后再将此图形从存放奇数环的列表中删去,继续遍历两图形的间距违例列表,检查是否还存在其他奇数环。接下来将上述流程中检查的所有图形设置为访问过,避免重复访问,采用深度优先搜索方法,对于两间距违例列表中的图形,各选出一个图形,判断是否是其他冲突对,如图10所示,如果是,不处理;两图形作为新的冲突对,层深减一,重复上述流程寻找一致的图形,如图11所示;搜索流程全部结束后,将所有图形设置为未访问过,防止影响到别的冲突对。

[0067]

最终报告所有违例,如附图12所示。

[0068]

本发明还保护双重图形光刻方法,该双重图形光刻方法在对电路版图进行光刻之前,采用上述技术方案的电路版图的拆分验证方法查找所有冲突环,并对电路版图的设计进行改进,直至所述电路版图不存在冲突环,再对电路板进行光刻。

[0069]

本发明还保护计算机可读存储介质,用于存储计算机程序,该计算机程序运行时执行上述技术方案的电路版图的拆分验证方法。

[0070]

以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1