一种面向高层次综合的动态内存管理装置及方法与流程

1.本发明涉及计算机硬件定制技术领域,尤其涉及一种面向高层次综合的动态内存管理装置及方法。

背景技术:

2.以fpga为代表的定制硬件在提高计算性能方面表现优秀,可以提供超过cpu几个数量级的性能提高。尽管fpga拥有性能优势和成熟的商业体系,但是由于fpga应用是基于硬件逻辑表示的rtl语言进行开发,编写周期往往很长。高层次综合技术是为加速fpga开发而提出的一门语言。高层次综合使用更高抽象层次的c/c++等软件代码开发硬件,使得开发人员可以从繁琐的rtl语言中解脱出来,让没有硬件开发经验的程序员也可以参与到硬件开发中来。尽管高层次综合的性能在很多方面已经接近手工编写的rtl语言,然而软件代码中的一些常见写法高层次综合中并不支持,比如动态内存管理(malloc/free)。这部分代码虽然在总体中出现频率不高,但却是代码逻辑中的关键环节,缺少对这部分代码的映射迫使开发者对代码进行大量的重构,来用静态内存管理替代原来的动态内存管理。静态内存分配除了会造成大量代码重构之外,还会迫使程序员按照内存使用过程中的最大值来占用内存,导致内存利用率低,硬件资源开销大等问题。因此使用动态内存管理十分必要。

3.内存管理是操作系统最重要的任务之一,并且已经有了很多成熟的方案,比如sequential fits、buddy system、bitmapped fits等等。然而fpga平台并没有一个通用的操作系统,传统操作系统的软件方式直接向fpga移植执行效率并不高,例如buddy system方式由于速度快过程简单等优势成为了操作系统上最主流的管理方式,然而直接移植到fpga硬件平台上则会因为内存带宽限制导致较长时延。

4.当前fpga平台动态内存管理主要有基于fixed size、bitmap和buddy system的三种分配方式,这三种方式都不适合对dram的gb级别的内存空间进行管理。fixed size方式只能够分配固定长度的内存块,导致灵活性很差,会造成大量的内存碎片导致内存利用率低等问题;bitmap方式使用向量中的每个bit来对应固定长度的地址块,通过查找向量来反转相应数量的bit来进行内存的分配和回收。这种方式并不适合gb级别的dram内存管理,因为gb级的内存空间会导致向量很长,而每次分配最坏情况下会遍历整个向量,导致分配效率很低;buddy system方式利用树结构来加速对bitmap的查找,但是随着树高度增加会导致时钟频率严重下降,因此同样不适合对大的dram进行管理。

5.公开号为cn109324904a的中国专利公开了一种动态内存管理方法及装置,其中,该动态内存管理方法中包括:s10判断当前所需内存管理类型;s21若判断需要在typedarray中存入一数据对象,进一步判断typedarray中是否存在未存储空间,typedarray中预分配有第一预设长度的存储单元;若是,跳转至步骤s31;s31根据typedarray中的当前数据长度,按照存储顺序将该数据对象存入一存储单元中,并将当前数据长度自增1。其通过typedarray对javascript动态内存进行管理,大幅度降低了javascript引擎分配内存/垃圾回收的频次,提高了javascript性能。但是,该发明也不适

合gb级别的dram内存管理,

6.公开号为cn103377134a的中国专利公开了基于哈佛结构的动态内存管理系统,其包含一个哈佛结构处理器,程序总线,数据总线,程序存储器,数据存储器,动态内存管理单元以及由内存管理单元控制的动态存储器。根据系统的应用需要,可以由程序存储器中的程序配置动态内存管理单元,使得动态存储器能够被程序总线或数据总线访问,实现程序存储空间和数据存储空间的动态分配,从而最大限度的提高系统的性能。但是,该发明也不适合gb级别的dram内存管理。

7.如上所述,已公开的发明专利均没有解决本发明提出的缺陷。本发明旨在提出一种面向高层次综合的动态内存管理装置及方法。

8.此外,一方面由于对本领域技术人员的理解存在差异;另一方面由于申请人做出本发明时研究了大量文献和专利,但篇幅所限并未详细罗列所有的细节与内容,然而这绝非本发明不具备这些现有技术的特征,相反本发明已经具备现有技术的所有特征,而且申请人保留在背景技术中增加相关现有技术之权利。

技术实现要素:

9.现有的fpga平台动态内存管理主要有基于fixed size、bitmap和buddy system的三种分配方式,这三种方式都不适合对dram内存空间进行管理。fixed size方式只能够分配固定长度的内存块,导致灵活性很差,会造成大量的内存碎片导致内存利用率低等问题;bitmap方式使用向量中的每个bit来对应固定长度的地址块,通过查找向量来反转相应数量的bit来进行内存的分配和回收。这种方式并不适合gb级别的dram内存管理,因为gb级的内存空间会导致向量很长,而每次分配最坏情况下会遍历整个向量,导致分配效率很低;buddy system方式利用树结构来加速对bitmap的查找,但是随着树高度增加会导致时钟频率严重下降,因此同样不适合对大的dram进行管理。

10.针对现有技术之不足,本发明提供了一种面向高层次综合的动态内存管理装置,所述装置至少包括:若干搜索缓存模块和若干修改写回模块,所述搜索缓存模块与dram存储模块和bram缓存模块分别建立连接关系,修改写回模块与dram存储模块和bram缓存模块分别建立连接关系,所述bram缓存模块用于缓存搜索路径上的节点信息并暂存对节点的修改信息;所述搜索缓存模块根据接收的操作符和节点地址从所述dram存储模块中读取节点数据并写入所述bram缓存模块,所述修改写回模块从所述bram缓存模块中读取节点数据并写回dram存储模块。本发明通过对高层次综合中动态内存管理需求提供支持,减少了代码编写工作量,提高了内存利用率。

11.优选地,所述dram存储模块至少被划分为静态存储区、动态存储区和多路搜索树存储区;所述静态存储区用于存储在写入后不会被释放的信息,所述动态存储区属于被动态管理的内存区域;所述多路搜索树存储区用于存储搜索树结构信息,其中,基于空闲节点链表以节点为粒度对搜索树结构信息进行管理,在提取节点时,所述多路搜索树存储区从所述空闲节点链表的头部提取下一个节点,在释放节点时,把空节点重新插入到所述空闲节点链表的头部。本发明使用搜索树结构来管理空闲内存块,并且设计了相应的内存分配、回收算法和双向流水线,分配和回收内存块都可以在树高次内存读写内完成,同时避免了对搜索树进行回溯遍历。

12.优选地,若干所述搜索缓存模块按照与搜索树的层数相同的方式设置为多层结构,在其中一个所述搜索缓存模块分析所述操作符和所述节点数据后,该搜索缓存模块会向相邻的另一个搜索缓存模块传递对应的操作符和待读取的节点地址。

13.优选地,若干所述修改写回模块按照与搜索树的层数相同的方式设置为多层结构,所述修改写回模块根据接收的操作符对所述bram缓存模块中的节点进行修改,并且将节点数据写回到所述dram存储模块中的所述多路搜索树存储区,在其中一个修改写回模块对操作符和读取的节点进行分析后,该修改写回模块向相邻的修改写回模块传递相应的操作符。

14.优选地,若干所述搜索缓存模块的数据的层级传递顺序与若干所述修改写回模块的数据的层级传递顺序相反。

15.优选地,所述多路搜索树存储区对内存的管理方式被配置为:基于搜索树结构对内存中的空闲内存块进行管理;其中,所述空闲内存块为内存的最小单位,并且以空闲内存块的首地址和长度来表示该空闲内存块。

16.本发明把内存按照空闲内存块的方式管理,利用内存块的首地址和长度来表示一个空闲内存块,不仅可以对几十mb的bram进行管理,同时也支持对16gb的dram进行管理,对bram的占用率很低,避免了对计算单元的资源挤占。

17.优选地,所述装置还包括切换模块,所述切换模块与位于底层的搜索缓存模块和位于底层的修改写回模块分别建立连接关系,当位于底层的所述搜索缓存模块将释放内存块的操作符传递至所述切换模块中后,所述切换模块将操作符的传递顺序切换为相反顺序并且将操作符传递至与其连接的修改写回模块。

18.优选地,所述装置还包括请求队列模块,所述请求队列模块与若干所述搜索缓存模块建立连接关系,所述请求队列模块用于缓存由计算单元发送的内存分配请求和内存释放请求,其中,由于内存不足造成的失败的分配请求被缓存在队列中,出队列的分配请求被加入流水线中参与计算。

19.本发明还提供一种面向高层次综合的动态内存管理方法,所述方法至少包括:将若干所述搜索缓存模块按照与搜索树的层数相同的方式设置为多层结构,将若干所述修改写回模块按照与搜索树的层数相同的方式设置为多层结构,所述搜索缓存模块根据上一层传递的操作符和节点地址从dram存储模块中读取节点数据并写入bram缓存模块,所述bram缓存模块缓存搜索路径上的节点信息并暂存对节点的修改信息;所述修改写回模块从所述bram缓存模块中读取节点数据并写回所述dram存储模块。

20.优选地,所述方法还包括:所述dram存储模块至少被划分为静态存储区、动态存储区和多路搜索树存储区;所述静态存储区用于存储在写入后不会被释放的信息,所述动态存储区属于被动态管理的内存区域;所述多路搜索树存储区用于存储搜索树结构信息,所述多路搜索树存储区对内存的管理方式被配置为:基于搜索树结构对内存中的空闲内存块进行管理;其中,所述空闲内存块为内存的最小单位。

21.本发明的方法,用搜索树结构来管理空闲内存块,设计了相应的内存分配、回收算法和双向流水线,分配和回收内存块都可以在树高次内存读写内完成,同时避免了对搜索树进行回溯遍历,显著提高了内存管理的效率。

附图说明

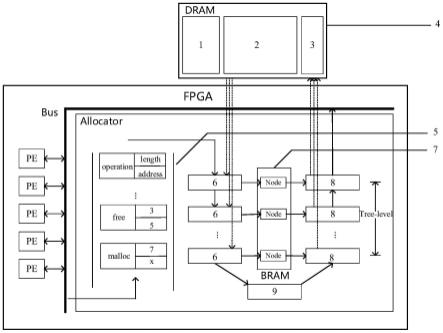

22.图1是本发明优选的面向高层次综合动态内存管理装置的硬件结构的示意图;

23.图2是本发明优选的空闲内存块映射的示意图;

24.图3是本发明优选的多路搜索树逻辑结构的示意图;

25.图4是本发明优选的多路搜索树的存储结构的示意图。

26.附图标记列表

27.1:静态存储区;2:动态存储区;3:多路搜索树存储区;4:dram存储模块;5:请求队列模块;6:搜索缓存模块;7:bram缓存模块;8:修改写回模块;9:切换模块。

具体实施方式

28.下面结合附图进行详细说明。

29.针对现有技术当前无法适合gb级别的dram内存管理,导致灵活性很差、内存利用率低、内存空间会导致向量长、分配效率低、时钟频率严重下降等的缺陷,本发明提供一种面向高层次综合的动态内存管理装置及方法,旨在能够对dram级别内存进行动态管理。

30.本发明的面向高层次综合的动态内存管理装置,其硬件结构如图1所示。

31.一种面向高层次综合的动态内存管理装置,包括请求队列模块5、若干搜索缓存模块6、bram缓存模块7、修改写回模块8和切换模块9。

32.请求队列模块5可以是专用集成芯片、处理器(cpu)、逻辑处理模块等等。请求队列模块5用于执行请求队列的具体方法步骤的程序编码。

33.搜索缓存模块6为按照预设的程序编码执行本发明的搜索缓存步骤的缓存器。

34.bram缓存模块7为按照预设的程序编码执行本发明的缓存步骤的缓存器。

35.修改写回模块8可以是专用集成芯片、处理器(cpu)、逻辑处理模块等等。修改写回模块8能够执行修改写回步骤的程序编码。

36.切换模块9可以是专用集成芯片、处理器(cpu)、逻辑处理模块等等。切换模块9能够执行本发明的切换操作的程序编码。

37.请求队列模块5与装置的接收端口连接,从而接收由接收端口输入的内存分配请求和内存释放请求并进行缓存。由于内存不足造成的失败的分配请求同样会被缓存在队列中,出队列的请求会被加入流水线中参与计算。例如,运算单元pe通过axi总线和分配单元通信发送内存分配和回收请求信息至接收端口,接收内存地址和内存释放结果。请求队列模块5中,存有一个申请3个内存单元的和一个在5号内存单元开始3个长度内存块释放请求。

38.dram存储模块4为dram动态随机存取存储器。dram存储模块4至少被划分为静态存储区1、动态存储区2和多路搜索树存储区3。静态存储区1用于存储在写入后不会被释放的信息。具体地,静态存储区1用于存储一写不会被释放的信息,例如各种计算参数。动态存储区2属于被动态管理的内存区域。多路搜索树存储区3用于存储搜索树结构信息。其中,多路搜索树存储区3基于空闲节点链表以节点为粒度对搜索树结构信息进行管理。在提取节点时,多路搜索树存储区3从空闲节点链表的头部提取下一个节点,在释放节点时,把空节点重新插入到空闲节点链表的头部。

39.请求队列模块5与每一个搜索缓存模块6分别建立连接关系。优选地,若干搜索缓

存模块6按照与搜索树的层数相同的方式设置为多层结构,如图1所示。在其中一个搜索缓存模块6分析操作符和节点数据后,该搜索缓存模块6按照预设的顺序会向相邻的另一个搜索缓存模块6传递对应的操作符和待读取的节点地址。如图1所示,若按照图示箭头方向,从上至下计算搜索缓存模块6的层级序号。操作符和节点数据是从上一层的搜索缓存模块6向下一层的搜索缓存模块6传递。

40.每一个搜索缓存模块6与bram缓存模块7建立连接关系。每一个搜索缓存模块6与dram存储模块4建立连接关系。搜索缓存模块6根据上一层搜索缓存模块传递的操作符和节点地址从dram存储模块4中读取节点数据并写入bram缓存模块7。bram缓存模块7用于缓存搜索路径上的节点信息并暂存对节点的修改信息。

41.优选地,若干修改写回模块8按照与搜索树的层数相同的方式设置为多层结构。bram缓存模块7与每一个修改写回模块8建立连接关系。每一个修改写回模块8与dram存储模块4建立连接关系。

42.修改写回模块8根据接收的操作符对bram缓存模块7中的节点进行修改,并且将节点数据写回到dram存储模块4中的多路搜索树存储区3。

43.位于底层的搜索缓存模块6和位于底层的修改写回模块8分别与切换模块9建立连接关系。当位于底层的搜索缓存模块6将释放内存块的操作符传递至切换模块9中后,切换模块9将操作符的传递顺序切换为相反顺序并且将操作符传递至与其连接的修改写回模块8。

44.本发明中以图1为例,搜索树结构的层数为3,则搜索缓存模块6的层数为3,修改写回模块8的层数为3。将层级顺序从上至下标记为1、2、3。搜索缓存模块6的操作符和节点数据的层级传递顺序为1

→2→

3。修改写回模块8的操作符的层级传递顺序为3

→2→

1。

45.修改写回模块8从bram缓存模块7中读取节点数据并写回dram存储模块4。在其中一个修改写回模块8对操作符和读取的节点进行分析后,该修改写回模块8向相邻的修改写回模块传递相应的操作符。以图1所示的传递顺序为例,若按照图示箭头方向,从上至下计算修改写回模块8的层级序号。操作符是从底层的修改写回模块8向上一层的修改写回模块8传递。

46.如图1所示,若干搜索缓存模块6的数据的层级传递顺序与若干修改写回模块8的数据的层级传递顺序相反。本发明中的图1的层级传递顺序仅为示例,不作为唯一的实施方式。

47.优选地,多路搜索树存储区3对内存的管理方式被配置为:基于搜索树结构对内存中的空闲内存块进行管理。

48.空闲内存块为内存的最小单位,并且以空闲内存块的首地址和长度来表示该空闲内存块。如图2所示,首地址为22、长度为7的内存块,可以表示为(22,7),其他内存块同理。

49.如图3所示,每个搜索树的树节点中保存有多个空闲内存块。所有树节点中的空闲内存块数量有一个共同的上下界。当空闲内存块数量多于上界时,树节点会进行分裂,当空闲内存块少于下界时,树节点会进行合并,使得每一个树节点中的空闲内存块数量重新满足上下界的约束。

50.树节点进行分裂时,会向上层父节点插入一个空闲内存块,树节点合并时,会向上层父节点删除一个空闲内存块。

51.多路搜索树是一棵有序的搜索树,每一个树节点中的空闲内存块按首地址有序排列。树节点之间所有的空闲内存块的首地址按照中序有序排列。如图3所示,搜索树设置上界为2下界为1,并且节点3d内的空闲地址块(1,1)(10,3)按照首地址大小有序排列,节点3a-3g之间同样满足中序有序。

52.多路搜索树的数据项配置如图4所示,包括:树节点中有效空闲内存块总数、空闲树节点链表索引、空闲内存块数组、子节点指针数组、子节点最大内存块长度数组、本节点最大内存块长度、本节点最大空闲内存块索引、子节点最大内存块索引和子节点最大内存块长度。

53.使用搜索树结构来管理空闲内存块,设计了相应的内存分配操作、回收内存操作算法和双向流水线,分配和回收内存块都可以在树高次内存读写内完成,同时避免了对搜索树进行回溯遍历。

54.本发明中,内存分配操作用于通过双向流水线删除至少一个内存块。回收内存操作用于通过双向流水线插入至少一个内存块。

55.本发明按照双向流水线方式对搜索树进行计算,具体步骤如下所示。

56.s1:搜索缓存,由搜索缓存模块6执行。

57.搜索缓存模块6根据指令对搜索树进行不同类型的搜索,并且缓存需要在修改写回模块8使用的数据到bram缓存模块7中。

58.搜索缓存模块6的执行方向是由搜索树根部向叶子的方向进行搜索。需要缓存的数据至少包括:节点、节点地址、兄弟节点地址、搜索路径、双亲节点的内存块和搜索的方向。搜索缓存模块6需要向下一层搜索缓存模块6传递的数据有:操作符、被释放内存块地址、被释放内存块长度、被搜索的下一层节点的地址、下一层节点的兄弟节点的地址、传向下一层节点的空闲内存块等。

59.具体的,搜索缓存的方式如下。

60.释放内存块操作,按地址大小对搜索树进行搜索,按大小找到向下搜索的路径,判断被释放的内存块能否和节点内相邻的内存块合并。如果可以和左右两个内存块合并,进行合并后,向下查找可以替代的后继内存块。如果只可以和一边内存块合并,向下查找后继或者前驱。如果不能合并,继续向下传递释放内存块指令。如果内存块和其他内存块有重叠则传递释放失败操作。

61.申请内存操作,根据节点内的最大内存块索引判断节点内最大内存块是否可以完成分配,如果大于申请长度,则完成分配,向下传递分配成功操作。如果本节点的最大内存块等于申请需求,向下查找后继内存块替换该内存块。如果本节点的最大内存块不能满足分配需求,根据子节点最大内存块索引,向下查找最大内存块。

62.查找前驱、查找后继、查找替代内存块、分配失败、释放失败根据查找方向向下传递相同操作。

63.对搜索树的查找支持优先分配最大内存块的worst fits和优先分配第一个满足需求的内存块的first fits方式。同时基于空闲内存块的表示方法避免了内碎片的产生,能够提高内存的利用率。

64.例如,以回收内存块(3,4)为例,搜索缓存模块6首先缓存节点3a,根据首地址比较得到下一层需要加载的节点3b,同时内存块(3,4)不能和(30,2)内存块合并,因此向下一层

搜索缓存模块6传递同样的搜索操作。后续搜索缓存模块读入节点3b、3d,进行相同操作。

65.s2:操作切换,由操作切换模块9执行。把向下的搜索缓存操作顺序转换为向上的修改写回操作顺序,该步骤不涉及具体节点和访存。

66.释放内存块操作被传递到操作切换模块9中,被切换为插入操作向上一层继续传递。

67.具体的,操作切换的方式如下。

68.释放内存操作,向上一层修改写回模块8传递插入操作,被释放的内存块转换为向上一层插入的内存块,向上传递释放成功操作。

69.查找前驱、查找后继,若父空闲内存块不是前驱或者后继,向上传递释放成功操作;若父空闲内存块是前驱或者后继,向上一层传递删除空闲内存块操作。

70.其他操作转换为对应的失败操作向上一层传递。

71.s3:修改写回,由修改写回模块8执行。

72.向上一层修改写回模块8传递对下一层节点进行的修改并写回,把缓存在bram缓存模块7中的数据写回到dram中。执行的方向和步骤s1相反,并且路径与步骤s1相同。

73.向上一层修改写回模块8传递的数据有:操作符、被分配的地址、节点和兄弟节点的地址、被分裂出的节点地址、用来合并或者替换的内存块、向上插入的内存块、节点以及兄弟节点的最大内存块等。

74.具体的,修改写回的具体方式如下。

75.替换内存块操作,将子节点上传的内存块和节点对应内存块交换后更新本节点最大内存块长度和本节点最大内存块索引。

76.删除内存块操作,将节点内对应的内存块删除,如果删除后节点中内存块数量少于下界,会插入父节点的对应内存块,兄弟节点上传一个内存块到父节点,向上传递替换内存块操作。如果兄弟节点内存块不足,会将两节点合并,并插入父节点内存块,向上传递删除内存块操作。

77.插入内存块操作,插入子节点的内存块,若插入后大于上界,对节点进行分裂,并插入一个内存块到父节点,向上传递插入内存块操作。若不大于上界,向上传递完成操作。

78.替换前驱、后继内存块操作,替换对应内存块,更新节点最大内存块长度,向上传递完成操作。

79.例如,当插入操作被传递到节点3d时,超过了节点的上界2,因此对节点进行分裂并插入内存块到父节点3b中。同样的对3b,3a进行同样的判断和操作。

80.经过上述步骤后,对内存块(3,4)的回收完成。对内存的分配操作过程和回收操作步骤类似,即转换成经过双向流水线对搜索树的删除和插入操作。因此不再赘述。

81.需要注意的是,上述具体实施例是示例性的,本领域技术人员可以在本发明公开内容的启发下想出各种解决方案,而这些解决方案也都属于本发明的公开范围并落入本发明的保护范围之内。本领域技术人员应该明白,本发明说明书及其附图均为说明性而并非构成对权利要求的限制。本发明的保护范围由权利要求及其等同物限定。本发明说明书包含多项发明构思,诸如“优选地”、“根据一个优选实施方式”或“可选地”均表示相应段落公开了一个独立的构思,申请人保留根据每项发明构思提出分案申请的权利。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1