一种用于磁共振系统的快速同步扫频波源装置及方法与流程

1.本发明涉及磁共振技术领域,特别涉及一种用于磁共振系统的快速同步扫频波源装置及方法。

背景技术:

2.磁共振技术是一门关于电磁波操控自旋的科学方法,通过射频场激励样品产生共振现象,从而实现对样品的特性探测。其能够在不对被测样品造成损害的情况下探测其微观尺度上的物质单元的组成、结构以及动力学性质。近年来,随着傅里叶变换波谱学、二维谱、磁共振成像等技术的发展,磁共振技术在信息科学、材料、化学、生物和医疗等诸多领域得到重要而广泛的运用。例如,应用于量子精密测量领域中的光探测磁共振技术,射频源通过扫频来为磁共振系统提供连续变化、没有间断的激励信号,对样品进行磁共振测量,最终准确获得目标色心的自旋磁共振频率。

3.然而,随着磁共振系统集成度、复杂度的提高,激励信号和探测设备的同步性至关重要。尤其在量子精密测量领域,以基于nv色心的量子实验系统为例,其系统所集成的设备主要包含波源,脉冲发生器以及采集卡等。为了准确获得nv色心的共振频率,波源在扫频的过程中需要与其他仪器设备进行精确同步,保证实验参数的一一对应。如果采用市面上的商用波源,我们只能通过使用计算机来协调波源与其他实验设备。这种方式包含了大量的通信以及系统的复位时间,大大增加了时间开销。

4.同时,不同频点之间切换的死时间也十分重要。同样,以基于nv色心的量子实验系统为例。由于微波源的输出功率等因素对电子自旋能级之间翻转时间的影响,每个频点所需要的持续时间仅在us甚至是ns量级。目前,商用的波源多采用基于压控振荡器(voltage controlled oscillator,vco)的锁相环来产生稳定的输出信号。但是,在改变输出频率时,由于锁相环重新锁定的时间较长导致切换不同频点时的死时间增加,从而增加了实验时间开销。采用直接数字合成器(direct digital synthesizer,dds)可以有效缩短不同频点之间切换的死时间。基于dds技术的波源可以在切换频率的一个周期内,通过相位累加器中的相位信息改变,修改驱动adc的数据,从而改变输出频率,实现快速切频。例如,对于一个基于dds技术且工作时钟为145mhz的波源在改变频率时,输出延时在ns级。

技术实现要素:

5.本发明的目的在于提供一种用于磁共振系统的快速同步扫频波源装置及方法,以克服现有技术中的不足。

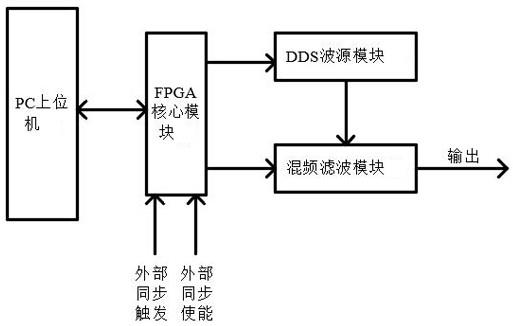

6.为实现上述目的,本发明提供如下技术方案:本发明公开了一种用于磁共振系统的快速同步扫频波源装置,包括pc上位机、fpga核心模块、直接数字合成器波源模块、混频滤波模块;所述pc上位机与fpga核心模块进行通讯,用于设置直接数字合成器波源输出频率数据,以及通过软件端复位、开始和暂停系统;

所述fpga核心模块包括上位机数据缓冲模块、锁相环驱动模块、频率调谐字主存、直接数字合成器波源初始化只读存储器、数据输出控制模块、直接数字合成器波源控制模块、数据选择器模块、快速同步模块;所述上位机数据缓冲模块连接所述锁相环驱动模块、频率调谐字主存和数据输出控制模块,所述数据输出控制模块连接所述快速同步模块、频率调谐字主存、直接数字合成器波源初始化只读存储器和直接数字合成器波源控制模块,所述频率调谐字主存、直接数字合成器波源初始化只读存储器和直接数字合成器波源控制模块均与数据选择器模块连接;所述快速同步模块提供外部同步使能接口和外部同步触发接口;所述fpga核心模块,用于初始化直接数字合成器波源,输出控制直接数字合成器波源的频率调谐字数据,切换直接数字合成器波源的工作模式,控制直接数字合成器波源的输出、复位、开始和暂停;所述直接数字合成器波源模块和混频滤波模块中各有一个锁相环,使用fpga内部时钟管理器 ip核,创建时钟源,用于锁相环工作时的参考时钟。

7.作为优选的,pc上位机将频率数据打包并发送给fpga的频率调谐字主存中存储;通过软件触发fpga核心模块,输出控制直接数字合成器波源的控制信号;实时读取当前输出的频率数据;和/或,所述上位机数据缓冲模块用于缓冲上位机发送的频率调谐字数据以及驱动锁相环的数据和软件触发信号、全局复位信号、系统开始或暂停信号。

8.作为优选的,所述锁相环驱动模块用于驱动直接数字合成器波源模块、混频滤波模块中的锁相环;其中,直接数字合成器波源模块中的锁相环输出的时钟信号,用于直接数字合成器波源模块的参考时钟;混频滤波模块中的锁相环输出的时钟信号,用于混频滤波模块混频时所需的本振信号;和/或,所述频率调谐字主存用于存储pc上位机计算完成的频率调谐字频率调谐字,在每一次接收到触发信号时,输出一个新地址中的频率调谐字数据。

9.作为优选的,所述直接数字合成器波源初始化只读存储器中存储了初始化直接数字合成器波源的数据,在工作之前对直接数字合成器波源中的寄存器进行初始化;和/或,所述数据输出控制模块用于管理频率调谐字主存输出、直接数字合成器波源初始化只读存储器输出以及直接数字合成器波源控制模块输出,并接收pc上位机数据缓冲模块的软件触发信号以及快速同步模块的快速同步触发信号;和/或,所述直接数字合成器波源控制模块用于配置直接数字合成器波源工作模式,复位直接数字合成器波源,直接数字合成器波源输出使能脉冲以及对功能端口的控制。

10.作为优选的,所述快速同步模块的外部同步使能接口用于同步复位频率调谐字主存中地址数据,所述外部同步触发接口接收触发脉冲,更新频率调谐字主存地址数据,输出新地址中的频率调谐字数据,实现快速同步触发扫频。

11.作为优选的,所述直接数字合成器波源模块包括直接数字合成器以及锁相环,锁相环的时钟输出用于直接数字合成器波源的参考时钟,所述锁相环的参考时钟是由fpga内部时钟管理器创建的50mhz的时钟源,fpga内部时钟为系统的源时钟。

12.作为优选的,所述混频滤波模块包括锁相环以及混频器和滤波器,锁相环输出的信号用于混频器的本振信号,混频器接收锁相环的输出信号以及直接数字合成器波源模块输出的信号,混频后的信号经过滤波器,获得单一输出,无谐波的频率信号。

13.本发明公开了一种用于磁共振系统的快速同步扫频方法:包括如下步骤:

s1、 pc上位机计算控制直接数字合成器波源输出频率的频率调谐字数据,计算控制直接数字合成器波源模块中的锁相环输出频率的配置数据以及混频滤波模块中的锁相环输出频率的配置数据,将这些数据打包发送给fpga核心模块进行处理,fpga核心模块对频率调谐字数据进行存储,并驱动锁相环输出的时钟信号,用于直接数字合成器波源工作的参考时钟频率以及混频滤波模块的混频本振信号;s2、pc上位机发送系统复位指令进行复位后,发送直接数字合成器波源初始化指令到fpga核心模块,fpga核心模块内部的数据输出控制模块发送初始化信号,内部的直接数字合成器波源控制模块采集到初始化信号后,功能配置信号设置为初始化模式,直接数字合成器波源控制模块向内部的数据选择器模块发送选择信号,用于选择输出直接数字合成器波源初始化只读存储器中的数据;直接数字合成器波源初始化只读存储器采集到初始化信号后,使能直接数字合成器波源初始化只读存储器,并且接收来自数据控制模块发送的地址信号,输出直接数字合成器波源初始化只读存储器中存储的数据,完成对直接数字合成器波源的初始化后,数据输出控制模块复位选择信号,释放直接数字合成器波源初始化只读存储器,直接数字合成器波源控制模块输出的功能配置信号设置为频率输出模式;s3、发送同步使能脉冲给fpga核心模块内部的快速同步模块,在fpga核心模块内部,检测到脉冲上升沿后,数据控制模块将频率调谐字主存中的地址复位;s4、完成同步使能脉冲发送后,所述fpga核心模块内部的快速同步模块的外部同步触发接口采集脉冲触发信号。

14.作为优选的,所述步骤s1中fpga核心模块具体处理过程为:通过fpga核心模块内部的上位机数据缓冲模块,将频率调谐字数据分发给fpga核心模块内部的频率调谐字主存,存储频率调谐字数据;将所述锁相环输出频率的配置数据发送给锁相环驱动模块,驱动锁相环工作,锁相环输出的时钟信号,经滤波器输出后,用于直接数字合成器波源工作的参考时钟频率以及混频滤波模块的混频本振信号。

15.作为优选的,所述步骤s4具体过程为:所述fpga核心模块内部的快速同步模块对触发脉冲信号进行上升沿检测,一旦检测到触发脉冲信号的上升沿,快速同步模块向数据控制模块发送数据输出指令,所述数据控制模块将地址数据发送给频率调谐字主存,由频率调谐字主存发送频率数据经数据选择器模块输出给直接数字合成器波源采样端口;数据保持一段时间后,由直接数字合成器波源控制模块向直接数字合成器波源发送输出脉冲信号,直接数字合成器波源采集到输出脉冲信号,并输出频率调谐字数据设定的频率信号。

16.本发明的有益效果:本发明提供了一种用于磁共振系统的、支持快速外触发同步的波源装置,该装置具备切频死时间短、输出频率高、输出带宽高的优点,该装置可以通过一个外触发数字接口来让波源实时获取当前所需的频率从而提高实验效率,外部同步触发接口可以接收ns级脉冲触发信号,当ram读取到最后一个ftw数据时,数据控制模块将地址复位,并输出该地址下的ftw,最终实现快速同步扫频目的。

附图说明

17.图1是一种用于磁共振系统的快速同步扫频波源装置系统框图;图2是本发明实施例提供的fpga内部系统设计图;图3是本发明快速同步时序设计图。

具体实施方式

18.为使本发明的目的、技术方案和优点更加清楚明了,下面通过附图及实施例,对本发明进行进一步详细说明。但是应该理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限制本发明的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本发明的概念。

19.如图1、图2所示,本发明实施例提供了一种用于磁共振系统的快速同步扫频波源装置,包括pc上位机,fpga核心模块,dds波源模块,混频滤波模块。

20.pc上位机与fpga核心模块进行通讯,主要用于设置dds波源输出频率数据,以及通过软件端复位、开始或暂停系统。pc上位机将频率数据打包并发送给fpga的频率调谐字ftw(frequency tuning word,频率调谐字) ram(random access memory,随机存取存储器,即主存)中存储;可通过软件触发fpga核心模块,输出控制dds波源的数据;实时读取当前输出的频率;使用fpga内部的时钟管理器(clock management,cmt)ip核输出50mhz时钟,用于外部dds波源以及混频滤波模块中的pll工作参考时钟。

21.fpga核心模块,用于初始化dds波源,输出控制dds波源的ftw数据,切换dds波源的工作模式,控制dds波源的输出、复位、开始和暂停等;设计了外部同步使能接口、外部同步触发接口,以实现快速同步扫频。

22.所述fpga核心模块包括上位机数据缓冲模块,锁相环(phase locked loop,pll)驱动模块,ftw ram,dds波源初始化rom(read-only memory,只读存储器),数据输出控制模块,dds波源控制模块,mux(multiplexer,数据选择器)模块,快速同步模块;所述快速同步模块提供了两个外部接口,包括外部同步使能接口,外部同步触发接口。外部同步使能接口用于同步复位ftw ram中地址数据,外部同步触发接口接收触发脉冲,更新ftw ram地址数据,输出新地址中的ftw数据,实现快速同步触发扫频。

23.所述上位机数据缓冲模块用于缓冲上位机发送的ftw数据以及驱动pll的数据和软件触发信号、全局复位信号、系统开始或暂停信号等。

24.所述pll驱动模块用于驱动dds波源模块、混频滤波模块中的锁相环,dds波源模块中的pll输出的时钟信号,用于dds波源模块的参考时钟;混频滤波模块中的pll其输出时钟信号,用于混频滤波模块混频时所需的本振信号。

25.所述ftw ram用于存储上位机计算完成的频率调谐字ftw,在每一次接收到触发信号时,输出一个新地址中的ftw数据。

26.所述dds波源初始化rom中存储了初始化dds波源的数据,在工作之前需要对dds波源中的寄存器进行初始化,保证dds波源可靠工作。所述数据输出控制模块用于管理ftw ram输出、dds波源初始化rom输出以及dds波源控制模块输出,并接收pc上位机数据缓冲模块的软件触发信号以及快速同步模块的快速同步触发信号。

27.所述dds波源控制模块包括配置dds波源工作模式,复位dds波源,dds波源输出使能脉冲以及一些功能端口的控制。

28.所述mux模块用于选择输出ftw数据还是dds波源初始化rom中的数据,选择信号由dds波源控制模块提供。

29.所述dds波源模块包括dds以及pll,pll的时钟输出用于dds波源的参考时钟。由于

pll的参考时钟是由fpga内部cmt创建的50mhz,即fpga内部时钟为系统的源时钟,保证了系统的可靠性。

30.所述混频滤波模块包括pll以及混频器和滤波器,pll输出的信号用于混频器的本振信号,混频器接收pll的输出信号以及dds波源模块输出的信号,混频后的信号经过滤波器,获得单一输出,无谐波的频率信号。

31.本发明实施例提供的一种用于磁共振系统的快速同步扫频装置,该案例以固态自旋(nv色心)实验平台为实施基础。由于固态自旋会受到来自外部的机械振动、微波展宽等因素影响,其自旋磁共振频率会发生一定偏移。因此在实验中,需要通过扫频测量的方式频繁地更新自旋磁共振频率,以确保实验结果的准确性。而扫频源的输出信号频率切换速度等,亦会影响自旋磁共振频率测量结果的准确性。为了评估本发明所提供的快速同步扫频装置的工作性能,本实施例将该扫频装置应用于固态自旋量子实验平台,并取得了良好的预期效果,自旋磁共振频率扫频测量实验耗时大大缩短。

32.本发明实施例提供了一种用于磁共振系统的快速同步扫频方法,包括如下步骤:步骤s1, pc上位机计算控制dds波源输出频率的ftw数据,计算控制dds波源模块中的pll输出频率的配置数据以及混频滤波模块中的pll输出频率的配置数据,将这些数据打包发送给fpga,通过上位机数据缓冲模块,将ftw数据分发给fpga内部的ftw ram,存储ftw数据;将pll配置数据发送给pll驱动模块,驱动锁相环pll工作,锁相环输出的时钟信号,经滤波器输出后,用于dds波源工作的参考时钟频率以及混频滤波模块的混频本振信号。

33.步骤s2,pc上位机发送系统复位指令,复位结束后,pc上位机发送dds波源初始化指令,数据输出控制模块发送初始化信号,dds波源控制模块采集到初始化信号后,功能配置信号设置为初始化模式,向mux模块发送选择信号,用于选择输出dds波源初始化rom中的数据;dds波源初始化rom采集到初始化信号后,使能dds波源初始化rom,并且接收来自数据控制模块发送的地址信号,输出dds波源初始化rom中存储的数据,完成对dds波源的初始化后,数据输出控制模块复位选择信号,释放dds波源初始化rom,dds波源控制模块输出的功能配置信号设置为频率输出模式。

34.步骤s3,如图3所示的快速同步时序,发送同步使能脉冲给设计好的fpga同步使能接口,在fpga内部,检测到脉冲上升沿后,数据控制模块将ftw ram中的地址复位。每次开始扫频前,通过发送一个同步使能脉冲,将ftw ram的地址复位,可以保证波源在扫频的过程中与其他仪器设备进行精确同步,保证实验参数的一一对应,准确获得nv色心的共振频率。

35.步骤s4,完成同步使能脉冲发送后,外部同步触发接口采集脉冲触发信号。快速同步模块对触发脉冲信号进行上升沿检测,一旦检测到触发脉冲信号的上升沿,快速同步模块向数据控制模块发送数据输出指令,数据控制模块将地址数据发送给ftw ram,由ftw ram发送频率数据经mux模块输出给dds波源采样端口。数据保持一段时间后,由dds波源控制模块向dds波源发送输出脉冲信号,dds波源采集到输出脉冲信号,并输出ftw数据设定的频率信号。dds波源输出的频率信号,经过混频滤波模块,最后得到输出信号,完成一次触发。从检测到触发脉冲的上升沿到最终的dds波源输出信号的时延为ns级。此外,外部同步触发接口可以接收ns级脉冲触发信号。外部同步触发接口接收连续触发信号,当ram读取到最后一个ftw数据时,数据控制模块将地址复位,并输出该地址下的ftw,最终实现快速同步

扫频目的。

36.最后将扫频装置输出的微波信号输入到微波辐射结构中。辐射结构将该信号转化为交变磁场,并作用于nv色心,以实现自旋操控;随后利用光电探测装置同步收集nv色心荧光信号,并发送至数据采集卡,通过pc上位机对nv色心荧光信号进行数据处理,从而获得其自旋磁共振频率。

37.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换或改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1