基于UVM的总线转换桥验证方法、装置、设备及存储介质与流程

基于uvm的总线转换桥验证方法、装置、设备及存储介质

技术领域

1.本发明涉及集成电路设计技术领域,尤其涉及一种基于uvm的总线转换桥验证方法、装置、设备及存储介质。

背景技术:

2.随着现代社会的高速发展,不论是民用领域还是军用领域各种先进电子产品的更新换代都离不开芯片的进步。据调查分析,大多数的soc(system on chip)功能芯片在第一次流片失败的原因是功能缺陷。由于soc的功能验证工作繁杂,从rtl(register transfer level)到芯片投片之前都要做充分的验证工作,因此提高验证工作效率、减小验证时间和提高验证完备性成为当务之急。

3.随着片上系统的发展,amba(advanced microcontroller bus architecture)总线协议也不断完善以满足人们对于系统高性能的要求,并且在复杂soc中,如果仅使用单个总线,会因为单总线挂载过多的ip(intellectual property)核而影响其时序收敛,因此,必须要搭建多条总线,而各总线间的信息交流必须通过总线转换桥,总线转换桥的大量使用显然会导致总线转换桥的验证难度不断提升。

4.目前系统级芯片设计规模不断扩大,soc芯片内部集成的ip模块数量也不断增加,因此在芯片开发中对芯片验证的要求越来越高,验证平台的搭建也更加复杂。因此,如何提高验证平台的工作效率成为目前亟待解决的技术问题。

技术实现要素:

5.本发明的主要目的在于提供一种基于uvm的总线转换桥验证方法、装置、设备及存储介质,旨在解决现有验证平台的工作效率低下的技术问题。

6.为实现上述目的,本发明提供一种基于uvm的总线转换桥验证方法,所述基于uvm的总线转换桥验证方法包括:

7.获取待测模块的输入参数,基于总线转换桥amba协议接口规范,确定所述输入参数对应的验证需求和验证策略;

8.基于所述验证需求和所述验证策略,确定目标接口,并基于uvm基类库,建立所述目标接口对应的约束激励;

9.基于验证模型和所述约束激励,对所述待测模块进行验证,输出验证结果。

10.进一步地,所述基于uvm基类库,建立所述目标接口对应的约束激励,包括:

11.基于所述uvm基类库中的序列类,创建各目标接口对应的序列项;

12.基于所述序列项,生成所述约束激励。

13.进一步地,所述基于验证模型和所述约束激励,对所述待测模块进行验证,输出验证结果,包括:

14.将所述约束激励输入至所述验证模型中,基于所述约束激励中的所述序列项,确定待验证功能以及各待验证功能的验证顺序;

15.基于所述序列项和所述验证顺序,依次对所述各待验证功能进行验证,输出所述验证结果,以完成所述待测模块的验证。

16.进一步地,所述基于所述验证需求和所述验证策略,确定目标接口,包括:

17.基于所述验证需求和所述验证策略,确定待验证功能;

18.基于所述待验证功能,确定待用验证模型;

19.基于所述待用验证模型,确定所述待用验证模型与所述待测模块之间的总线接口,作为所述目标接口。

20.进一步地,所述基于验证模型和所述约束激励,对所述待测模块进行验证,输出验证结果,还包括:

21.创建监测接口,基于所述监测接口,连接监视器和所述验证模型;

22.基于所述监视器,采样所述验证模型对所述待测模块的验证数据;

23.将所述验证数据发送至计分板中,获得所述计分板的所述验证数据和参考模型中的标准数据之间的对比结果,作为所述验证结果。

24.进一步地,所述基于所述监视器,采样所述验证模型对所述待测模块的验证数据,包括:

25.基于所述监视器,收集所述验证模型中各约束激励的代码覆盖率和功能覆盖率;

26.基于所述代码覆盖率和所述功能覆盖率,确定目标覆盖率;

27.在所述目标覆盖率达到预设覆盖率时,将当前采样数据作为所述验证数据。

28.进一步地,所述基于所述代码覆盖率和所述功能覆盖率,确定目标覆盖率之后,还包括:

29.在所述目标覆盖率未达到所述预设覆盖率时,对所述约束激励进行修改,确定测试盲区;

30.基于所述测试盲区,创建迭代约束激励,并基于所述迭代约束激励,对所述待测模型进行验证,获得所述当前采样数据和所述目标覆盖率,直至所述目标覆盖率达到所述预设覆盖率,将所述当前采样数据作为所述验证数据。

31.此外,为实现上述目的,本发明还提供一种基于uvm的总线转换桥验证装置,所述基于uvm的总线转换桥验证装置包括:验证需求确定模块,用于获取待测模块的输入参数,基于总线转换桥amba协议接口规范,确定所述输入参数对应的验证需求和验证策略;约束激励建立模块,用于基于所述验证需求和所述验证策略,确定目标接口,并基于uvm基类库,建立所述目标接口对应的约束激励;验证结果输出模块,用于基于验证模型和所述约束激励,对所述待测模块进行验证,输出验证结果。

32.此外,为实现上述目的,本发明还提供一种基于uvm的总线转换桥验证设备,所述基于uvm的总线转换桥验证设备包括处理器、存储器、以及存储在所述存储器上并可被所述处理器执行的基于uvm的总线转换桥验证程序,其中所述基于uvm的总线转换桥验证程序被所述处理器执行时,实现如上述的基于uvm的总线转换桥验证方法的步骤。

33.此外,为实现上述目的,本发明还提供一种计算机可读存储介质,所述计算机可读存储介质上存储有基于uvm的总线转换桥验证程序,其中所述基于uvm的总线转换桥验证程序被处理器执行时,实现如上述的基于uvm的总线转换桥验证方法的步骤。

34.本发明提供一种基于uvm的总线转换桥验证方法,所述方法获取待测模块的输入

参数,基于总线转换桥amba协议接口规范,确定所述输入参数对应的验证需求和验证策略;基于所述验证需求和所述验证策略,确定目标接口,并基于uvm基类库,建立所述目标接口对应的约束激励;基于验证模型和所述约束激励,对所述待测模块进行验证,输出验证结果。通过上述方式,本发明通过对输入参数的分析,确定对应的验证需求和验证策略,从而确定需要用到的验证模型,通过目标接口连接对应的验证模型,生成对应的约束激励,对待测模块进行验证测试,并获得验证结果。通过基于uvm的总线转换桥验证方法,可以提高系统的可重用性和验证平台搭建的自动化程度,提高了验证的工作效率,解决了目前验证平台的工作效率低下的技术问题。

附图说明

35.图1为本发明实施例方案中涉及的基于uvm的总线转换桥验证设备的硬件结构示意图;

36.图2为本发明基于uvm的总线转换桥验证方法第一实施例的流程示意图;

37.图3是本实施例提出的一个标准化的agent模板;

38.图4为本发明基于uvm的总线转换桥验证方法第二实施例的流程示意图;

39.图5为本发明提供的一种可重用验证平台的结构示意图;

40.图6为本发明基于uvm的总线转换桥验证方法第三实施例的流程示意图;

41.图7为本发明基于uvm的总线转换桥验证平台的应用流程示意图;

42.图8为本发明基于uvm的总线转换桥验证装置第一实施例的功能模块示意图。

43.本发明目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

具体实施方式

44.应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。

45.本发明实施例涉及的基于uvm的总线转换桥验证方法主要应用于基于uvm的总线转换桥验证设备,该基于uvm的总线转换桥验证设备可以是pc、便携计算机、移动终端等具有显示和处理功能的设备。

46.参照图1,图1为本发明实施例方案中涉及的基于uvm的总线转换桥验证设备的硬件结构示意图。本发明实施例中,基于uvm的总线转换桥验证设备可以包括处理器1001(例如cpu),通信总线1002,用户接口1003,网络接口1004,存储器1005。其中,通信总线1002用于实现这些组件之间的连接通信;用户接口1003可以包括显示屏(display)、输入单元比如键盘(keyboard);网络接口1004可选的可以包括标准的有线接口、无线接口(如wi-fi接口);存储器1005可以是高速ram存储器,也可以是稳定的存储器(non-volatile memory),例如磁盘存储器,存储器1005可选的还可以是独立于前述处理器1001的存储装置。

47.本领域技术人员可以理解,图1中示出的硬件结构并不构成对基于uvm的总线转换桥验证设备的限定,可以包括比图示更多或更少的部件,或者组合某些部件,或者不同的部件布置。

48.继续参照图1,图1中作为一种计算机可读存储介质的存储器1005可以包括操作系统、网络通信模块以及基于uvm的总线转换桥验证程序。

49.在图1中,网络通信模块主要用于连接服务器,与服务器进行数据通信;而处理器

1001可以调用存储器1005中存储的基于uvm的总线转换桥验证程序,并执行本发明实施例提供的基于uvm的总线转换桥验证方法。

50.本发明实施例提供了一种基于uvm的总线转换桥验证方法。

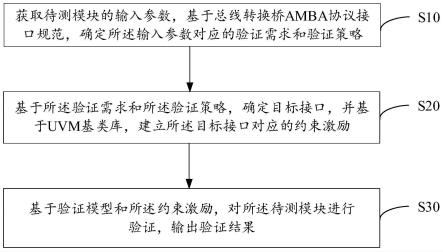

51.参照图2,图2为本发明基于uvm的总线转换桥验证方法第一实施例的流程示意图。

52.本实施例中,所述基于uvm的总线转换桥验证方法包括以下步骤:

53.步骤s10,获取待测模块的输入参数,基于总线转换桥amba协议接口规范,确定所述输入参数对应的验证需求和验证策略;

54.本实施例中,通过研究amba系列总线转换桥降低占用总线带宽的机制,总线转换桥设计原理以及amba口协议接口规范,给出基于uvm验证的目标以及整体的验证需求和验证策略。

55.具体地,amba总线协议是一套由arm提供的互连规范,该规范标准化了各种ip之间的芯片通信机制。这些设计通常有一个或多个微处理器以及集成其他一些组件——内部存储器或外部存储器桥、dsp、dma、加速器和各种其他外围设备,如usb、uart、pcie、i2c等。amba协议的主要目的是用一种标准和高效的方法来重用这些跨多个设计的ip。

56.步骤s20,基于所述验证需求和所述验证策略,确定目标接口,并基于uvm基类库,建立所述目标接口对应的约束激励;

57.本实施例中,通过对总线桥两侧总线接口信号的时序调整,以符合相应总线标准的时序规范,使不同总线之间就能够更顺利地进行数据交换和相互通信。把整个验证平台的运行过程设计为不同的阶段,保证各个阶段在特定的时间做特定的事情,从而提高效率。通过sequence的设计,将激励信息的产生从其他部分中完全独立出来,增加数据流产生的灵活性。

58.本实施例中,为提高uvm平台的可重用性,开发基于分层结构的uvm验证平台,包括factory机制、callback机制和sequence机制。

59.其中,factoy机制是指通过将拓展类在工厂注册,可实现环境内部组件的创建与对象的重载。factory机制主要针对构成验证环境层次的uvm_component及其子类,以及构成环境配置属性和数据传输的uvm_object及其子类。

60.callback机制提高代码的可重用性,还用于构建异常的测试用例。如果把两个项目不同的地方使用callback函数来做,而把相同的地方写成一个完整的env,这样重用时,只要改变相关的callback函数env可完全的重用。

61.sequence机制是用于控制和产生一系列激励,并通过sequencer将激励发送给driver的机制。sequence是一个产生和发送数据的过程。

62.具体地,利用uvm的通用类库编写组件模拟amba系列总线验证平台上主机端和从机端的行为,动态配置验证平台的环境使之满足不同的验证需求,产生受约束的随机激励,预留接口以方便扩展验证平台的功能。通过uvm基类库中的sequence类来实现激励事务的产生,分别给相应的接口创建sequence item,在sequence类中添加约束随机化激励,比如写地址和控制信息,突发类型、突发长度、保护类型等等,这样更能够全方面的验证待测设计dut(design under test)的功能是否有缺陷,弥补验证人员考虑不到的特殊情况,较快的达到全方位的验证。

63.其中,sequence item是每一次driver与dut互动的最小粒度内容,只能对数据进

行封装,不存在自动执行的函数。sequence对象自身会产生目标数量的sequence item对象。借助于sv的随机化和sequence item对随机化的支持,使得产生的每个sequence item对象中的数据内容都不相同。产生的sequence item会经过sequencer再流向driver。driver得到了每一个sequence item,经过数据解析,再将数据按照与dut的物理接口协议写入到接口上,对dut形成有效激励。

64.如图3所示,图3是本实施例提出的一个标准化的agent模板。

65.本实施例中,该标准化的agent模板为cag(common agent)模板,涵盖agent全部组件,依靠work_mode配置的不同,自动调整内部组件的调用与连接。包括:

66.(1)cag_driver.sv与cag_driver_cfg.sv

67.master模式下产生时序激励的模块,在build_phase中获取外部验证环境传入的interface;在main_phase中实现从sequencer获取trasaction并驱动至interface的功能。预留callback功能接口、动态复位功能、idle状态随机功能、读写操作分task模板。

68.cag_driver_cfg.sv文件为driver对应的控制文件,可用以指定一些driver相关的配置值,例如:随机模式、随机权重、反压模式、读无效时读数据是否保持等。

69.注:cfg的值应当从上层cfg文件中递归获取,即driver_cfg应来自agent_cfg,而agent_cfg应来自env_cfg。

70.(2)cag_slave_driver.sv与cag_slave_driver.sv

71.slave模式下用于对输入激励产生应答响应的模块,内部功能与cag_driver.sv类似。

72.slave_driver中的main_task有两种触发方式:1.利用sequence机制产生trasaction,并在特定条件下对trasaction赋值并驱动至interface;2.在run_phase中启动一个常驻循环进程,每当满足特定条件时便直接驱动至interface。若采用方式2,则slave_sequence有两种启动方式:

①

默认在cag_interface_agent.sv的run_phase中,自动启动slave_sequence。

②

由用户在自己的sequence_lib/testcase/environent的合适位置手动启动。

73.(3)cag_monitor.sv、cag_monitor_cfg.sv与cag_monitor_cov.sv

74.纯粹的监控采样模块,在各个工作模式下都将启用,从interface上采样并封装为trasaction,然后从out_port送出。(out_port一般在environment中连接至rm或checker)

75.cag_monitor_cov.sv是该agent涉及的全部接口类功能覆盖率模型全集,用于辅助用户衡量激励完备性。

76.(4)cag_interface.sv

77.为该agent的全部输入输出接口,包含三个clocking块以及三个modport。分别对应master(含reg_master)、slave、monitor三种工作模式。注意:同一信号在三个clocking块中方向不尽相同,以apb接口的paddr为例,drv_cb中应为output、slv_cb中应为input、而mon_cb中所有信号都应为input。

78.(5)cag_xaction.sv

79.为该agent中特定的uvm_sequence_item。需要注意的是cag_xaction中的成员与cag_interface中的成员并无绝对的一一对应关系。

80.(6)cag_sequence_lib.sv与cag_sequencer

81.cag_sequence_lib.sv中应提供该agent的base_sequence基类,以及在各类模式下的sequence分支(例如master_seq/slave_seq等)。同时应提供task封装的快捷操作方便用户使用(例如apb-agent应提供apb_write与apb_read函数)

82.(7)cag_agent.sv与cag_agent_cfg.sv

83.cag_agent的顶层,其中按照功能开关声明、例化、连接了前述组件。用户使用该agent时只需实例化该agent即可。cfg为其对应的配置文件。

84.(8)cag_agent_dec.sv

85.该agent的declare文件,其中用以定义该agent涉及到的parameter、define、typedef、struct等。

86.(9)cag_reg_adapter.sv

87.仅在reg_master模式下启用,用于连接reg_model与agent,将reg_model中的uvm_reg_bus_op与agent中的trasaction进行相互转换。

88.(10)cag.f

89.文件列表,使用者需要将其加入自己的env.f。

90.步骤s30,基于验证模型和所述约束激励,对所述待测模块进行验证,输出验证结果。

91.本实施例中,sequence中添加的激励整体被调用在uvm sequencer中,uvm sequencer根据driver的需求,然后以事务通信的方式发送给uvm驱动器driver,driver将抽象激励事务转换成dut接口能够识别的信号级的激励,从而驱动dut,同时,并在dut各创建监视器monitor来收集覆盖率数据,并将其转换成抽象事务发回给用户。

92.本实施例提供一种基于uvm的总线转换桥验证方法,所述方法获取待测模块的输入参数,基于总线转换桥amba协议接口规范,确定所述输入参数对应的验证需求和验证策略;基于所述验证需求和所述验证策略,确定目标接口,并基于uvm基类库,建立所述目标接口对应的约束激励;基于验证模型和所述约束激励,对所述待测模块进行验证,输出验证结果。通过上述方式,本发明通过对输入参数的分析,确定对应的验证需求和验证策略,从而确定需要用到的验证模型,通过目标接口连接对应的验证模型,生成对应的约束激励,对待测模块进行验证测试,并获得验证结果。通过基于uvm的总线转换桥验证方法,可以提高系统的可重用性和验证平台搭建的自动化程度,提高了验证的工作效率,解决了目前验证平台的工作效率低下的技术问题。

93.参照图4,图4为本发明基于uvm的总线转换桥验证方法第二实施例的流程示意图。

94.基于上述图2所示实施例,本实施例中,所述步骤s20具体包括:

95.步骤s21,基于所述uvm基类库中的序列类,创建各目标接口对应的序列项;

96.步骤s22,基于所述序列项,生成所述约束激励。

97.本实施例中,在amba协议转换桥设计中一共有三个接口,其中ahb、axi接口是主机接口,因此需要对这两接口添加随机化的激励事务来仿真数据流的传输。激励事务的产生是通过uvm systemverilog基类库中的sequence类来实现的,分别给相应的接口创建sequence item,在sequence类中添加约束随机化激励,比如写地址和控制信息,突发类型、突发长度、保护类型等等都可以是随机化的,这样更能够全方面的验证dut的功能是否有缺陷,弥补验证人员考虑不到的特殊情况,较快的达到全方位的验证程度。

98.进一步地,基于上述图2所示实施例,本实施例中,所述步骤s30具体包括:

99.将所述约束激励输入至所述验证模型中,基于所述约束激励中的所述序列项,确定待验证功能以及各待验证功能的验证顺序;

100.基于所述序列项和所述验证顺序,依次对所述各待验证功能进行验证,输出所述验证结果,以完成所述待测模块的验证。

101.本实施例中,uvm把整个验证平台的运行过程分为不同的阶段,目的就是保证在特定的时间做特定的事情,从而提高效率。sequence的设计思想也完全遵循这种原理。它把数据流(激励信息)的产生从其他部分中完全独立出来,从而提到了其他部分的可重用性,增加了数据流产生的灵活性。数据流产生之后,就需要把它送到驱动器中进而给dut,所以就需要序列发生器提供一种接口,将上层激励配置场景转换成所需要的事务激励,并把它传送给驱动器,通过tlm port连接驱动器实现通信。

102.进一步地,基于上述图2所示实施例,本实施例中,所述步骤s20具体包括:

103.基于所述验证需求和所述验证策略,确定待验证功能;

104.基于所述待验证功能,确定待用验证模型;

105.基于所述待用验证模型,确定所述待用验证模型与所述待测模块之间的总线接口,作为所述目标接口。

106.本实施例中,uvm整个验证平台时基于抽象事务的激励仿真,所以要将信号归类,分方向,并指向对应的dut的信号接口。这些都是通过systemverilog语法来实现的,这样也体现了搭建uvm验证平台的高效性以及可重用性。信号的打包是通过systemverilog中interface关键字实现的。信号的绑定是通过bind关键字来实现的。

107.其中,interface分两类,其中一类是实际的将信号打包起来操作的数据结构,另一类是虚拟interface,主要实现systemverilog代码与verilog代码的连接,并让其相互通信,因为在systemverilog中激励是添加在task任务中的,要实现正确的连接。基于uvm的amba协议转换桥验证实现只需要将接口实例化,如果要指向不同的dut子模块,那么就实例化到不同的dut子模块中,这样操作非常方便,节省了大量的工作,也很好的体现了uvm验证平台搭建的可重用性。

108.参照图5,图5为本发明提供的一种可重用验证平台的结构示意图。

109.本实施例中,可重用验证平台可以包括uvm验证组件级重用、模块级重用、功能级重用、事务级重用。

110.其中,验证组件级包括完善的测试激励库,根据环境配置或者传输序列的既定约束进行实时生成;模块级重用的重点是脱离协议内容而放在基本功能的重用上,功能级的重用主要包括各种协议之间的转换或数据与协议的发送和接收,包括地址映射转换函数和驱动地址传输的任务函数,公用函数,任务函数库;事务级重用通过对通用协议内容会定义数据包类型,数据传送格式等基础内容,对于协议相似的设计通过继承和修改公用库内容重用父类的定义以及功能函数。

111.参照图6和图7,图6为本发明基于uvm的总线转换桥验证方法第三实施例的流程示意图;图7为本发明基于uvm的总线转换桥验证平台的应用流程示意图。

112.基于上述图2所示实施例,本实施例中,所述步骤s30具体还包括:

113.步骤s31,创建监测接口,基于所述监测接口,连接监视器和所述验证模型;

114.步骤s32,基于所述监视器,采样所述验证模型对所述待测模块的验证数据;

115.步骤s33,将所述验证数据发送至计分板中,获得所述计分板的所述验证数据和参考模型中的标准数据之间的对比结果,作为所述验证结果。

116.本实施例中,uvm方法支持自动化监测模块,自动化监测模块主要实现参考模型模块reference model和计分板scoreboard协同起来实现对照验证,进而确保验证的正确性。结合system verilog高级验证语言进一步优化验证平台,完善查错机制,实现对soc设计中amba系列总线及总线转换桥复用的验证,采用总线功能模型来产生验证人员想要获取的激励。

117.具体实施例中,根据验证需求,采用systemverilog编写约束随机化的测试案例来产生大量随机化的激励给ahb、axi、以及apb三个接口,并编写coveragegroup收集覆盖率数据,收集三个接口上功能点的覆盖率信息。最后覆盖不到的功能点,采取直接测试案例去覆盖边界性条件,以提高覆盖率。

118.具体实施例中,来自sequencer的激励事务一方面经由driver给dut输入驱动,另一方面也经由driver给参考模型。参考模型是整个uvm验证平台的关键和核心,因为它做的工作与dut一致,计分板scoreboard会根据它的输出和dut进行比较,如果参考模型有错误,那其输出也是不可信的,从而scoreboard也是不可信的。而scoreboard主要用来比较参考模型输出的数据与dut是否一致,并给出比较结果。

119.基于上述图6所示实施例,本实施例中,所述步骤s32具体包括:

120.基于所述监视器,收集所述验证模型中各约束激励的代码覆盖率和功能覆盖率;

121.基于所述代码覆盖率和所述功能覆盖率,确定目标覆盖率;

122.在所述目标覆盖率达到预设覆盖率时,将当前采样数据作为所述验证数据。

123.进一步地,所述基于所述代码覆盖率和所述功能覆盖率,确定目标覆盖率之后,还包括:

124.在所述目标覆盖率未达到所述预设覆盖率时,对所述约束激励进行修改,确定测试盲区;

125.基于所述测试盲区,创建迭代约束激励,并基于所述迭代约束激励,对所述待测模型进行验证,获得所述当前采样数据和所述目标覆盖率,直至所述目标覆盖率达到所述预设覆盖率,将所述当前采样数据作为所述验证数据。

126.本实施例中,覆盖率技术是衡量验证进展与验证工作完成度的重要指标,研究覆盖率驱动的验证技术,包括代码覆盖率和功能覆盖率两种。

127.其中,代码覆盖率包括行覆盖率、状态机覆盖率、分支覆盖率、条件覆盖率和路径覆盖率。仿真工具将自动从设计代码中提取代码覆盖率。

128.功能覆盖率分为两种:面向数据的覆盖率,对已进行的数据组合检查,通过编写覆盖组、覆盖点和交叉覆盖获得面向数据的覆盖率。面向控制的覆盖率,检查行为序列是否已经发生。

[0129]“覆盖率”是衡量设计验证完成程度的一个通用词。随着测试逐步覆盖各种合理的组合,仿真过程会慢慢勾画出设计的情况。覆盖率工具会在仿真工程中搜集信息,然后进行后续处理并得到覆盖率报告,通过这个覆盖率报告找出覆盖上的盲区,然后对现有的测试激励做进一步修改,或者创建新的测试来填补这些盲区。这个过程一直迭代,直到覆盖率达

到预设标准为止。

[0130]

此外,本发明实施例还提供一种基于uvm的总线转换桥验证装置。

[0131]

参照图8,图8为本发明基于uvm的总线转换桥验证装置第一实施例的功能模块示意图。

[0132]

本实施例中,所述基于uvm的总线转换桥验证装置包括:

[0133]

验证需求确定模块10,用于获取待测模块的输入参数,基于总线转换桥amba协议接口规范,确定所述输入参数对应的验证需求和验证策略;

[0134]

约束激励建立模块20,用于基于所述验证需求和所述验证策略,确定目标接口,并基于uvm基类库,建立所述目标接口对应的约束激励;

[0135]

验证结果输出模块30,用于基于验证模型和所述约束激励,对所述待测模块进行验证,输出验证结果。

[0136]

进一步地,所述约束激励建立模块20具体包括:

[0137]

序列项创建单元,用于基于所述uvm基类库中的序列类,创建各目标接口对应的序列项;

[0138]

约束激励生成单元,用于基于所述序列项,生成所述约束激励。

[0139]

进一步地,所述验证结果输出模块30具体包括:

[0140]

待验证功能确定第一单元,用于将所述约束激励输入至所述验证模型中,基于所述约束激励中的所述序列项,确定待验证功能以及各待验证功能的验证顺序;

[0141]

验证结果输出单元,用于基于所述序列项和所述验证顺序,依次对所述各待验证功能进行验证,输出所述验证结果,以完成所述待测模块的验证。

[0142]

进一步地,所述约束激励建立模块20具体还包括:

[0143]

待验证功能确定第二单元,用于基于所述验证需求和所述验证策略,确定待验证功能;

[0144]

待用验证模型确定单元,用于基于所述待验证功能,确定待用验证模型;

[0145]

目标接口确定单元,用于基于所述待用验证模型,确定所述待用验证模型与所述待测模块之间的总线接口,作为所述目标接口。

[0146]

进一步地,所述验证结果输出模块30具体还包括:

[0147]

监测接口创建单元,用于创建监测接口,基于所述监测接口,连接监视器和所述验证模型;

[0148]

验证数据采集单元,用于基于所述监视器,采样所述验证模型对所述待测模块的验证数据;

[0149]

验证结果获得单元,用于将所述验证数据发送至计分板中,获得所述计分板的所述验证数据和参考模型中的标准数据之间的对比结果,作为所述验证结果。

[0150]

进一步地,所述验证数据采集单元具体包括:

[0151]

覆盖率收集子单元,用于基于所述监视器,收集所述验证模型中各约束激励的代码覆盖率和功能覆盖率;

[0152]

目标覆盖率确定子单元,用于基于所述代码覆盖率和所述功能覆盖率,确定目标覆盖率;

[0153]

验证数据确定子单元,用于在所述目标覆盖率达到预设覆盖率时,将当前采样数

据作为所述验证数据。

[0154]

进一步地,所述验证结果输出模块30具体还包括覆盖率迭代单元,具体包括:

[0155]

测试盲区确定子单元,用于在所述目标覆盖率未达到所述预设覆盖率时,对所述约束激励进行修改,确定测试盲区;

[0156]

覆盖率迭代子单元,用于基于所述测试盲区,创建迭代约束激励,并基于所述迭代约束激励,对所述待测模型进行验证,获得所述当前采样数据和所述目标覆盖率,直至所述目标覆盖率达到所述预设覆盖率,将所述当前采样数据作为所述验证数据。

[0157]

其中,上述基于uvm的总线转换桥验证装置中各个模块与上述基于uvm的总线转换桥验证方法实施例中各步骤相对应,其功能和实现过程在此处不再一一赘述。

[0158]

此外,本发明实施例还提供一种计算机可读存储介质。

[0159]

本发明计算机可读存储介质上存储有基于uvm的总线转换桥验证程序,其中所述基于uvm的总线转换桥验证程序被处理器执行时,实现如上述的基于uvm的总线转换桥验证方法的步骤。

[0160]

其中,基于uvm的总线转换桥验证程序被执行时所实现的方法可参照本发明基于uvm的总线转换桥验证方法的各个实施例,此处不再赘述。

[0161]

需要说明的是,在本文中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者系统不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者系统所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者系统中还存在另外的相同要素。

[0162]

上述本发明实施例序号仅仅为了描述,不代表实施例的优劣。

[0163]

本技术可用于众多通用或专用的计算机系统环境或配置中。例如:个人计算机、服务器计算机、手持设备或便携式设备、平板型设备、多处理器系统、基于微处理器的系统、置顶盒、可编程的消费电子设备、网络pc、小型计算机、大型计算机、包括以上任何系统或设备的分布式计算环境等等。本技术可以在由计算机执行的计算机可执行指令的一般上下文中描述,例如程序模块。一般地,程序模块包括执行特定任务或实现特定抽象数据类型的例程、程序、对象、组件、数据结构等等。也可以在分布式计算环境中实践本技术,在这些分布式计算环境中,由通过通信网络而被连接的远程处理设备来执行任务。在分布式计算环境中,程序模块可以位于包括存储设备在内的本地和远程计算机存储介质中。

[0164]

通过以上的实施方式的描述,本领域的技术人员可以清楚地了解到上述实施例方法可借助软件加必需的通用硬件平台的方式来实现,当然也可以通过硬件,但很多情况下前者是更佳的实施方式。基于这样的理解,本发明的技术方案本质上或者说对现有技术做出贡献的部分可以以软件产品的形式体现出来,该计算机软件产品存储在如上所述的一个存储介质(如rom/ram、磁碟、光盘)中,包括若干指令用以使得一台终端设备(可以是手机,计算机,服务器,空调器,或者网络设备等)执行本发明各个实施例所述的方法。

[0165]

以上仅为本发明的优选实施例,并非因此限制本发明的专利范围,凡是利用本发明说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本发明的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1