一种通用高速大容量缓存电路的制作方法

1.本发明属于存储电路领域,进一步来说涉及缓存电路领域,具体来说,涉及一种通用高速大容量缓存电路。

背景技术:

2.原有的缓存技术通常使用flash、ram、内存卡等实现采集、处理系统中的数据实时缓存,但目前还存在有迫切需求却不能广泛应用的现象,主要原因是现有技术方案存在以下不足:

3.a)容量不足。如flash、ram虽然读写速度快,但容量不大,不能满足大量数据存储的要求,如果需扩大存储容量,势必会大大增加电路的规模和成本;

4.b)读写速度不足。如内存卡容量虽然可以做得比较大,但是读写速度不高,不能满足高速的要求;

5.c)开发周期长。容量大和速度快的器件ddr操控的难度相对较大,增加开发时长,也会消耗不少驱动资源,并不能在科研和工程实践中大量应用。

6.有鉴于此,特提出本发明。

技术实现要素:

7.本发明所要解决的技术问题是:针对现有存储器件存在的大容量与快读写速度不能兼容的问题,特提出本发明的缓存电路,以解决系统中高速、大容量数据缓存的技术难题。

8.本发明的发明构思是:采用即插即用的通用性解决方案,通过对外部读写接口进行设计将电路组件化,在嵌入式系统中利用该组件即可轻松实现大容量、高速数据的缓存。

9.对于读写速度问题:使用fpga/cpld对ddr存储芯片进行驱动控制,读写时钟速度和传输带宽直接由处理器与ddr硬件的速度决定,读写时钟速度可达百mhz以上,传输带宽可达百mbit/s以上,从而解决高速高密度场景下数据缓存的问题;

10.对于存储容量与成本问题:ddr存储芯片价格相对比较低,且单芯片的容量密度可达十gbit以上,同时,使用fpga/cpld实现对ddr内存芯片进行控制,增加存储芯片数量就能对容量进行扩展,增加io的数量,即可获得设定的容量;

11.对于接口问题:在电气接口上,使用并行接口,采用同步时钟控制,即可实现简单、方便、快捷的数据读写;在物理接口上,使用通用性的插拔式金手指接口,就能在电路板上方便安装、更换或扩展内存。

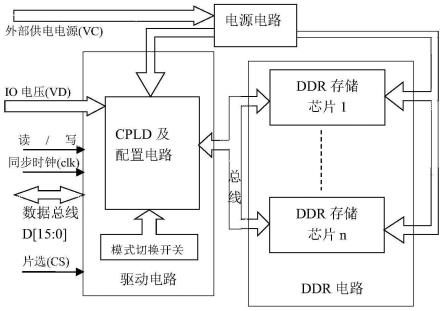

12.为此,本发明提供一种通用高速大容量缓存电路,原理框图如图1所示。包括电源电路、ddr电路和驱动电路。

13.电源电路给驱动电路、ddr电路供电。

14.ddr电路由若干个(至少1个)ddr存储芯片组成,用来存储数据。

15.驱动电路由模式切换开关、cpld及配置电路组成,用于驱动外部数据接口与ddr存

储芯片,完成数据的读写,模式切换开关用来调整外部接口数据总线位宽。

16.缓存电路利用cpld的高速特性,使用并行接口,将ddr存储芯片的驱动时序固化在缓存电路的cpld中,cpld将接收到的高速数据实时存入到ddr存储芯片中,从而用户不需要再对ddr存储芯片进行访问、操作,只需对缓存电路接口进行控制即可,可极大地节省了用户的设计资源,缩短开发周期,同时通过片选功能控制输出高阻态,允许共用总线的情况下挂载多块缓存电路,实现缓存扩展。

17.缓存电路接口进行通用性设计,采用金手指插拔式的通用接口,用户在进行系统设计时,预留匹配的电气端口,数据读写简单。电气端口定义见表1。

18.表1电气端口定义

[0019][0020]

表1中:vc为缓存电路供电端口;vd为数据、控制信号的电压调整端口,与外部数据、控制信号的电平匹配;w/r为存储和读取使能端口,1读,0写;cs为片选端口,0有效;clk为数据读写同步时钟端口,上升进行读写;d[15:0]为数据端口,当模式开关置0时,d[7:0]有效,模式开关置1时,d[15:0]有效;cmd_clk、cmd_in、cmd_out用于指定数据读写的起始位置,cmd_clk为同步时钟端口,上升进行读写,cmd_in为串行地址信息输入端口,cmd_out为串行地址信息输出端口。地址信息格式见表2。

[0021]

表2地址信息格式

[0022][0023]

本发明的特点:

[0024]

(1)具有容量大、速度快、接口简单等特性,并提供了通用化的接口,能适应多种处理器的直接控制。

[0025]

(2)能实现2gbit容量、700mbit/s传输宽带的缓存功能,且容量可以扩展,选用高性能的处理器和ddr存储芯片以及优化电路布线,传输带宽还能进一步提高。

[0026]

(3)以低成本实现了数据高速、大容量缓存,并且接口能匹配多种处理器,具备较

强的通用性。

[0027]

(4)采用即插即用式的简单通用接口,大大降低了缓存系统操控的复杂度,缩短应用系统的开发周期。

[0028]

本发明可以用于工业、农业等领域的科学研究和工程应用,能对高速度、高密度的数据进行临时缓存,在数据采集、处理系统中可以广泛应用。

附图说明

[0029]

图1为缓存电路原理示意图。

[0030]

图2为电源电路原理示意图。

[0031]

图3为ddr电路原理示意图。

[0032]

图4为驱动电路原理示意图。

[0033]

图5为金手指插拔式电路接口引脚示意图。

[0034]

图6为数据存储和读取流程示意图。

[0035]

图7为ad9231数据采集原理示意图。

[0036]

图8为ad9231数据采样局部波形示意图。

[0037]

图中:d1-d3为电源管理器,d4为ddr存储器,u为cpld,r为电阻,c为电容,g为无源晶振,p为接口插头。

具体实施方式

[0038]

如图1-8所示,所述一种通用高速大容量缓存电路,具体实施方式如下:

[0039]

电源电路选用0.8a输出驱动能力、0.02%负载调整率的电源管理器lp3964emp,具有较好的瞬态稳定性,d1产生的1.8v和d2产生的3.3v给cpld供电、d3产生的1.8v给ddr存储芯片和cpld的bank供电,电路原理图如图2所示。

[0040]

ddr电路选用ddr2的mt47h128m16(图3中的d4a-d4c)存储芯片作为存贮部件,ddr2在技术上与ddr1相比,做了改进,不需再增加终端匹配电阻,减少了大量外围器件,同时也降低了功耗,为减小设计规模,mt47h128m16的参考电压通过电阻分压获取,为保证高速电平跳变环境下线电压的稳定,内存芯片的每个电源脚就近接有退耦、贮能电容,另外为保证信号较好的完整性,布板时信号线都需做等长处理,ddr电路原理图如图3所示。

[0041]

驱动电路使用cpld xc2c128(u1a-u4e)为处理器,工作主频200mhz以上,并且拥有2个可独立供电的io bank,本电路将一个bank与ddr电路共电压,实现cpld与内存芯片的电平匹配,另一个bank的电压由外部接口引入,实现与外部电平的通用匹配,切换开关可调整高低电平,用来调整总线的有效宽度(8位、16位),可以合理调整外部驱动io的占用数量;p1接口用于程序下载;p2为模式开关,有0、1两个状态,用来调整总线的有效宽度;g1为有源晶振,可根据实际情况调整频率,本设计取100mhz。驱动电路原理框如图4所示。

[0042]

缓存电路使用金手指插拔接口,匹配通用mini pcie-52插座,引脚定义及参数见表3,接口引脚示意图见图5。

[0043]

表3接口定义及参数

[0044][0045]

缓存电路进行数据存储和读取时,数据存储和读取流程图如图6所示,运作流程如下:

[0046]

(1)vc输入5v,vd输入与外部处理器io电平一致的电压,范围为1.5v-3.3v;

[0047]

(2)通过xc2c128内部软件完成mt47h128m16存储芯片的初始化;

[0048]

(3)cs输入0使能激活缓存电路;

[0049]

(4)通过指令定义起始地址,地址指令总数据位宽32位,0-13为行地址,14-23为列地址,24-26为块地址,27-31预留为空,写入和读出的地址信息格式一致,通过cmd_clk上升沿进行地址指令的读写,cmd_in输入的是进行数据存储和读取时地址的初始位置,cmd_out输出的是数据存储和读取时地址的实时位置。w/r读写值改变后,需根据实际情况更新地址,如不更新,地址的初始值为最后更新的值,若从未更新,则默认为0;

[0050]

(5)w/r输入1时,进行写操作,通过clk上升沿写入待储存的数据,如模式开关为1,缓存电路取d[15:0]堆栈式存入存储芯片,如模式开关为0,缓存电路取d[7:0],累积满16位后堆栈式存入存储芯片;

[0051]

(6)w/r输入0时,进行读操作,通过clk上升沿读取已储存的数据,如模式开关为1,数据通过d[15:0]输出,如模式开关为0,数据通过d[7:0]输出。

[0052]

应用案例1:

[0053]

如图7所示,采用ad9231 40msps进行采样缓存,ad9231为12位模数转换器,fpga以40msps的采样率进行采样时,1秒钟会产生12bit

×

40m=480mbit的数据,以40mhz的同步时钟、16bit的位宽实时写入缓存电路,传输带宽折算为16bit

×

40m=640mbit/s,给ad9231输入标准正弦波,采样时间3秒,存入缓存电路的数据总量为1920mbit(1.875gb),数据缓存完成后,fpga将所有的数据读出并发送至测试计算机进行保存分析,无错存、漏存现象,波形与输入一致,图8为采集数据局部波形图。

[0054]

应用案例2:

[0055]

如图7所示,使用fpga产生16位无符号累加递增数据,增量为1,累加更新速率为45mhz,累加结果实时存入缓存电路,总时间2.5秒,传输带宽为45m

×

16bit=720mbit/s,存入总数据量为2.5

×

45m

×

16=1800mbit(1.75gbit),数据读回测试计算机进行处理分析,

无错存、漏存现象。

[0056]

最后应说明的是:上述实施例仅仅是为清楚地说明所作的举例,本发明包括但不限于以上实施例,这里无需也无法对所有的实施方式予以穷举。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。凡符合本发明要求的实施方案均属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1