一种基于6位近似全加器的2组有符号张量计算电路结构

1.本发明涉及神经网络硬件加速领域,尤其是2组有符号张量合并结构。

背景技术:

2.尽管大数据应用的高速增长为神经网路的发展提供动力,但它也给传统计算机系统带来了数据处理速度和可扩展性方面的严峻挑战。多层神经网络可以增加识别的准确度,但是也带来了大量计算单元和计算功耗。加法和乘法是应用中最广泛采用的计算运算。乘法器和加法器在任何数字电路或系统的功能中都发挥着重要作用,处理器的整体性能很大程度上取决于乘法器和加法器的面积和能耗。近似计算目前已经成为一种降低神经网络硬件功耗的普遍方案。

3.此外,神经网络在训练过程中有很大的容错率,神经网络加速器可以牺牲掉部分数据的精确度,换取电路结构上延迟,面积和功耗的优化。本发明利用所设计的6位近似全加器模块对2组有符号张量计算过程进行了优化,虽然损失了一定的数据精度,但是可以换取面积和功耗上的改进。

技术实现要素:

4.技术问题:本发明是为了解决在神经网络加速器中降低张量计算的面积和功耗问题,并且提供一种基于6位近似全加器的2组有符号张量计算电路结构。本发明是将所设计的6位近似全加器模块,应用到有符号8*8近似乘法器计算过程和2组有符号张量计算过程中,从而优化计算单元,进而降低电路的功耗和面积等硬件性能。

5.技术方案:本发明一种基于6位近似全加器的2组有符号张量计算电路结构包括:

6.6位近似全加器模块:具有六个数据输入位s1,s2,s3,s4,s5,s6;两个进位输入位cin1和cin2;两个进位输出位cout1和cout2;一个本级和位s;

7.有符号8*8近似乘法器电路:其利用所述的6位近似全加器模块优化计算过程,具有两个8位二进制数据输入位为x和y,所述的数据输入位x的范围是-127到127;所述的数据输入位y的范围是-127到127;所述的有符号8*8近似乘法器具有16位二进制输出结果s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13,s14,s15,s16;

8.2组有符号张量计算电路:其利用所述的6位近似全加器模块优化计算过程,输入数据是两组包含16个十进制数据的向量,每组向量的每个数据的范围在-127至127;所述2组有符号张量计算电路的输出结果是一组20位二进制数据输出位m1,m2,m3,m4,m5,m6,m7,m8,m9,m10,m11,m12,m13,m14,m15,m16,m17,m18,m19,m20。

9.所述的6位近似全加器模块的六个数据输入位s1,s2,s3,s4,s5,s6为111111输入,且两个进位输入位cin1和cin2为11输入时,所述的两个进位输出位cout1和cout2,以及所述的本级和位s的输出结果有两种输出结果,输出结果一为所述的两个进位输出位cout2和cout1,以及所述的本级和位s输出结果为111;输出结果二为所述的两个进位输出位cout2和cout1,以及所述的本级和位s输出结果为000。

10.所述有符号8*8近似乘法器电路中,所述的16位二进制输出结果的第1位是符号位,所述的符号位为1时,16位二进制输出结果为负数,所述的符号位为0时,16位二进制输出结果为正数;所述的输入数据x的符号位与输入数据y的符号位,共同确定有符号8*8近似乘法器的符号位s1;所述的16位二进制输出结果第2位至第16位是数据位,数据位是所述的近似乘法器的输出结果绝对值的二进制表示方式;有符号8*8近似乘法器的16位二进制输出结果的第11位由所述的6位近似全加器模块计算本级和位s11;有符号8*8近似乘法器的16位二进制输出结果的第10位由所述的6位近似全加器计算本级和位s10;有符号8*8近似乘法器的16位二进制输出结果的第9位由所述的6位近似全加器计算本级和位s9;由精确全加器计算本级和位s2至s8以及s12至s16位。

11.所述2组有符号张量计算电路需要的16组16位二进制数据由所述的有符号8*8近似乘法器电路结构计算16次所得,16组16位二进制数据用二进制补码逻辑表示标记为m1,m2,m3,m4,m5,m6,m7,m8,m9,m10,m11,m12,m13,m14,m15,m16。

12.所述2组有符号张量计算电路,计算所述的20位二进制数据输出位的第一级计算电路结构用于求解数据输出位的第一部分,具体过程为,m1,m2,m3,m4,m5,m6的第15位至第20位用所述的6位近似全加器模块计算所述数据输出位的第一部分s15_1,s16_1,s17_1,s18_1,s19_1,s20_1,第一部分的其余位s1_1至s14_1是由多个精确全加器计算m1,m2,m3,m4,m5的第1位至第14位所得。

13.所述2组有符号张量计算电路,计算所述的20位二进制数据输出位的第二级计算电路用于求解数据输出位的第二部分,具体过程为,m7,m8,m9,m10,m11,m12的第15位至第20位用所述的6位近似全加器模块计算所述数据输出位的第二部分s15_2,s16_2,s17_2,s18_2,s19_2,s20_2,第二部分的其余位s1_2至s14_2是由多个精确全加器计算m7,m8,m9,m10,m11的第1位至第14位所得。

14.所述2组有符号张量计算电路,计算所述的20位二进制数据输出位的第三级计算电路结构用于求解数据输出位的第三部分,具体过程为,m13,m14,m15,m16的第15位至第20位以及s15_1,s16_1,s17_1,s18_1,s19_1,s20_1和s15_2,s16_2,s17_2,s18_2,s19_2,s20_2,用所述的6位近似全加器模块计算所述20位二进制数据输出位的m15,m16,m17,m18,m19,m20,第三部分的其余位s1_3至s14_4是由多个精确全加器计算m13,m14,m15,m16的第1位至第14位所得。

15.所述2组有符号张量计算电路,计算所述的20位二进制数据输出位的第四级计算电路结构用于求解数据输出位的第四部分,具体过程为,第一级计算电路结构第一部分的s1_1至s14_1,第二级计算电路结构第二部分的s1_2至s14_2,第三级计算电路结构第三部分的s1_3至s14_3,s6的第1位至第14位以及s12的第1位至第14位,共同通过多个精确全加器计算所述的20位二进制数据输出位的m1,m2,m3,m4,m5,m6,m7,m8,m9,m10,m11,m12,m13,m14。

16.有益效果:本发明所提出的2组有符号张量合并方法相对于16组精确张量计算单元而言,由于所设计的6位近似全加器模块在结构上比6位精确全加器在结构上少了一个输入进位和一个输出进位,所以与精确张量计算过程对比,本发明所提出的2组有符号张量合并方法所对应的计算电路结构降低了所占用的面积资源;在整体电路性能上,所设计的有符号张量计算电路结构可以忽略额外进位所产生的功耗,从而进一步降低了张量计算的功

耗。

附图说明

17.图1为基于6位近似全加器的有符号8*8近似乘法器的电路结构图,

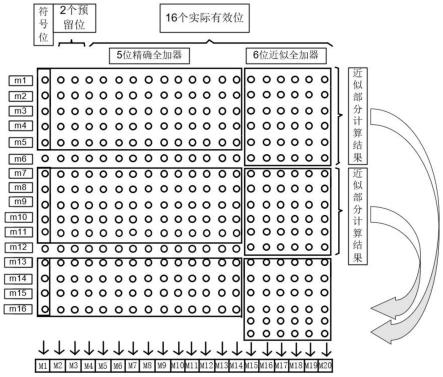

18.图2为2组有符号张量计算电路结构的整体流程图,

19.图3为2组有符号张量计算电路结构的第一级计算电路结构图,

20.图4为2组有符号张量计算电路结构的第二级计算电路结构图,

21.图5为2组有符号张量计算电路结构的第三级计算电路结构图,

22.图6为2组有符号张量计算电路结构的第四级计算电路结构图,

23.图7为有符号8*8近似乘法器错位累加计算图,

24.图8为本发明所提出的张量计算过程中16组11111100000101011111的累加计算图。

具体实施方式

25.下面结合具体实施例,进一步阐明本发明,应理解这些实施例仅用于说明本发明而不用于限制本发明的范围,在阅读了本发明之后,本领域技术人员对本发明的各种等价形式的修改均落于本技术所附权利要求所限定的范围。

26.本发明包含6位近似全加器模块,有符号8*8近似乘法器电路,2组有符号张量计算电路。

27.所述的6位近似全加器模块,其设计思想是以6位精确全加器为基础,省略6位精确全加器的一个输出进位和输入进位,从而近似成6位近似全加器,这种近似思想只在级联过程中有效。得到6位近似全加器的具体方法为,当6位精确全加器作为第一级(无输入进位)时,6位精确全加器的输入最大值条件为:6个输入数据位均为1,无进位输入,此时在6位精确全加器的输出端的结果是输出进位cout1_1为1,输出进位cout1_2为1,本级和位s1为0;当6位精确全加器作为第二级(接收第一级的输出进位cout1_1)时,6位精确全加器的输入最大值条件:6个输入数据位均为1,有一个进位输入值为1(即cout1_1的值),此时在6位精确全加器的输出端的结果是输出进位cout2_1为1,输出进位cout2_2为1,本级和位s2为1;当6位精确全加器作为第三级(接收第一级的输出进位cout1_2,接收第二级的输出进位cout2_1)时,6位精确全加器的输入最大值条件:6个输入数据位均为1,两个进位输入值均为1(即cout1_2和cout2_1的值),此时在6位精确全加器的输出端是输出进位cout3_1为1,输出进位cout3_2为0,输出进位cout3_3为0,本级和位s3为0,此时,将所述的第三级6位精确全加器的输出结果进行近似(省略掉一个输出进位),这种近似思想存在两种输出结果,输出结果一是将第三级6位精确全加器的输出数据近似成输出进位cout3_1为1,输出进位cout3_2为1以及本级和位s3为1,输出结果二是将第三级6位精确全加器的输出数据近似成输出进位cout3_1为0,输出进位cout3_2为0以及本级和位s3为0。从6位精确全加器级联的输出进位和输入进位中,可以观察到,本发明所设计的6位近似全加器模块只需要两个输入进位和两个输出进位即可满足级联要求。

28.所述的6位近似全加器模块的结构表现为,具有两个进位输入位cin1和cin2,六个数据输入位s1,s2,s3,s4,s5,s6,两个进位输出位cout1和cout2,一个本级和位s;所述的6

位近似全加器模块的功能表现为,只有在六个数据输入位s1,s2,s3,s4,s5,s6且两个进位输入位cin1和cin2的数值均为1时,进位输出位cout1、cout2以及本级和位s的输出数值为111(所述的输出结果一)或000(所述的输出结果二);其他输入条件的情况下,进位输出位cout1、cout2以及本级和位s的输出均为精确计算的数值。

29.所述的有符号8*8近似乘法器电路,其输入数据是两组数据x和y的二进制形式的后7位数据相乘,即x2,x3,x4,x5,x6,x7,x8与y2,y3,y4,,y5,y6,y7,y8按位相乘,得到七组7个二进数计算单元,该七组二进制计算单元的错位累加结果是所述的近似乘法器输出结果,x1与y1分别是两个输入数据的符号位,有符号8*8近似乘法器输出结果是一组16位二进制数据s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13,s14,s15,s16,其中s1表示输出结果的正负性,由x1和y1共同决定,s2至s16表示输出结果的绝对值;计算s9至s11时,引入所述的6位近似全加器模块和多个半加器级联进行近似计算。

30.所述的有符号8*8近似乘法器的电路结构主要由第一精确全加器模块1,第二精确计算模块2以及近似计算模块等三部分构成。在计算s16,s15,s14,s13,s12,s8,s7,s6,s5,s4,s3,s2时,均采用多个5位精确全加器级联进行计算;在计算s11时,第一6位近似全加器301接收来自第一精确计算模块1所产生的进位cout13to11和进位cout12to11;在计算s10时,第二6位近似全加器302先计算七组累加数据中的六组数据,例如先计算x2*y8,x3*y7,x4*y6,x5*y5,x6*y4,x7*y3六组数据,第二6位近似全加器302接收来自精确计算模块1所产生的进位cout12to10和来自第一6位近似全加器301的进位cout12to10,产生的s10_1与x8*y2经过第一半加器401获得s10,以及进位cout10to9_2;在计算s9时,将cout10to9_2与第二6位近似全加器302所产生的进位cout10to9_1共同经过一个第二半加器402,得到输出进位cout9和cout8_1;将cout8_1与cout10to8共同进过一个第三半加器403,得到输出进位cout8_2和cout7;第三6位近似全加器303接收来自第二半加器402所产生的进位cout9和来自第一6位近似全加器301所产生的进位cout11to9,第三6位近似全加器303最终输出s9。

31.所述的2组有符号张量合并方法所对应的计算电路结构,其输入数据是两组张量a和b,其中a是一组包含16个数据的张量(可以表示为矩阵形式[a1 a2 a3 a4 a5 a6 a7 a8 a9 a10 a11 a12 a13 a14 a15 a16]),每个数据的范围在-127至127,b也是一组包含16个数据的张量(可以表示为矩阵形式[b1 b2 b3 b4 b5 b6 b7 b8 b9 b10 b11 b12 b13 b14 b15 b16]),每个数据的范围在-127至127;将a和b按位相乘,即a1*b1,a2*b2,a3*b3

……

一共16组乘法计算单元(标记这16组计算单元为m1,m2,m3,m4,m5,m6,m7,m8,m9,m10,m11,m12,m13,m14,m15,m16),每组乘法计算单元以20位二进制补码的形式参与到合并计算的电路结构中,采用20位二进制补码是为了解决多组数据累加所导致的符号位不易累加的问题。此外,20位的二进制输出结果的范围可以容纳16组16位二进制的累加结果。所述的2组有符号张量计算电路的输出结果是一组20位的二进制数据(可以表示为m1,m2,m3,m4,m5,m6,m7,m8,m9,m10,m11,m12,m13,m14,m15,m16,m17,m18,m19,m20),此输出结果是张量计算真实值的二进制补码形式,需要利用计算工具进一步计算真实值。

[0032]

所述的2组有符号张量合并方法所对应的计算电路结构,其计算过程可以划分为四级计算电路结构:第一级计算电路结构的计算结果可以分为近似部分和精确部分,其中近似部分是由m1(20)(即m1的第20位,以下表示方式相同),m2(20),m3(20),m4(20),m5(20),m6(20)共同经过一个第一6位近似全加器11,并且第一6位近似全加器11与m1(19),m2

(19),m3(19),m4(19),m5(19),m6(19)为输入的第二6位近似全加器12级联,以此类推,第二6位近似全加器12、第三6位近似全加器13、第四6为近似全加器14、第五6位近似全加器15、第六6为近似全加器16级联,共同计算出第一部分的m15_1至m20_1位;精确部分由第一5位精确全加器101、第二5位精确全加器102等14个5位精确全加器构成,共同级联计算出第一部分的m1_1至m14_1位。

[0033]

所述的2组有符号张量合并方法所对应的计算电路结构,其第二级计算电路结构的计算结果可以分为近似部分和精确部分,其中近似部分是由m7(20),m8(20),m9(20),m10(20),m11(20),m12(20)共同经过第一6位近似全加器21,并且第一6位近似全加器21与m6(19),m7(19),m8(19),m9(19),m10(19),m11(19)为输入的第二6位近似全加器22级联,以此类推,第二6为近似全加器22、第三6位近似全加器23、第四6为近似全加器24、第五6位近似全加器25、第六6为近似全加器26级联,共同计算出m15_2至m20_2位;精确部分由第一5位精确全加器201、第二5位精确全加器202等14个5位精确全加器构成,共同级联计算出m1_2至m14_2位。

[0034]

所述的2组有符号张量合并方法所对应的计算电路结构,其第三级计算电路结构的计算结果可以分为近似部分和精确部分,其中近似部分是由m13(20),m14(20),m15(20),m16(20),m20_1,m20_2共同经过第一6位近似全加器31,并且第一6位近似全加器31与m1(19),m2(19),m3(19),m4(19),m19_1,m19_2为输入的第二6位近似全加器32级联,以此类推,第二6为近似全加器32、第三6位近似全加器33、第四6为近似全加器34、第五6位近似全加器35、第六6为近似全加器36级联,共同计算出m15至m20位;精确部分由第一5位精确全加器301、第二5位精确全加器302等14个5位精确全加器构成,共同级联计算出m1_3至m14_3位。

[0035]

所述的2组有符号张量合并方法所对应的计算电路结构,其第四级计算电路结构的计算结果只有精确部分,其精确部分由以输入m14_1、m14_2、m14_3、m6(14)、m12(14)为输入的第一5精确全加器401等14个5位精确全加器构成,共同级联计算出m1至m14位。

[0036]

所得到的结果m1,m2,m3,m4,m5,m6,m7,m8,m9,m10,m11,m12,m13,m14,m15,m16,m17,m18,m19,m20是张量计算结果的二进制补码形式。

[0037]

实施例1:

[0038]

本发明实施例1中首先提供一种基于6位近似全加器的有符号8*8近似乘法器的计算方法。6位近似全加器的其功能逻辑主要的近似部分是当8个输入端(6个数据输入位+2个进位)为11111111时,输出端结果为111。当有符号8*8近似乘法器的输入数据x为127(二进制为01111111),y为-127(二进制为11111111)时,两个输入数据的后七位按位相乘,并进行错位累加,其累加形式如图7所示,其近似部分的级联电路结构如图1所示。计算结果分析如下:

[0039]

s16位是经过第一精确计算模块1而得,为1;

[0040]

s15位是经过第一精确计算模块1而来,为0;

[0041]

s14位是经过第一精确计算模块1而得,为0;

[0042]

s13位是经过第一精确计算模块1而得,为0;

[0043]

s12位是经过第一精确计算模块1而得,为0;

[0044]

s11位是经过第一6位近似全加器301而得(6个输入位均为1,2个进位也均为1),为

1;

[0045]

s10位是经过第二6位近似全加器302和第一半加器401而得,为0;

[0046]

s9位是经过第三6位近似全加器303而得,为1;

[0047]

s8位是经过第二精确计算模块2而得,为0;

[0048]

s7位是经过第二精确计算模块2而得,为1;

[0049]

s6位是经过第二精确计算模块2而得,为1;

[0050]

s5位是经过第二精确计算模块2而得,为1;

[0051]

s4位是经过第二精确计算模块2而得,为1;

[0052]

s3位、s2位是经过第二精确计算模块2而得,分别为1和0;

[0053]

s1位是通过x(1)和y(1)而得,为1(表示负数);

[0054]

从而可知,输出结果绝对值的二进制为011111010100001,再考虑符号位1表示负数,即-16033,通过计算器可知-127*127的精确结果为-16129,误差在允许范围内。

[0055]

实施例2:

[0056]

本发明实施例2中首先提供一种基于6位近似全加器的2组有符号张量计算电路的合并方法。为了计算方便,采用实施例1中的有符号8*8近似乘法器的输入数值和输出结果,设张量a为[-127-127-127-127-127-127-127-127-127-127-127-127-127-127-127-127]、张量b为[127127127127127127127127127127127127127127127127]。张量a与张量b按位相乘后,得到的m1至m16均为11111100000101011111,故张量计算的原始输入数据为16组11111100000101011111的累加,如图8所示。计算2组有符号张量计算电路的四级计算电路结构如图3、4、5、6所示。

[0057]

2组有符号张量计算电路的第一级计算电路的结果如下:

[0058]

m20_1是m1(20)、m2(20)、m3(20)、m4(20)、m5(20)、m6(20)经过第一6位近似全加器11而得,为0;

[0059]

m19_1是m1(19)、m2(19)、m3(19)、m4(19)、m5(19)、m6(19)经过第二6位近似全加器12而得,为1;

[0060]

m18_1是m1(18)、m2(18)、m3(18)、m4(18)、m5(18)、m6(18)经过第三6位近似全加器13而得,为1;

[0061]

m17_1是m1(17)、m2(17)、m3(17)、m4(17)、m5(17)、m6(17)经过第四6位近似全加器14而得,为1;

[0062]

m16_1是m1(16)、m2(16)、m3(16)、m4(16)、m5(16)、m6(16)经过第五6位近似全加器15而得,为1;

[0063]

m15_1是m1(15)、m2(15)、m3(15)、m4(15)、m5(15)、m6(15)经过第六6位近似全加器16而得,为0;

[0064]

m14_1是m1(14)、m2(14)、m3(14)、m4(14)、m5(14)经过第一5位精确全加器101而得,为1;

[0065]

m13_1是m1(13)、m2(13)、m3(13)、m4(13)、m5(13)经过第二5位精确全加器102而得,为1;

[0066]

m12_1是m1(12)、m2(12)、m3(12)、m4(12)、m5(12)经过第三5位精确全加器103而得,为0;

[0067]

m11_1是m1(11)、m2(11)、m3(11)、m4(11)、m5(11)经过第四5位精确全加器104而得,为1;

[0068]

m10_1是m1(10)、m2(10)、m3(10)、m4(10)、m5(10)经过第五5位精确全加器105而得,为1;

[0069]

m9_1是m1(9)、m2(9)、m3(9)、m4(9)、m5(9)经过第六5位精确全加器106而得,为0;

[0070]

m8_1是m1(8)、m2(8)、m3(8)、m4(8)、m5(8)经过第七5位精确全加器107而得,为0;

[0071]

m7_1是m1(7)、m2(7)、m3(7)、m4(7)、m5(7)经过第八5位精确全加器108而得,为0;

[0072]

m6_1是m1(6)、m2(6)、m3(6)、m4(6)、m5(6)经过第九5位精确全加器109而得,为1;

[0073]

m5_1是m1(5)、m2(5)、m3(5)、m4(5)、m5(5)经过第十5位精确全加器110而得,为1;

[0074]

m4_1是m1(4)、m2(4)、m3(4)、m4(4)、m5(4)经过第十一5位精确全加器111而得,为0;

[0075]

m3_1是m1(3)、m2(3)、m3(3)、m4(3)、m5(3)经过第十二5位精确全加器112而得,为1;

[0076]

m2_1是m1(2)、m2(2)、m3(2)、m4(2)、m5(2)经过第十三5位精确全加器113而得,为1;

[0077]

m1_1是m1(1)、m2(1)、m3(1)、m4(1)、m5(1)经过第十四5位精确全加器114而得,为1;

[0078]

由于输入数据和电路结构的相似性,2组有符号张量合并方法的第二级计算电路的计算结果与第一级的计算电路的计算结果相同。

[0079]

2组有符号张量计算电路结构的第三级计算电路的结果如下:

[0080]

m20是m20_1、m20_2、m13(20)、m14(20)、m15(20)、m16(20)经过第一6位近似全加器31而得,为0;

[0081]

m19是m19_1、m19_2、m13(19)、m14(19)、m15(19)、m16(19)经过第二6位近似全加器32而得,为0;

[0082]

m18是m18_1、m18_2、m13(18)、m14(18)、m15(18)、m16(18)经过第三6位近似全加器33而得,为1;

[0083]

m17是m17_1、m17_2、m13(17)、m14(17)、m15(17)、m16(17)经过第四6位近似全加器34而得,为1;

[0084]

m16是m16_1、m16_2、m13(16)、m14(16)、m15(16)、m16(16)经过第五6位近似全加器35而得,为1;

[0085]

m15是m15_1、m15_2、m13(15)、m14(15)、m15(15)、m16(15)经过第六6位近似全加器36而得,为0;

[0086]

m14_3是m13(14)、m14(14)、m15(14)、m16(14)经过第一5位精确全加器301而得,为0;

[0087]

m13_3是m13(13)、m14(13)、m15(13)、m16(13)经过第二5位精确全加器302而得,为1;

[0088]

m12_3是m13(12)、m14(12)、m15(12)、m16(12)经过第三5位精确全加器303而得,为1;

[0089]

m11_3是m13(11)、m14(11)、m15(11)、m16(11)经过第四5位精确全加器304而得,为

0;

[0090]

m10_3是m13(10)、m14(10)、m15(10)、m16(10)经过第五5位精确全加器305而得,为1;

[0091]

m9_3是m13(9)、m14(9)、m15(9)、m16(9)经过第六5位精确全加器306而得,为0;

[0092]

m8_3是m13(8)、m14(8)、m15(8)、m16(8)经过第七5位精确全加器307而得,为0;

[0093]

m7_3是m13(7)、m14(7)、m15(7)、m16(7)经过第八5位精确全加器308而得,为0;

[0094]

m6_3是m13(6)、m14(6)、m15(6)、m16(6)经过第九5位精确全加器309而得,为0;

[0095]

m5_3是m13(5)、m14(5)、m15(5)、m16(5)经过第十5位精确全加器310而得,为0;

[0096]

m4_3是m13(4)、m14(4)、m15(4)、m16(4)经过第十一5位精确全加器311而得,为1;

[0097]

m3_3是m13(3)、m14(3)、m15(3)、m16(3)经过第十二5位精确全加器312而得,为1;

[0098]

m2_3是m13(2)、m14(2)、m15(2)、m16(2)经过第十三5位精确全加器313而得,为1;

[0099]

m1_3是m13(1)、m14(1)、m15(1)、m16(1)经过第十四5位精确全加器314而得,为1;

[0100]

2组有符号张量计算电路结构的第四级计算电路的结果如下:

[0101]

m14是m6(14)、m12(14)、m14_1、m14_2、m14_3经过第一5位精确全加器401而得,为0;

[0102]

m13是m6(13)、m12(13)、m13_1、m13_2、m13_3经过第二5位精确全加器402而得,为1;

[0103]

m12是m6(12)、m12(12)、m12_1、m12_2、m12_3经过第三5位精确全加器403而得,为1;

[0104]

m11是m6(11)、m12(11)、m11_1、m11_2、m11_3经过第四5位精确全加器404而得,为0;

[0105]

m10是m6(10)、m12(10)、m10_1、m10_2、m10_3经过第五5位精确全加器405而得,为1;

[0106]

m9是m6(9)、m12(9)、m9_1、m9_2、m9_3经过第六5位精确全加器406而得,为0;

[0107]

m8是m6(8)、m12(8)、m8_1、m8_2、m8_3经过第七5位精确全加器407而得,为1;

[0108]

m7是m6(7)、m12(7)、m7_1、m7_2、m7_3经过第八5位精确全加器408而得,为0;

[0109]

m6是m6(6)、m12(6)、m6_1、m6_2、m6_3经过第九5位精确全加器409而得,为0;

[0110]

m5是m6(5)、m12(5)、m5_1、m5_2、m5_3经过第十5位精确全加器410而得,为0;

[0111]

m4是m6(4)、m12(4)、m4_1、m4_2、m4_3经过第十一5位精确全加器411而得,为0;

[0112]

m3是m6(3)、m12(3)、m3_1、m3_2、m3_3经过第十二5位精确全加器412而得,为0;

[0113]

m2是m6(2)、m12(2)、m2_1、m2_2、m2_3经过第十三5位精确全加器413而得,为1;

[0114]

m1是m6(1)、m12(1)、m1_1、m1_2、m1_3经过第十四5位精确全加器414而得,为1;

[0115]

综上所述,2组有符号张量计算电路结构的输出结果m1至m20为11000001010110011100,由于此时得到的是补码形式,经过计算器换算得到真实值的二进制为10111110101001100100,即-256612。张量a和张量b按位相乘再累加的精确值为-127*127*16,即-256064,所采用的合并方案的计算结果的误差在允许范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1