缓存及其操作方法、计算机装置与流程

1.本公开的实施例涉及一种缓存及其操作方法、包括该缓存的计算机装置。

背景技术:

2.随着计算机科学技术高速发展,人们不仅期望计算机系统能精准、快速的执行程序运算,更对计算机系统的安全性能提出了一定的要求。近些年c/c++语言已被广泛采用在现代系统编程中,但是目前主流的编译器以及运行时环境(runtime)对c/c++程序指针不会做静态或者动态的安全检查,使得使用c/c++编程的程序很容易受到攻击。

3.目前解决内存安全问题的方法一方面是通过修改硬件、编译器以及运行时环境(runtime)这三个手段进行保护,另一方面是对于某些类型的攻击,硬件架构上无法进行直接处理,这种情况下最好的解决方法是使用一些通用的安全手段,比如通过虚拟化分区进行内存保护。

4.内存漏洞攻击可利用攻击者构造的违规行为构成攻击的第一阶段,然后通过漏洞将程序导向攻击者事先准备好的恶意程序进行执行,以获得系统的控制权或者泄漏系统特权信息。根据非法指针访问的类型,内存细粒度安全违例主要分为两大类:空间安全违例(spatial safety violation)和时间安全违例(temporal safety violation)。

5.空间安全违例:当指针访问对象是该程序范围外的内容,内存空间安全就会受到侵犯。最常见的例子就是利用堆栈上的缓冲区溢出,使用攻击者设计好的值覆盖函数的返回地址,引导程序的执行流方向;或者直接利用溢出改写重要变量或重要信息。

6.时间安全违例:当对对象的引用在规定时间范围外使用,内存时间安全就会受到侵犯,通常是在实例化对象的内存被重新分配之后,未进行严格的内存初始化。例如,由于对指向无效(通常是未分配或释放的)内存的指针进行解引用而导致的时间安全违例。

7.为了缓解内存安全违例带来的威胁,已经有一些相应的防御技术被研究出来,较为典型的就是数据执行保护(dep)机制,其基本原理就是将数据所在内存页标识为不可执行,当程序溢出成功转入壳代码(shellcode)时,程序会尝试在数据页面上执行指令,此时cpu就会抛出异常,而不是去执行恶意指令。通过启用dep,可以有效阻止数据页(如默认的堆页、各种堆栈页以及内存池页)执行代码。

8.另一种有效的防御机制是stack canary机制,其原理为在函数执行时向栈底插入cookie(缓存)信息,当函数返回时会验证cookie信息是否合法,若不合法就会停止程序运行。

9.通过虚拟内存系统实现的aslr机制、dep(nx/xd)或者stack canary机制都使得攻击者不再能够随意的注入和执行任意的攻击代码,因此这些预防机制在一定程度上保护了程序的安全运行。

10.但是,面对更加复杂的攻击代码以及手段,这些保护机制就会面临着失效的结果。例如,在面向返回的编程(rop)攻击中,通过破坏代码指针(如返回地址)和将多个工具(gadget)的执行链接在一起来实现任意代码执行。这些原始二进制代码中的序列被组合起

来实现攻击者设想的恶意攻击代码。

技术实现要素:

11.本公开的至少一个实施例提供了一种缓存,该缓存包括:数据阵列、标签阵列和标记阵列。该数据阵列配置为用于存储多个缓存行;该标签阵列配置为用于存储多个标签;该标记阵列配置为用于存储多个标记行。多个缓存行、多个标签以及多个标记行彼此一一对应,每个标记行用于存储与对应的缓存行中存储的第一数量的标记存储单元项相关联的第二数量的内存标记,标记行中存储的内存标记与关联的标记存储单元项的内存地址具有映射关系。

12.本公开的至少一个实施例还提供了一种计算机装置,该计算机装置包括:至少一缓存、处理器核内存,该至少一缓存采用上述实施例的缓存;处理器与缓存耦接;该内存与处理器和缓存耦接且配置为在计算机装置的运行过程中提供内存空间,其中,内存地址位于内存空间中。

13.本公开的至少一个实施例还提供了一种上述实施例的缓存的操作方法,该操作方法包括:接收访存请求,其中,访存请求包括访存地址,访存地址包括第一内存标记;响应于使用访存地址查询缓存命中的情况下,从标记阵列获取对应于访存地址的第二内存标记;比较获取的第一内存标记和获取的第二内存标记以确定第一内存标记和第二内存标记是否匹配。

附图说明

14.为了更清楚地说明本公开实施例的技术方案,下面将对实施例的附图作简单地介绍,显而易见地,下面描述中的附图仅仅涉及本公开的一些实施例,而非对本公开的限制。

15.图1示出了计算机系统中内存空间包括安全内存空间和非安全内存空间的示意图;

16.图2示出本公开的实施例中所使用的指针的示意图;

17.图3示出使用本公开实施例的内存标记对内存空间的访问进行保护的流程图;

18.图4示出根据本公开至少一实施例的包括内存标记的内存地址的示例;

19.图5示出6条示例性的标记内存指令的二进制编码格式;

20.图6a示出根据本公开至少一实施例的处理器的框架示意图;

21.图6b示出根据本公开至少一实施例的标记产生单元的示意图;

22.图6c示出根据本公开至少一实施例的硬件乱数生成器的示意图;

23.图7示出根据本公开至少一实施例的计算机装置的示意图;

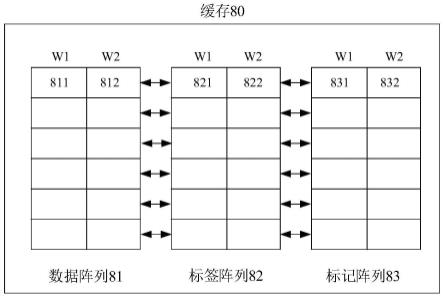

24.图8示出根据本公开至少一实施例的缓存的示意图;

25.图9示出根据本公开至少一实施例的一种示例性缓存的结构;

26.图10示出根据本公开至少一实施例的另一示例性的缓存的示意图。

27.图11示出根据本公开至少一实施例的涉及内存标记的访存指令的流程图;

28.图12为本公开至少一个实施例提供的一种电子装置的示意框图。

具体实施方式

29.为使本公开实施例的目的、技术方案和优点更加清楚,下面将结合本公开实施例的附图,对本公开实施例的技术方案进行清楚、完整地描述。显然,所描述的实施例是本公开的一部分实施例,而不是全部的实施例。基于所描述的本公开的实施例,本领域普通技术人员在无需创造性劳动的前提下所获得的所有其他实施例,都属于本公开保护的范围。

30.除非另作定义,此处使用的技术术语或者科学术语应当为本公开所属领域内具有一般技能的人士所理解的通常意义。本公开中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。同样,“包括”或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。“上”、“下”、“左”、“右”等仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则该相对位置关系也可能相应地改变。

31.为了应对计算机面临的内存安全问题,本公开的多个实施例提供了一种标记内存方案,该方案通过标记内存及其提供的细粒度内存保护,例如通过软硬件协同处理以保护对于计算机内存的访问,以较低的成本实现对计算机系统的保护,以缓解或避免内存安全违例带来的威胁。

32.图1示出了计算机装置中内存空间包括安全内存空间和非安全内存空间的示意图。本公开的至少一实施例提供的标记内存方案中,如图1所示,计算机系统的内存空间10包括安全内存空间100和非安全内存空间200,例如将计算机系统的内存空间10划分为安全内存空间100和非安全内存空间200。

33.在安全内存空间100中,将对应的内存空间按照预定大小划分为多份内存子空间101_n等,并且对每份内存子空间101进行标记,赋予内存标记(label),因此安全内存空间100在本公开中也简称“标记内存空间”或“标记内存”,即被赋予了内存标记的内存空间。

34.如图1所示,在安全内存空间100中,对于内存子空间101_1赋予标记la1,对于内存子空间101_2赋予标记la2,

……

。由此,内存子空间101_1、101_2等与对应的内存标记la1、la2等具有映射关系,也即,指向内存子空间101_1内的一个或多个内存地址与对应的内存标记la1具有该映射关系,指向内存子空间101_2内的一个或多个内存地址与对应的内存标记la2具有该映射关系,

……

。

35.内存标记la1、la2等的值例如基于随机数得到,每个内存标记的默认初始化值为0;例如,至少彼此相邻的内存子空间的标记的值彼此不同,或者在预定空间大小范围内(例如连续相邻的4个、8个、16个等内存子空间构成的地址段内)各个内存子空间的内存标记的值彼此不同,又或者,例如安全内存空间内的全部内存子空间的标记的值彼此都不同(虽然这需要内存标记本身可能的值的数量很大)。在非安全内存空间200中,则与常规的内存空间相同,不按份划分也不进行标记。

36.安全内存空间100的最小粒度(即一份内存子空间101_n的预定大小,又可以称为“标记粒度”(lg,label grain))可以根据需要选择,例如可以根据处理器的硬件规格决定,例如,内存空间的最小粒度可以设置一个字,也可以设置为2个字、4个字、8个字等,例如,该最小粒度可以根据处理器中所使用的缓存中缓存行(cache line或cache block)的大小来

设置,例如设置为等于缓存行的大小,或者设置为缓存行的大小的1/2,或者设置为缓存行的大小

×

路(way)所得到的大小(缓存中一个组(set)的大小);该最小粒度通常为一个字大小的2n倍(n为大于等于0的整数)。

37.在本公开的至少一个实施例中,标记内存和内存标记之间采用的是物理地址映射的方式。这种映射方式可以将标记元数据限制为可用内存的固定比例,例如物理地址0x8000000对应标记0x1,0x8000008对应标记0x2,

……

。虚拟地址通过处理器的存储管理单元(mmu)翻译过后得到物理地址,对内存标记的读写是基于物理地址。

38.该计算机系统的安全内存空间的标记粒度可以固定,或者也可以根据需要弹性设置;该标记粒度例如保存在系统中的预定位置或预定寄存器中,以供处理器在运行的过程中根据需要调用。内存标记本身所占据存储空间的大小(即标记大小(ls,label size)或标记宽度)则根据所需要的标记本身可能的值的数量来确定,例如可以设置为5个位(bit)(例如,这对应于31个非零标记值,其他类似的)、6个位、1字节(即8位)或2字节(即16位)。内存标记的大小在系统运行的过程中通常是固定的,或者在某些实施例中,内存标记的大小也可以根据需要设置;该标记大小例如保存在预定位置或预定寄存器中,以供处理器在需要的时候调用。

39.例如,在本公开的至少一个实施例中,设置了安全寄存器(sec寄存器),该安全寄存器设置为一种控制与状态寄存器(csr),用于runtime等控制硬件。该寄存器用于保存系统中标记匹配的安全开关(xs)以及标记粒度(lg)和标记内存粒度(ls)。例如,标记粒度最小为4bit,共设计2bit位宽,最后得到4+2

sec[lg]

大小的标记粒度;标记内存粒度最小为8字节。本公开的实施例中可以在硬件生成和/或后续程序runtime中对各种标记粒度、标记内存粒度、安全开关进行改写、设置。

[0040]

例如,sec寄存器中的xs字段具有2bit位宽,具体含义如下表1所示,该寄存器中的xs字段只能在m模式(machine mode,机器模式)、s模式(supervisor mode,监测模式)下访问。当系统中进程进行上下文切换时,需要检查sec寄存器的xs字段,以快速确定是否需要保存或恢复状态。

[0041]

表1

[0042]

状态含义0安全扩展并未启用1安全扩展已经启用但是所有状态皆为初始态2寄存器可能有非初始值,但这些值在之前被保存3寄存器存在未被保存的值

[0043]

如图1所示,对于安全内存空间100所分配的多个内存标记,可以例如在内存中再单独(即独立于安全内存空间100和非安全内存空间200)开辟另一个内存空间以作为存储标记的标记存储300;或者,可以独立于内存提供一个标记存储300,例如内存采用动态随机访问存储器(dram),而该标记存储300可以采用静态随机访问存储器(sram)。例如,该标记存储300具有多个标记项,每个标记项与安全内存空间200中的每个内存子空间对齐。需要指出的是,在上述第一种情形中,标记存储300中的这些标记项的物理地址不需要是连续的。

[0044]

在本公开的实施例中,例如,可以通过定制指令对安全内存空间中的每一份内存

空间进行标记,并且对需要保护的内存地址、指针等(在本公开的实施例中为了简便起见也统称“访存地址”)进行标记,即对内存地址、指针等也赋予标记,这种赋予访存地址的内存标记也可以称为“安全标记”。图2示出了本公开的实施例中所使用的指针的示意图。如图2所示,指针px包括对应的有效地址addrx,该指针px还包括被赋予的内存标记lax。

[0045]

在计算机系统中(例如处理器)通过识别内存地址、指针等对应的内存标记是否为0将内存地址、指针等区分为安全的(内存标记非0)与非安全的(内存标记为0),同时区分安全空间与非安全空间。例如,当设置某程序在安全内存空间中运行时(这样的程序可以被称为“安全程序”),则可以在启动该程序的进程时,由系统创建安全内存空间,并对程序中的访存指令等所使用的内存地址、指针等赋予目标地址对应的内存标记,之后在使用内存地址、指针等时,将内存地址、指针等被赋予的内存标记与对应于安全内存空间的目标地址获得的内存标记进行比较,由此判断内存地址、指针等是否被攻击者修改而违例访问本不应访问的地址,从而改善计算机系统的安全性。

[0046]

图3示出了使用本公开实施例的内存标记对内存空间的访问进行保护的流程图。如图3所示,该对内存空间的访问进行保护的流程包括:

[0047]

步骤310,获取被标记的访存地址要访问的目标内存地址;

[0048]

步骤320,使用该访存地址请求内存访问;

[0049]

步骤330,提取该访存地址本身的内存标记,并且获取被访问的目标内存地址的内存标记,比较两个内存标记以判断二者是否匹配;

[0050]

步骤340,如果二者匹配,则进行后续操作,访问目标内存地址并反馈访存成功;

[0051]

步骤350,如果二者不匹配,则中止处理,进行异常处理。

[0052]

该异常处理包括报警等,本公开的实施例对此不作限制。通过图3所示的进行标记匹配的流程来检测是否存在内存安全违规,由此提高了计算机系统的安全性。

[0053]

结合图3,再次参考图2所示,当使用该指针px访问对应的目标地址addrx时,该指针px本身的内存标记lax,假设目标地址位于内存子空间101_1中且该目标地址的内存标记为la1,则分别获取内存标记lax和内存标记la1,比较内存标记lax和内存标记la1,如果二者匹配,则可以进行后续操作,如果不匹配,则中止处理并返回异常。

[0054]

对于内存地址、指针等赋予的内存标记可以单独存储,也可以将内存标记与内存地址、指针等本身整合为一体,例如通过复用系统设定的内存地址中的富余位来保存每个内存地址、指针等对应的内存标记。例如,在64位处理器架构中,系统位宽为64位(bit),然而系统中的虚拟地址通常不会使用全部64位;例如,risc-v指令集中虚拟地址目前通常使用sv32、sv39和sv48三种分页模式,因此在64位的系统中,上述三种分页模式下,虚拟地址的低32位、低39位和低48位记载了全部有效地址(页表号+页内偏移)。因此,系统的虚拟地址中在高位存在无用位(例如,这些无用位通常为0),而低位则已经记载了全部有效地址信息。因此,可以利用64位架构中虚拟地址中高位余量来记载该地址对应的内存标记。

[0055]

图4示出了根据本公开至少一实施例的包括内存标记的内存地址的示例;如图4所示,一项地址包括高位部分以及低位部分,例如,对于64位地址而言,如果对应于sv48分页模式,可以选择高位部分为最高的16位(即[63:48]),而其余的低位部分则为最低的48位(即[47:0])。例如,高位部分的全部或部分用于记录内存标记,例如选择最高的16位中的8位作为内存标记位,例如选择[63:56]作为内存标记位用于记录对应的内存标记;低位部分

则用于记录有效地址,该有效地址部分共有48位,对应于理论上最多2

48

字节大小的内存空间。

[0056]

例如,访存地址或指针等在缺省状态下本身的内存标记为0,用于访问非安全空间;如果是用于访问安全空间的访存地址或指针,则在内存标记位设置相应的内存标记。处理器的微架构中通过识别一项访存地址或指针等的内存标记位是否全为0,从而将内存地址、指针等区分为用于安全内存空间的(标记非0)与用于非安全内存空间的(标记全为0),这两种类型不能混用,即不能使用用于安全内存空间的访存地址或指针访问非安全内存空间,反之也不允许。更进一步地,在至少一个示例中,虚拟地址的高位中记载的内存标记不但不能全为0,也不能各位都为1。

[0057]

如上所述,在本公开的实施例中,在系统中对于内存标记是通过一条或多条定制的标记内存指令进行操作,例如,这些标记内存指令包括用于生成标记、存储标记、读取标记、赋予标记、访存指令、修改标记等操作,例如,访存指令包括使用带有内存标记的内存地址、指针等访问内存,用于从内存中的目标地址读取数据或向目标地址存储数据。

[0058]

安全程序利用标记内存指令对安全访存地址、安全指针(指被标记的内存地址、指针等)以及安全内存空间进行保护,而安全访存地址、安全指针以及安全内存空间的创建、修改仅通过定制的标记内存指令进行,而不可通过常规的非标记内存指令创建、修改。

[0059]

本公开至少一个实施例中提供了至少如下所示的6条自定义拓展指令,图5示出该6条示例性的操作指令的二进制编码格式。例如,这些示例性的操作指令符合risc-v标准中的指令格式要求,共有32位,其中:

[0060]

·

[6:0]为opcode字段为指令的操作码;

[0061]

·

rd字段为目的寄存器;

[0062]

·

rs2字段为第二源寄存器;

[0063]

·

rs1字段为第一源寄存器;

[0064]

·

[14:12]为funct3字段表示3位的功能码;

[0065]

·

offset[11:0]或offset[11:5]表示计算地址所需要的立即数。

[0066]

在本公开的实施例中,这些标记内存指令并不限于采用如图5所示的指令格式,在不同于risc-v的其他指令集(isa)中,则可以采用相应的指令格式。

[0067]

这6条标记内存指令的具体功能如下所述,这里设地址的总长度(系统位宽)为xlen位,并且选择虚拟地址中的最高位[xlen-1:xlen-ls]用于记载内存标记。

[0068]

irl(插入随机标记,insert random label):将一个随机数生成器(例如硬件乱数生成器)生成的标记值写入目的寄存器的高位x[rd][xlen-1:xlen-ls](即内存标记位)中,而目的寄存器的低位x[rd][xlen-ls-1:0]置0,最终目的寄存器的值由流水线的执行单元写回。

[0069]

ldl(读取标记,load label):从内存地址x[rs1]+sign-extend(offset)读取八个字节,写入目的寄存器x[rd],此时地址高位x[rs1][xlen-1:xlen-ls]已经于内存地址计算单元进行剥离,在译码阶段存储于微操作码中,并且在写回阶段进行内存标记的匹配检查。

[0070]

sdl(存储标记,store label):将第二源寄存器x[rs2]中的标记(在内存地址计算单元进行剥离x[rs2][xlen-1:xlen-ls]得到)存入内存地址x[rs1]+sign-extend(offset)对应的标记项,即将一个硬件乱数生成器生成的标记值或者0值与内存地址绑定。

[0071]

sddl(在标记内存中存储数据,store data label):先检测内存地址x[rs1]+sign-extend(offset)取回的标记是否与该指令携带的标记(存储于微操作中,于x[rs1]地址计算后进入内存地址计算单元的时候进行剥离)匹配,若是标记匹配成功,将第二源寄存器x[rs2]的内容存入内存地址x[rs1]+sign-extend(offset)。

[0072]

mvl(移动标记,move label):将一个随机数生成器(例如硬件乱数生成器)生成的标记值与第一源寄存器的低位x[rs1][xlen-ls-1:0]的值进行拼接,拼接后的值发送给目的寄存器x[rd],最终目的寄存器的值由流水线的执行单元写回。

[0073]

addl(附加标记,add label):实现有关指针的继承以及转移功能,用于复制与转移指针高位的标记位,通过剥离第一源寄存器的高位x[rs1][xlen-1:xlen-ls]与第二源寄存器的低位x[rs2][xlen-ls-1:0]拼接,并将拼接结果复制到目的寄存器x[rd]之中。

[0074]

下面,例如以ldl指令以及sddl指令为例对图5所示的指令的格式进行说明。

[0075]

在所示出的示例中,ldl指令被编码成i型指令,其操作码(opcode)为000001,funct3为010(表示读取指令),用于将rs1寄存器(rs1)的值加上符号位扩展的12位立即数(offset[11:0])得到的(位于安全内存空间中的)有效地址对应的内存标记复制到目的寄存器(rd)。

[0076]

sddl指令被编码成s型指令,其操作码(opcode)为0100011,funct3为011(表示存储指令),用于将rs2寄存器(rs2)的值写入将rs1寄存器(rs1)的值加上符号位扩展的12位立即数(offset[11:5]+offset[4:0])得到的(位于安全内存空间中的)有效地址中。

[0077]

根据本公开至少一个实施例,上述6条自定义指令的一些示例性应用场景描述如下:

[0078]

(1)对于安全内存空间中的目标内存子区域,通过irl指令将例如随机数生成器生成的内存标记写入寄存器xd中,通过sdl指令把寄存器xd中的内存标记写入到与该目标内存子区域对齐的标记项中;

[0079]

(2)对于上述irl指令写入寄存器xd中的内存标记,通过addl指令将寄存器xd中的内存标记结合待标记的虚拟地址(例如访存地址或指针),将该内存标记写入该虚拟地址的高位之中;

[0080]

(3)对于待标记的虚拟地址,通过mvl指令将例如随机数生成器生成的内存标记与待标记的虚拟地址结合,由此给该待标记的虚拟地址分配了该内存标记。

[0081]

(4)当出现对于标记内存的读操作或写操作,例如执行ldl指令、sddl指令的操作时,如上所述,系统会将指令中的访存地址中本身携带的标记与访存地址(有效地址部分)对应的目标标记内存的内存标记进行匹配,如果匹配失败,则会触发异常,由此陷入异常处理机制并且例如中止程序的执行。

[0082]

(5)若标记内存被释放,例如进程执行结束,则将该标记内存的标记写入默认的0值进行复位,该复位操作通过sdl指令进行。

[0083]

(6)在本公开的至少一个实施例中,在系统实现时,在软件上修改堆分配器,使用sdl指令在分配初始化内存的时候进行标记,与此同时并为分配内存索引的返回指针设置相应的地址标记。

[0084]

例如对于如下示例:

[0085]

要保护的指针p1:0x80000000;目的寄存器1(rd1);目的寄存器2(rd2);目的寄存

器3(rd3);目的寄存器4(rd4),有如下指令:

[0086]

(1)irl rd1,表示产生一个内存标记(0x01,假定ls为8比特位宽,下同)且将其存储在目的寄存器rd1,其中,该目的寄存器rd1存储的数据中高位部分([xlen-1:xlen-ls])是产生的内存标记,而低位部分([xlen-ls-1:0])均为0,此时寄存器rd1中存储的内容为rd1=0x0100_0000_0000_0000;

[0087]

(2)mvl rd2 p1,表示产生一个内存标记(0x01)且将其写入指针p1的高位部分([xlen-1:xlen-ls]),而指针p1的低位部分([xlen-ls-1:0])保持不变,并且修改后的指针p1存储在目的寄存器rd2,此时寄存器rd2中存储的内容为rd2=0x0100_0000_8000_0000;

[0088]

(3)addl rd3 rd1 p1,表示将irl指令的目的寄存器rd1中存储的内存标记(即其中的高位部分([xlen-1:xlen-ls]))写入指针p1的高位部分([xlen-1:xlen-ls]),而指针p1的低位部分([xlen-ls-1:0])保持不变,并且修改后的指针p1存储在目的寄存器rd3,此时寄存器rd3中存储的内容为rd3=0x0100_0000_8000_0000;

[0089]

(4)sdl p1 0(rd1),表示将irl指令的目的寄存器rd1中存储的内存标记(即其中的高位部分([xlen-1:xlen-ls]))与指针p1指向的地址绑定;

[0090]

(5)ldl rd4 0(rd3),表示将addl指令的目的寄存器rd3中存储的内存标记(即其中的高位部分([xlen-1:xlen-ls]))读入到目的寄存器rd4中,此时寄存器rd4中存储的内容为rd4=0x0100_0000_0000_0000。

[0091]

例如,在至少一个实施例中,在所有安全内存空间分配的时候,当分配的空间不满足自定义的标记内存的标记粒度大小的时候,例如,按照自定义的标记内存的标记粒度大小进行扩充,分配的空间最后是自定义的标记内存粒度大小的整数倍。

[0092]

本公开的实施例中仅定义一部分的内存空间为安全内存空间,因此存在安全指针与非安全内存空间、非安全指针与安全内存空间的标记匹配等操作。需要说明的是,在至少一个实施例中,定制的标记内存指令使用内存标记为0的指针访问内存标记为0的安全内存空间时,也同样会触发匹配失败,由此触发硬件异常,这是因为定制的标记内存指令仅针对安全指针地址进行匹配。其余情况如下表2所示。

[0093]

表2

[0094][0095]

本公开的至少一个实施例提供了一种处理器或处理器核,处理器可以为包括单个处理器核的单核处理器或包括多个处理器核的多核处理器,以下为了简便起见,将处理器

或处理器核统称为“处理器”。本公开实施例的处理器可以用于执行上述标记内存以及对应的操作。图6a示出了上述实施例提供的处理器的框架示意图。

[0096]

如图6a所示,该处理器60包括前端模块61、译码及重命名单元62、发射单元63、寄存器堆64、执行模块65、重排序缓冲器(rob)66等。

[0097]

处理器执行应用程序时所使用的地址是虚拟地址。操作系统在给进程分配内存时,需要把使用到的虚拟地址映射到物理地址,物理地址是真正的物理内存访问地址。程序在实际访问内存之前需要先将虚拟地址转换为物理地址。将虚拟地址转换为物理地址的过程被称为地址翻译。处理器使用存储管理单元(mmu)进行地址翻译。并且,为了节省地址翻译的时间,为处理器核提供翻译后备缓冲器(tlb),用于存放一部分之前使用过的页表项(pte)。当需要进行地址翻译时,首先使用要翻译的虚拟地址查询tlb以看是否有需要的页表项,否则使用要翻译的虚拟地址查询页表来获得需要的页表项,通过页表项和页内地址偏移,就可以获得该要翻译的虚拟地址相对应的物理地址。之后可以使用该物理地址进行访问内存。

[0098]

例如,在对带内存标记的虚拟地址进行地址翻译时,首先剥离位于高位的内存标记,使用0填充高位得到修改后的虚拟地址,然后使用修改后的虚拟地址进行地址翻译,或者在不进行内存标记剥离的情况下,仅使用位于低位的有效位进行地址翻译,由此得到翻译后的物理地址,如果需要,再将内存标记与物理地址组合,得到待内存标记的物理地址。

[0099]

这里,前端模块61可以包括取指单元、分支预测单元等(图中未示出),可以与常规的处理器的前端模块相同,这里不赘述。

[0100]

译码及重命名单元62除了对常规的指令进行译码以及对指令中涉及的寄存器进行重命名操作之外,还包括标记内存指令表621,由此可以用于执行对于上述自定义标记内存指令的译码操作,以获得这些标记内存指令对应的微操作码以供后续由执行模块中的执行单元使用。

[0101]

执行模块65包括各种执行单元,例如,访存单元(load/store unit,lsu)651、标记产生单元652、算术逻辑单元(alu)、乘法单元(mvl)等,分别用于执行访存操作、标记产生操作、算术逻辑运算、乘法运算等。

[0102]

图6b示出根据本公开至少一实施例的标记产生单元的示意图。在本公开的实施例中,如图6b所示,标记产生单元652包括随机数产生子单元6521和标记合格检测子单元6522,用于执行上述irl、mvl等指令,以产生用于内存标记的标记值。

[0103]

随机数产生子单元6521例如为随机数生成器,该随机数生成器为硬件乱数生成器(hardware random number generator,hrng)。图6c示出根据本公开至少一实施例的硬件乱数生成器的示意图。如图6c所示,例如,在至少一个示例中,硬件乱数生成器包括:基于反相器链的振荡环(cor,chained oscillation ring)、触发器阵列、异或阵列以及输出单元;图6c中输出单元包括四个输出端口[0]~[3]。本公开的实施例对于随机数生成器的实现方式和具体结构没有限定。

[0104]

例如,硬件乱数生成器6521可以具有至少一个随机数生成源,例如两个随机数生成源,这两个随机数生成源分别是cor采用异或门来组合相邻振荡环的抖动信号以及触发器采样时候因为亚稳态的产生的不确定输出。cor电路由于受到工艺、温度、电压等影响,其输出随时间变化具有一定的浮动,处于一种不定态。而且,cor电路输出作为触发器阵列的

输入,该输入无法维持触发器正常工作所需要的建立时间以及保持时间,因此触发器最终工作在亚稳态,并且触发器的输出处于非人为控制的随机状态值。硬件乱数生成器的采样点至少包含一个振荡区域,因此输出数据得以保证其随机性。

[0105]

标记合格检测子单元6522对硬件乱数生成器6521生成的真随机值进行匹配验证,倘若取得的随机数值为0,则需要重新生成新的随机数,并且再对其进行匹配验证。倘若匹配验证通过,则标记产生单元652则可以发送有效(valid)信号,表示所获得的随机数可用于内存标记。前述匹配验证确保了不会产生为零(0)的内存标记,也即内存标记都是非0的,由此使得非带有内存标记的(非安全)内存地址与内存地址的有效部分与内存标记整合为一体时的(安全)内存地址相区别。更进一步地,在至少一个示例中,标记合格检测子单元6522除了如上所述检测标记是否为0之外,还检测所生成的标记是否各位都为1,如果是,则也设定为匹配验证不通过。

[0106]

在本公开至少一个实施例中,访存单元(lsu)651除了具有用于执行常规的针对非安全内存空间的访存指令,以从目标地址读取数据或将数据写入目标地址等之外,该访存单元651可以访问一级(l1)数据缓存67和二级(l2)缓存68等。访存指令用于在内存和寄存器之间传递数据,例如用于执行读取(load)和存储(store)操作,例如risc-v中常规的访存指令包括lw指令与sw指令、lb指令与sb指令等。

[0107]

在本公开的实施例中,该访存单元651还用于执行本公开实施例中上述自定义ldl指令、sdl指令、sddl指令等,分别用于获取目标地址的内存标记,或将内存标记写入与目标地址对应的标记项中等,用于将数据存入目标地址对应的标记内存中等。

[0108]

本公开至少一个实施例的处理器对于指令的执行方式可以是顺序执行,也可以是乱序执行。乱序执行过程中,处理器允许将多条指令不按取指顺序而将指令分开发送给各相应执行单元处理。重排序缓冲器(rob)提供来使得乱序执行的指令被顺序地提交。具体而言,一条指令在经过译码和重命名之后,就会被派遣到rob中、进入发射单元(发射队列)中,并且其状态被标记为“正在执行中”;在该指令被执行完毕后,rob会被通知并将该指令的状态标记为“执行完毕”;之后,当该指令在rob中位置被移位到rob的头部时,该指令会被提交(这里的“提交”指的是修改处理器状态,如修改逻辑寄存器堆),这条指令的结果在外部将可以被“观测”到。即,rob记录下各条指令在当前执行的程序中的顺序,并且一条指令在执行完毕之后不会立刻提交,而是先在rob中等待,等到其前面的所有指令都提交完毕,才可以提交结果到寄存器堆。例如,在处理器核(例如boom处理器核)的处理流水线中,重排序缓冲器(rob)的每个条目(entry)中,通过例如如下几个状态寄存器记录着该条目的状态,例如这些状态寄存器包括(但不限于):

[0109]

val(valid):该条目是否有效;

[0110]

bsy(busy):该条目的指令是否在执行中;

[0111]

exc(exception):该条目是否是一个异常;

[0112]

br_mask:该条目的指令属于哪个处于预测中的分支上。

[0113]

本公开的至少一个实施例提供了一种计算机装置,该计算机装置包括上述处理器以及与该处理器配合的多级缓存。图7示出了该实施例的计算机装置的示意图。如图7所示,计算机装置700包括至少一个处理器(或处理器核)710、一级缓存(l1缓存)、二级缓存(l2缓存)730、内存740和标记存储750。一级缓存(l1缓存)可以划分为例如彼此独立的一级指令

缓存(l1指令缓存)721和一级数据缓存(l1数据缓存)722;二级缓存730统一用于指令和数据,而不进行划分。例如,内存740采用dram而标记存储750采用sram。如下面具体描述的实施例,l1数据缓存和l2缓存还包括用于处理内存标记的部分(图中用l表示)。

[0114]

该处理器710包括存储管理单元(mmu)711和翻译后备缓冲器(tlb)712,以用于执行对于内存地址的地址翻译,以将虚拟地址翻译为对应的物理地址。

[0115]

本公开的实施例对于处理器(或处理器核)的架构不做限制,例如可以为用于risc-v指令集、arm指令集的微架构,例如对于用于risc-v指令集的微架构,可以为boom处理器核(例如sonicboom处理器核)等。在上述计算机装置中,一级缓存和二级缓存之间通过总线701连接;二级缓存和内存、标记存储之间也通过总线701连接。该总线701例如为tilelink总线。tilelink总线支持缓存一致性协议。

[0116]

在本公开的实施例中,例如上述ldl和sdl指令要分别从标记存储750读取内存标记以及在标记存储750中写入内存标记,同样地,为了加快对于内存标记的处理,需要在上述多级缓存中提供对于内存标记的缓存,例如将内存标记作为数据的一种加以处理。然而,如前所述,内存标记本身的大小(ls)可以选择为少于1个字节(例如5个位或6个位),则内存标记的大小与缓存行(或称为“缓存块”)的大小不能对齐,而且内存标记的存储地址(标记项的存储地址)与安全内存空间编址方式可能不同,因此需要修改对于l1缓存和l2缓存的常规访问逻辑,这将导致系统实现变得复杂。

[0117]

本公开的至少一个实施例提供了一种用于计算机装置的缓存,该缓存与处理器配合工作,可以用于一级缓存、二级缓存等。

[0118]

根据本公开的至少一实施例提供的缓存,该缓存包括数据阵列、标签阵列和标记阵列。该数据阵列配置为用于存储多个缓存行;该标签阵列配置为用于存储多个标签;该标记阵列配置为用于存储多个标记行。多个缓存行、多个标签以及多个标记行彼此一一对应,每个标记行用于存储与对应的缓存行中存储的第一数量的标记存储单元项相关联的第二数量的内存标记,标记行中存储的内存标记与关联的标记存储单元项的内存地址具有映射关系。通过该关联关系,内存标记可以对关联的标记存储单元项的访问提供验证、保护。例如,第一数量和第二数量可以相同或不同。

[0119]

在本公开的至少一实施例中,例如,数据阵列、标签阵列和标记阵列具有相同的逻辑组织结构。

[0120]

在本公开的至少一实施例中,上述缓存还包括至少一个地址译码器,该至少一个地址译码器配置为根据输入到缓存的访存地址中记载的索引对数据阵列、标签阵列和标记阵列进行检索,以确定数据阵列、标签阵列和标记阵列中的目标缓存行、目标标签和目标标记行。

[0121]

在本公开的至少一实施例中,该至少一个地址译码器包括第一地址译码器和第二地址译码器,第一地址译码器根据索引对数据阵列和标记阵列进行检索,以确定目标缓存行所在的目标缓存行组和目标标记行所在的目标标记行组,第一地址译码器根据索引对标签阵列进行检索以确定目标标签所在的目标标签组。

[0122]

在本公开的至少一实施例中,上述缓存还包括比较器、第一多路选择器和第二多路选择器。该比较器配置为根据输入到缓存的访存地址中记载的标签与目标标签组比较以确定是否命中,并且响应于该命中,提供访存地址中记载的标签在目标标签组中的路编号;

第一多路选择器配置为根据路编号,从目标缓存行组输出目标缓存行;第二多路选择器配置为根据路编号,从目标标记行组输出目标标记行。

[0123]

在本公开的至少一实施例中,上述缓存还包括第一校准器和第二校准器。第一校准器配置为根据输入到缓存的访存地址中记载的偏移从目标缓存行中选择目标数据项;第二校准器配置为根据输入到缓存的访存地址中记载的偏移从目标标记行中选择目标标记项。

[0124]

在本公开的至少一实施例中,上述缓存还包括匹配检测器,该匹配检测器配置为将输入到缓存的访存地址中记载的第一内存标记与目标标记项记载的第二内存标记进行比较,以确定第一内存标记和第二内存标记是否匹配。

[0125]

在本公开的至少一实施例中,上述缓存还包括数据缓冲器和标记缓冲器;该数据缓冲器配置为保存目标数据项;该标记缓冲器配置为保存目标标记项。

[0126]

在本公开的至少一实施例中,上述缓存还包括缺失状态处理寄存器,该缺失状态处理寄存器配置为当缓存处理的访问请求导致缓存缺失时,记录缓存缺失,且当缓存缺失被处理后,释放被记录的缓存缺失。

[0127]

在本公开的至少一实施例中,上述缓存还包括请求缓冲器,该请求缓冲器配置为临时存储缓存接收的访存请求,以等待缓存处理访存请求。

[0128]

在本公开的至少一实施例中,请求缓冲器还配置为用于对涉及数据的访存请求的处理,以及用于对涉及内存标记的访存请求的处理。

[0129]

在本公开的至少一实施例中,上述缓存还包括响应缓冲器,该响应缓冲器配置为临时存储缓存对于访存请求出现缓存缺失的情况下接收对对访存请求的响应,以等待缓存对于响应的处理。

[0130]

在本公开的至少一实施例中,该响应缓冲器还配置为用于对涉及数据的访存请求的处理,以及用于对涉及内存标记的访存请求的处理。

[0131]

在本公开的至少一实施例中,上述缓存还包括至少一个接口单元,该至少一个接口单元配置为用于缓存与处理器或其他缓存进行通信。

[0132]

在本公开的至少一实施例中,上述缓存还包括控制单元,该控制单元配置为:接收访存请求,其中,该访存请求包括访存地址,访存地址包括第一内存标记;响应于使用访存地址查询缓存命中的情况下,从标记阵列获取对应于访存地址的第二内存标记;比较获取的第一内存标记和获取的第二内存标记以确定第一内存标记和第二内存标记是否匹配。

[0133]

本公开的至少一个实施例还提供一种计算机装置,该计算机装置包括处理器、至少一缓存和内存。该至少一缓存采用上述任一实施例的缓存;该处理器与上述至少一缓存耦接;内存与处理器和缓存耦接且配置为在计算机装置的运行过程中提供内存空间,其中,所述缓存所涉及的内存地址位于内存空间中。

[0134]

在本公开的至少一实施例中,上述至少一缓存包括一级缓存和二级缓存。

[0135]

在本公开的至少一实施例中,一级缓存和二级缓存之间通过总线连接,该总线在计算机装置的运行过程中具有传送当前事务是否为内存标记相关事务的标志位。

[0136]

在本公开的至少一实施例中,该计算机装置还包括标记存储,该标记存储与处理器和内存耦接,且配置为用于存储多个内存标记,其中,标记存储中存储的多个内存标记分别与内存空间中分配的多个内存地址具有映射关系。

[0137]

在本公开的至少一实施例的计算机装置中,该处理器包括标记产生单元,该标记产生单元配置为计算机装置的运行过程中根据输入处理器的指令产生用于内存标记的随机值。

[0138]

本公开的至少一个实施例还提供一种上述缓存的操作方法,该操作方法包括:接收访存请求,其中,访存请求包括访存地址,访存地址包括第一内存标记;响应于使用访存地址查询缓存命中的情况下,从标记阵列获取对应于访存地址的第二内存标记;比较获取的第一内存标记和获取的第二内存标记以确定第一内存标记和第二内存标记是否匹配。

[0139]

图8示出了根据本公开一实施例的缓存的示意图。如图8所示,该缓存80包括数据阵列(data array)81、标签阵列(tag array)82和标记阵列(label array)83。

[0140]

在该实施例的一个示例中,这三个阵列具有相同的逻辑组织结构并且彼此对应,例如,对于数据阵列中的每一项,在标签阵列中存在对应的一项,在标记阵列中存在对应的一项。例如,数据阵列的逻辑组织结构可以是直接相联映射、分组相联映射或全相联映射方式,则对应地,标签阵列82和标记阵列83可以是直接相联映射、分组相联映射或全相联映射方式。

[0141]

在下面说明中以分组相联映射为例进行说明。本公开的实施例对于分组相联映射的结构不做具体限制,例如,每组(set)可以包括2路(way)、4路等。如图8示出了对于2路组的逻辑组织结构,数据阵列中每组具有两个缓存行(例如,缓存行811、812),分别对应于2路w1和w2;相应地,每个标签组具有两个标签(例如,标签821、822),分别对应于2路w1和w2以及分别对应于两个缓存行(例如,缓存行811、812);相应地,每个标记行具有两个内存标记行(例如,标记行831、832),分别对应于2路w1和w2以及分别对应于两个缓存行(例如,缓存行811、812)。

[0142]

例如,缓存行的大小可以为32字节或64字节,内存中的内存行(memory block)相应地也是32字节或64字节,并且安全内存空间中安全内存子空间与内存行对齐。根据标记内存的标记粒度(lg)的大小,标记阵列中每个标记行中内存标记的数量则可能不同;例如,当缓存行的大小为64字节,且安全内存空间的标记粒度也为64字节时,则每个缓存行存储了1个安全内存子空间对应的标记存储单元项(即具有标记粒度大小的内存空间),对应地每个标记行中仅包括1个内存标记;当缓存行的大小为64字节,而标记粒度为32字节时,则每个缓存行存储了2个安全内存子空间对应的标记存储单元项,对应地每个标记行中包括2个内存标记,分别对应于相应的缓存行中前32个字节的标记存储单元项和后32个字节对应的标记存储单元项。

[0143]

在该实施例的另一个示例中,数据阵列和标签阵列具有相同的逻辑组织结构,然而标记阵列与数据阵列不具有相同的逻辑组织结构但仍彼此对应,例如,对于数据阵列中的每一项,在标签阵列中存在对应的一项,在标记阵列中存在对应的一项。例如,数据阵列81的逻辑组织结构是分组相联映射,而标记阵列83的逻辑组织结构可以采用直接相联映射方式。标记阵列中每一标记行对应于数据阵列中的一组,且每一标记行仅包括1个内存标记,在这种情况下,标记粒度的大小等于缓存行的大小

×

路(way)所得到的大小,例如,当缓存行的大小为64字节且数据阵列81采用2路组的逻辑组织结构,则标记粒度为64*2,即128字节,即数据阵列中同一组中的两个缓存行都被映射为同一内存标记,此时每个缓存行存储了1/2个标记存储单元项。在该实施例中,标记阵列83的逻辑组织结构可以采用分组相联

映射方式,只是组中多个标记行彼此相同。

[0144]

如上所述,在本公开的不同的实施例中,缓存行中存储的标记存储单元项的数量(第一数量)与标记行存储的标记项(内存标记)的数量(第二数量)相同或不同。

[0145]

图9示出了根据至少一实施例的示例性缓存的结构,该缓存90包括数据阵列91、标签阵列92和标记阵列93,例如,如上所述这三者都具有分组相联映射的逻辑组织结构,或者数据阵列91和标签阵列92具有分组相联映射的逻辑组织结构而标记阵列93具有直接相邻映射。该缓存90还包括两个地址译码器941和942、两个多路选择器(mux)951和952、两个校准器(aligner)961和962、比较器98、匹配检测器(check)99。

[0146]

地址译码器941用于数据阵列91和标记阵列93,地址译码器942用于标签阵列92,这两个地址译码器对同一个输入(即下面描述的索引)进行译码。在其他示例中,这两个地址译码器也可以被合并为单个地址译码器,该单个地址译码器将译码输出同时提供给数据阵列、标签阵列和标记阵列。地址译码器941和942根据输入到缓存90的访存地址中记载的索引对数据阵列、标签阵列和标记阵列进行检索,以确定数据阵列、标签阵列和标记阵列中的目标缓存行、目标标签和目标标记行。更具体而言,地址译码器941根据索引对数据阵列和标记阵列进行检索,以确定目标缓存行所在的目标缓存行组和目标标记行所在的目标标记行组;地址译码器942根据索引对标签阵列进行检索以确定目标标签所在的目标标签组。

[0147]

比较器98用于将输入的访存地址中本身记载的标签(tag)与根据输入(即索引)从标签阵列检索得到的目标标签组中的多个标签分别比较,从而确定是否缓存命中(cache hit)或缓存缺失(cache miss),如果缓存命中,则提供访存地址中记载的标签在目标标签组中的路编号(例如图8所示的路w1或路w2)。

[0148]

多路选择器951用于数据阵列91,以根据输入的选择信号(即上述路编号)从数据阵列91的目标缓存行组输出目标缓存行;多路选择器952用于标记阵列93,以根据输入的选择信号(即上述路编号)从标记阵列93的目标标记行组输出目标标记行。

[0149]

校准器961用于数据阵列91,以在数据阵列91中选择的目标缓存行中再根据访存地址中记载的偏移进行选择,以获得目标数据项,选择结果被存入数据缓冲器(data buffer)971;校准器962用于标记阵列93,以在标记阵列93中选择的目标标记行中再根据偏移进行选择,以获得目标标记项,选择结果被存入标记缓冲器(label buffer)972。

[0150]

由于缓存行与标记行的组织方式一定相同,因此校准器961和校准器962对于偏移的使用方式不一定相同。例如,在一个示例中,缓存行的大小为64字节(在64位系统中包括8个字),安全内存空间的标记粒度也为64字节,每个缓存行存储了1个标记存储单元项,对应地每个标记行中仅包括1个内存标记,当指令集(isa)是基于字寻址时(例如目标数据项的大小为字),那么可以使用偏移在缓存行中再定位8个字之一以得到目标数据项,而此时标记行中仅有一个内存标记,因此实际无需使用偏移。又例如,在另一个示例中,缓存行的大小为64字节,而标记粒度为32字节,每个缓存行存储了2个标记存储单元项,对应地每个标记行中包括2个内存标记,那么可以使用偏移在缓存行中再定位8个字之一以得到目标数据项,在标记行中再定位2个内存标记之一以得到目标标记项。

[0151]

匹配检查器99用于将输入的访存地址中本身记载的内存标记(label)与根据输入(即索引)从标记阵列检索得到的目标标记项记载的内存标记(即保存在标记缓冲器中的内存标记)比较,从而确定二者是否匹配。

[0152]

该缓存90还包括控制模块(或控制逻辑,图中未示出),该控制模块配置为用于控制该缓存空间的操作,这些操作例如包括:接收访存请求,其中,该访存请求包括访存地址,访存地址包括第一内存标记;响应于使用访存地址查询缓存命中的情况下,从标记阵列获取对应于访存地址的第二内存标记;比较获取的第一内存标记和获取的第二内存标记以确定第一内存标记和第二内存标记是否匹配。

[0153]

进一步地,在本公开实施例的上述缓存,还需要能够区分带内存标记的指令和正常的指令(即不带内存标记的指令),由此实现与内存标记相应的操作,例如,标记匹配、匹配失败后异常报告等。需要指出的是,本公开实施例的缓存当然也能够执行正常的指令。

[0154]

本公开实施例的缓存还可以根据需要包括其他电路部分,这些电路部分例如包括有效位阵列、对于二级缓存的预取(prefetch)单元、目录组织等,例如,有效位阵列对应于标签阵列,用于记载对应的缓存行是否有效(valid)(例如:1代表有效;0代表无效)。只有在某个缓存行有效的情况下,比较标签才有意义;如果无效,可以直接判定缓存缺失。本公开的实施例对其他电路部分的组成、功能等不作限制,因此不再赘述。

[0155]

对于缓存的访问采用的是虚拟地址经地址翻译后得到的物理地址。对于操作标记内存的指令,在将带内存标记的虚拟地址翻译之后,将翻译得到的物理地址以及从虚拟地址高位剥离得到的内存标记一起(例如将二者结合得到带内存标记的物理地址)提供给缓存。因此,用于内存访问的被标记的访存地址进入缓存时会被分为标签(tag)、索引(index)、偏移(offset)以及标记(label)这四部分(前三者来自翻译得到的物理地址):

[0156]

·

偏移(offset)被用来识别访存地址对应的目标数据项以及目标标记项分别存储在缓存行或标记行中的哪一个字或字节(这取决于处理器所采用的指令集(isa)是基于字寻址的还是基于字节寻址的);

[0157]

·

索引(index)用来决定目标缓存行、目标标签和目标标记行存储在哪个组(set)中或是应当从哪个组(set)中查找;

[0158]

·

标签(tag)用来与标签阵列的目标标签组中储存的多个标签比较,决定访问请求是否缓存命中(hit)以及在命中的情况下是在当前组(set)中哪一路(way)命中;

[0159]

·

标记(label)用来在缓存命中的情况下,与从标记阵列中对应于数据阵列中被选择的访存地址的数据项的内存标记项记载的内存标记进行匹配、比较。

[0160]

参考图9所示,如上所述,当处理器执行一条访存指令的过程中,例如,在执行读取指令而需要访问缓存时,访存指令使用了被标记的访存地址以对安全内存空间进行访问,该被标记的访存地址在进行了地址翻译之后得到带标记的物理地址,该带标记的物理地址进入缓存时被拆分为标记(label)、标签(tag)、索引(index)、偏移(offset),标记被送入匹配检查器99,标签被输入比较器98,索引被送入地址译码器941和地址译码器942;偏移被送入校准器961和校准器962。

[0161]

如上所述,地址译码器411和地址译码器9422进行对索引进行译码,得到在数据阵列91、标签阵列92和标记阵列93中分别需要选择的组(set);数据阵列91和标记阵列93中各自被选中的组的内容被分别送入多路选择器951和多路选择器952,标签阵列92中被选中的组的内容被分别送入比较器98,比较器将访存地址本身的标签与标签阵列92中被选中的组中的多个标签分别进行比较之后,如果比较器98确定访存地址中本身的标签与标签阵列92中被选中的组中的某个标签相同(即缓存命中),则在命中的情况下将被命中的标签所在路

的路编号输出,且比较器98将该路编号送入多路选择器951和多路选择器952作为选择信号,如果不同(即缓存缺失),则返回缺失信号。

[0162]

在比较器确定命中的情况下,多路选择器951和多路选择器952根据比较器输出的选择信号(即路编号),选择数据阵列91和标记阵列93中各自被选中的组中相应路中的缓存行以及标记行输出,并分别对应输出至校准器961和校准器962。

[0163]

校准器961和校准器962根据该偏移在多路选择器1和多路选择器2输出的缓存行和标记行中分别选择目标数据项和目标标记项,并将它们分别存入数据缓冲器971和标记缓冲器972。

[0164]

匹配检查器99将接收的标记(label)与保存在标记缓冲器972中的标记进行比较,确定二者是否匹配,在匹配的情形,向处理器反馈匹配成功的信号,否则在不匹配的情形,反馈匹配失败的信号。处理器根据匹配成功的信号,读取在数据缓冲器971的数据项,否则根据匹配失败的信号,进入异常处理。

[0165]

本公开实施例的缓存兼容常规的非标记的访存地址的访存操作,非标记的访存地址不具有标记部分,因此相应地,缓存中的标记阵列93、多路选择器952、校准器962、标记缓冲器972、匹配检查器99不被激活,从而不参与缓存处理。并且,在上述缓存的使用过程中,使用最近访问的数据以填充缓存的数据阵列的多个项时所采用的替换策略可以包括最近使用(least recently used,lru)、最不常使用(least-frequently used,lfu)等,对应地,对于填充缓存的标记阵列的多个项时也采用相同的策略,本公开的实施例对具体采用的策略不作限制。

[0166]

并且,在执行存储(store)指令而需要写缓存时,例如可以采用多种写策略,包括直写(write through)、后写(post write)以及写回(write back)等方式。其中,在直写方式中,处理器向缓存写入数据时,同时向内存也写一份,使得缓存和内存的数据保持一致;在后写方式中,处理器更新缓存数据时,把更新的数据写入到一个更新缓冲器,在合适的时候才将更新的数据写入内存中,对内存进行更新;在写回方式中,处理器向缓存写入数据时,更新的数据仅被写入到缓存中,之后只有当修改过的缓存行被替换时才被写到内存中。

[0167]

并且,在向缓存写入对象数据时,在写入操作的过程中,如果存在缓存缺失的情况,这时也可以有两种处理方式。第一种方式为写分配(write allocate)方式,将写入地址的对象数据从内存读入缓存的某一缓存行中,然后再次执行(或唤醒)写入操作,则此时查询缓存必然为缓存命中,然后再在相应的缓存行中写入对象数据。第二种方法为非写分配(no-write allocate)方式,该方式并不将写入地址的对象数据读入缓存,而是直接将对象数据写入内存,因此这种方式执行后缓存并没有该对象数据的拷贝。

[0168]

如果缓存中只有数据阵列、标签阵列、标记阵列等,那么该缓存在遇到缓存缺失(或请求缺失)的情况下将不能接受新的缓存缺失(例如读取或存储缺失),这样的缓存被称为阻塞缓存。阻塞缓存在乱序处理器中会阻止访存单元(lsu)向其发出更多的存储或读取的访问请求,因此会影响整个处理器的运行速度。

[0169]

为此,可以在缓存中加入缺失状态处理寄存器(miss status holding register,mshr)。拥有mshr的缓存可以接受多个缓存缺失以待处理,因此被叫做非阻塞缓存。当出现一项访问请求导致缓存缺失时,mshr会在一项中记录该缓存缺失,缓存可以继续响应其它的访问请求,当之后缓存缺失被处理后,这个mshr的项会被释放。mshr通常是以填充缓冲器

(fill buffer)的方式实现。

[0170]

图10示出了根据本公开至少一实施例的另一示例性的缓存的示意图。如图10所示,该缓存50除具有如图9所示的缓存的结构(例如数据阵列、标记阵列、标签阵列(图中未示出))之外,还包括控制单元51、缺失状态处理寄存器(mshr)52、请求缓冲器(request buffer)53、响应缓冲器(response buffer)54、接口单元551和接口单元552。

[0171]

在至少一个示例中,如图10所示的缓存50可以用于一级缓存或二级缓存。在缓存50实现为一级缓存(即一级数据缓存)的情形,接口单元551用于与处理器通信,而接口单元552用于和二级缓存通信;在缓存50实现为二级缓存的情形,接口单元551用于与一级缓存通信,而接口单元552用于和下一级缓存(例如三级缓存(l3缓存))或内存以及标签存储(无l3缓存的情形)通信。如上所述,缓存之间例如通过tilelink总线通信连接。

[0172]

任何一条带有内存标记的访存指令在访问一级缓存的过程中出现缓存缺失之后,会通过总线向二级缓存进行访问请求,因此一级缓存和二级缓存之间进行通信的总线的至少部分端口也相应地被修改、封装,以匹配内存标记访存指令的操作。例如,在缓存之间(例如一级缓存和二级缓存之间)的总线提供标识当前数据是普通数据还是标记数据的is_lable标识位,例如该is_lable标识位为高(“1”)时,表示当前处理的对象为标记数据,否则表示当前处理的对象为通常的数据。

[0173]

控制单元51即为该缓存的控制模块,用于控制该缓存空间的操作,这些操作包括但不限于常规的处理访存请求、写回、填充、实现一致性协议等,还能区分带内存标记的指令和正常的指令(即不带内存标记的指令),实现与内存标记相应的操作。例如,在处理访存请求时,控制单元根据接收到的一项数据读请求/标记读请求,比较数据读请求/标记读请求与当前所缓存的各个缓存行或标记行对应的标签,以决定所请求的数据/标记是否在缓存中,如果所请求的数据/标记在缓存中,则返回相应的数据/标记,如果查询所请求的数据/标记未命中缓存(即缓存缺失),则将该数据读请求/标记读请求填入mshr中,并等待请求的数据/标记的返回。

[0174]

请求缓冲器53用于临时存储该缓存从前一级(例如处理器或一级缓存等)接收的访存请求,以等待该缓存的处理,由此可以避免在请求较多时导致的请求反压。响应缓冲器54用于临时存储例如该缓存对一项访存请求出现缓存缺失的情况下从后一级(例如二级缓存或三级缓存等)接收的对访存请求的响应,以等待缓存对于该响应的处理,由此可以避免在响应较多时导致的数据反压。

[0175]

例如,该请求缓冲器53和响应缓冲器54既可以用于对于通常的数据的请求处理,也可以用于涉及内存标记的请求处理。例如,该请求缓冲器53和响应缓冲器54可以将通常的请求和涉及内存标记的请求分开在不同的队列存储,或者在同一个队列存储。

[0176]

从后一级接收的对访存请求的响应后,该二级缓存通过例如响应缓冲器54中保存的访存请求的属性,判断返回的是通常的数据还是内存标记,然后将返回的数据或内存标记写入数据阵列或标记阵列中相应的位置。

[0177]

本公开至少一实施例提供了一种计算机装置,该计算机装置包括一级缓存、二级缓存等,例如,一级缓存实现为上述示例性的缓存,或者二级缓存实现为上述示例性的缓存,或者一级缓存和二级缓存都实现为上述示例性的缓存,由此实现对于内存空间的保护,提高系统的安全性。

[0178]

本公开的实施例还提供一种用于计算机装置的访存方法,该计算机装置包括内存,该访存方法包括:接收访存请求,其中,访存请求用于将对象数据存储到访存请求涉及的访存地址指向的内存中的目标地址,目标地址与第一内存标记具有映射关系,访存地址包括第二内存标记;使用访存地址获取第一内存标记;比较获取的第一内存标记和从访存地址获取的第二内存标记;响应于比较的结果指示第一内存标记和第二内存标记匹配,将对象数据存储到目标地址,否则触发异常。例如,该访存方法对应于执行上述sddl指令的过程。

[0179]

在本公开实施例的至少一实施例的访存方法中,访存地址由高位部分和低位部分组成,第二内存标记保存在高位部分,访存地址的有效地址保存在低位部分。

[0180]

在本公开实施例的至少一实施例中,上述访存方法还包括:在接收访存请求之后,从访存地址中提取第二内存标记。

[0181]

在本公开实施例的至少一实施例中,上述访存方法还包括:在接收访存请求之后,对访存地址进行地址翻译以得到访存物理地址;其中,使用访存物理地址获取第一内存标记。

[0182]

在本公开实施例的至少一实施例的访存方法中,计算机装置还包括标记存储,标记存储包括多个内存标记,多个内存标记与内存中的多个标记存储单元项的内存地址具有映射关系,多个内存标记包括第一内存标记;使用访存地址获取第一内存标记,包括:根据访存地址从标记存储获取第一内存标记。

[0183]

在本公开实施例的至少一实施例的访存方法中,计算机装置包括缓存,缓存配置为存储缓存数据和与缓存数据的内存地址对应的内存标记项;根据访存物理地址获取第一内存标记,包括:使用访存物理地址访问缓存,从缓存获取第一内存标记。

[0184]

在本公开实施例的至少一实施例的访存方法中,根据访存物理地址获取第一内存标记,还包括:在使用访存物理地址访问缓存且产生缓存缺失的情形,使用访存物理地址从内存读取对象数据并获取第一内存标记,将对象数据和第一内存标记填充到缓存中。

[0185]

在本公开实施例的至少一实施例的访存方法中,访存请求对应于第一指令,第一指令指示将对象数据存储到访存地址指向的内存中的目标地址;访存方法还包括:对第一指令进行译码以得到与第一指令对应的多个微操作。例如该第一指令对应于上述sddl指令。

[0186]

在本公开实施例的至少一实施例的访存方法中,上述多个微操作包括:用于从访存地址中获取第二内存标记的一个或多个第一微操作;使用访存地址获取第一内存标记的一个或多个第二微操作;比较获取的第一内存标记和从访存地址获取的第二内存标记的一个或多个第三微操作;响应于比较的结果指示第一内存标记和第二内存标记匹配,将对象数据存储到目标地址的一个或多个第四微操作;响应于比较的结果指示第一内存标记和第二内存标记不匹配,触发异常的一个或多个第五微操作。例如,上述一个或多个第二微操作等价于译码ldl指令得到的一个或多个微操作。

[0187]

在本公开实施例的至少一实施例的访存方法中,在对第一指令译码之后,将第一指令填入重排序缓冲器,将多个微操作发射到访存单元以用于执行多个微操作。

[0188]

在本公开实施例的至少一实施例中,访存方法还包括:响应于比较的结果指示第一内存标记和第二内存标记匹配,修改重排序缓冲器中对应于第一指令的状态,以允许重

排序缓冲器可以提交第一指令,其中,将对象数据存储到目标地址包括提交第一指令。

[0189]

在本公开实施例的至少一实施例中,访存方法还包括:使用执行状态寄存器以记录在执行第一指令的多个微操作中的一个或多个状态。

[0190]

本公开的至少一实施例提供了一种计算机装置,该计算机装置包括处理器和内存,其中,处理器包括访存单元(lsu)。该访存单元配置为:接收访存请求,其中,访存请求用于将对象数据存储到访存请求涉及的访存地址指向的内存中的目标地址,目标地址与第一内存标记具有映射关系,访存地址包括第二内存标记;使用访存地址获取第一内存标记;比较获取的第一内存标记和从访存地址获取的第二内存标记;响应于比较的结果指示第一内存标记和第二内存标记匹配,将对象数据存储到目标地址,否则触发异常。

[0191]

在本公开实施例的至少一实施例的计算机装置中,访存单元还配置为:在获取访存请求之后,从访存地址中提取第二内存标记。

[0192]

在本公开实施例的至少一实施例中,计算机装置还包括存储管理单元(mmu),该存储管理单元配置为对访存地址进行地址翻译以得到访存物理地址,其中,访存单元还配置为使用访存物理地址获取第一内存标记。

[0193]

在本公开实施例的至少一实施例中,计算机装置还包括标记存储,其中,标记存储包括多个内存标记,多个内存标记与内存中的多个标记存储单元项的内存地址具有映射关系,多个内存标记包括第一内存标记;访存单元还配置为使用访存地址从标记存储获取第一内存标记。

[0194]

在本公开实施例的至少一实施例中,计算机装置还包括缓存,该缓存配置为存储缓存数据和与缓存数据的内存地址对应的内存标记项,其中,访存单元还配置为:使用访存物理地址访问缓存,从缓存获取第一内存标记。

[0195]

在本公开实施例的至少一实施例的计算机装置中,处理器还包括译码单元和重排序缓冲器;译码单元配置为,对对应于访存请求的第一指令进行译码,以得到与第一指令对应的多个微操作;重排序缓冲器配置为,在第一指令被译码之后,在重排序缓冲器中填入第一指令,以等待第一指令被访存单元执行。

[0196]

在本公开实施例的至少一实施例的计算机装置中,访存单元还配置为:响应于比较的结果指示第一内存标记和第二内存标记匹配,修改重排序缓冲器中对应于第一指令的状态,以允许重排序缓冲器可以提交第一指令;重排序缓冲器还配置为:响应于状态被修改,提交第一指令。

[0197]

在本公开实施例的至少一实施例中,计算机装置还包括执行状态寄存器,该执行状态寄存器配置为记录在执行第一指令的多个微操作中的一个或多个状态。

[0198]

本公开实施例的至少一实施例提供了一种处理装置,包括处理单元和存储器;存储器上存储有一个或多个计算机程序模块;其中,一个或多个计算机程序模块被配置为由处理单元执行时实现如上任一实施例的访存方法。

[0199]

本公开实施例的至少一实施例提供了一种非瞬时可读存储介质,其中,非瞬时可读存储介质上存储有计算机指令,其中,计算机指令被处理器执行时实现如上任一实施例的访存方法。

[0200]

下面以上述ldl指令、sdl指令以及sddl指令以及一级缓存为例,对上述自定义指令在本公开实施例中包括上述结构的缓存的计算机装置中的执行流程进行说明。

[0201]

当处理器执行一条ldl指令时,需要读取该指令中指定的内存地址ad的内存标记la,首先进行地址翻译后得到内存地址ad对应的物理地址pad,使用该物理地址pad(即该内存地址中低位有效地址部分,而地址高位x[rs1][xlen-1:xlen-ls]已经于内存地址计算单元进行剥离,在译码阶段存储于微操作码中)访问一级缓存。如果缓存命中,即一级缓存的数据阵列中已经存储有该物理地址pad对应的数据da,相应地标记阵列也已经存储有该物理地址pad对应的标记la,因此可以获取该物理地址pad对应的标记la,并将内存标记la返回给处理器(写入目的寄存器)。如果缓存缺失,即一级缓存的数据阵列中尚未存储该物理地址pad对应的数据da,相应地标记阵列也没有存储该物理地址pad对应的标记la,则向下级缓存(即二级缓存)请求读取物理地址pad的内存标记la;当下级缓存返回物理地址pad的内存标记la,同时也返回物理地址pad对应的数据da,一级缓存将返回的物理地址pad的内存标记la以及数据da彼此对应地填充到标记阵列和数据阵列中,另外将内存标记la返回给处理器(写入目的寄存器)。

[0202]

当处理器执行一条sdl指令时,需要将该指令中指定用于内存地址ad的内存标记la存入与内存地址ad对应的标记项中,以直写方式为例,首先进行地址翻译后得到内存地址ad对应的物理地址pad,使用该物理地址pad(即该内存地址中低位有效地址部分,而地址高位x[rs1][xlen-1:xlen-ls]已经于内存地址计算单元进行剥离,在译码阶段存储于微操作码中)访问一级缓存和标记存储(参见图7),在标记存储中与物理地址pad对应的内存标记项中写入内存标记la。在访问一级缓存时,如果缓存命中,则将内存标记la写入标记阵列中,该内存标记la在标记阵列中的项与数据阵列中保存内存地址ad的数据da的项相对应。如果缓存缺失,即一级缓存的数据阵列中尚未存储该物理地址pad对应的数据da,则将物理地址pad及其当前内存标记(如果对于物理地址pad尚未分配内存标记,则缺省为0)读入该一级缓存中,在该一级缓存的数据阵列、标记阵列中创建对应于物理地址pad的项以分别保存对应的数据da和当前内存标记,之后再次唤醒sdl指令访问一级缓存,将内存标记la写入标记阵列中,该内存标记la在标记阵列中的项与数据阵列中保存内存地址ad的数据da的项相对应。

[0203]

对应于上述sddl指令,用于在非安全内存空间进行对应的写入操作的为存储(store)指令,例如sb或sw指令等。对于非安全内存空间的写入操作时,这些指令在源操作数准备好之后就可以执行、提交,将源操作数对应的数据写入内存中的目的地址。但是,本公开实施例的上述sddl指令在源操作数准备好之后并不会马上执行、提交,而是要先进行内存标记匹配以确定当前的写入操作是否为安全操作。因此,在本公开的至少一个实施例中,在对sddl指令进行译码以产生微操作时,除了常规的地址计算的微操作、获取内存地址中的标记的微操作、比较标记是否匹配的微操作、写存储器的微操作、触发异常的微操作等(即上述第一微操作~第五微操作的示例)之外,还分裂出等价于上述ldl指令的操作,该操作包括的一个或多个微操作等价于译码ldl指令得到的一个或多个微操作,即读取该sddl指令中指定的内存地址ad对应的内存标记la。然后,可以进一步将该内存标记la与该指令中指定的内存地址ad本身所携带的内存标记la’进行比较,判断二者是否匹配,如果匹配,则将该sddl指令的执行结果提交,否则触发异常。

[0204]

图11示出了根据本公开至少一实施例的涉及内存标记的访存指令(数据存储指令)的流程图。首先sddl指令被送入处理器中,在被译码、重命名之后进入重排序缓冲器

(rob)以及发射队列中等待执行,在rob中设置该sddl指令对应的条目的bsy状态为“正在执行中”以等待提交,之后在该sddl指令所涉及的源寄存器中的数据(源操作数)准备好之后,如图11所示,在步骤1101,该sddl指令从发射队列被送入处理器的访存单元(lsu)。

[0205]

然后,对该sddl指令中所包括的作为目的地址的内存地址ad进行处理,首先,在步骤1102,开始进行地址翻译以得到内存地址ad对应的物理地址pad,在进行地址翻译时,对地址高位x[rs1][xlen-1:xlen-ls]进行剥离,获得该内存地址ad本身记载的内存标记la’,并且对地址低位x[rs1][xlen-ls-1:0](即有效地址部分)进行实际的地址翻译,由此得到翻译后的带内存标记的物理地址pad。在地址翻译过程中,首先在步骤1103,查询tlb(翻译后备缓冲器)是否缓存有对应的页表项(pte),如果tlb查询缺失,则需要进一步查询页表以获得内存地址ad对应的物理地址pad,先将查询页表得到的页表项填充到tlb中,然后在步骤1104,重新发送地址请求,重新进入地址翻译流程,再次查询tlb,此时将tlb查询命中;如果tlb查询命中,则可直接返回内存地址ad对应的物理地址pad。

[0206]

如图11所示,接下来,在步骤1105中,使用该物理地址pad执行分裂出的等价于ldl指令的一个或多个微指令的微操作(以下描述为了简单起见,也简称“类ldl指令”),即根据该物理地址pad获得对应于该物理地址pad的内存标记la。使用该类ldl指令对应的物理地址pad访问一级缓存。在步骤1106中,如果一级缓存命中,即一级缓存的数据阵列中已经存储有该物理地址pad对应的数据da,相应地标记阵列也已经存储有该物理地址pad对应的内存标记la,因此可以获取该物理地址pad对应的内存标记la,并在步骤1108中,将内存标记la返回给处理器的lsu。如果一级缓存缺失,即一级缓存的数据阵列中尚未存储该物理地址pad对应的数据da,相应地标记阵列也没有存储该物理地址pad对应的内标记la,则向下级缓存(即二级缓存)请求读取物理地址pad的内存标记la。此时,二级缓存可以进行与一级缓存类似的操作,如果二级缓存仍然缺失,则需要到更下级的缓存或内存中读取对应的内存标记la。当下级缓存返回物理地址pad对应的内存标记la,同时也返回物理地址pad对应的数据da,一级缓存将返回的物理地址pad的内存标记la以及数据da彼此对应地填充到自身的标记阵列和数据阵列中;在步骤1107中,重新发送上述ldl指令以访问缓存,此时将缓存命中,在步骤1108中,将从缓存获得的内存标记la返回给处理器的lsu。

[0207]

接下来,在步骤1109中,lsu将内存标记la’和内存标记la进行比较,如果二者相同,则认为sddl指令要操作的内存地址ad与内存中的目标地址相匹配,写入操作安全,不存在安全违例;相反,如果二者不同,则不匹配,在步骤1120中,处理器进入异常处理。在内存标记la’和内存标记la彼此匹配的情形,在步骤1110中,处理器给rob发送bsy状态清除操作,即将该sddl在rob中的bsy状态修改为“执行完毕”,由此,在步骤1111中,rob指示可提交该sddl指令,当该sddl位于rob的头部时,实际执行数据存储操作,即将源操作数写入到内存汇中的目的地址(即内存地址ad)。

[0208]

根据所采用的写操作策略,如上所述可以采用直写、后写、写回等方式。例如,以直写方式为例,那么在将源操作数写入到目的地址的同时还将源操作数写入到缓存(例如一级缓存)中。在步骤1112中,在将源操作数写入到缓存时,使用上述物理地址pad查询该缓存,如果缓存命中,则将源操作数写入查询到的缓存行中,此时可以无需比较缓存中存储的内存标记与前述内存标记la’;如果缓存缺失,则如上所述可以选择写分配或非写分配方式,例如,以写分配方式为例,在步骤1113中,从内存中读取物理地址pad对应的数据,选择

缓存中的空闲缓存行或替换某一非空闲缓存行以写入该数据,然后唤醒该sddl指令,再次执行上述直写操作,由此在内存的物理地址pad和缓存的相应缓存行中写入源操作数。至此,到步骤1130,实施例中的sddl指令得以执行完成。

[0209]

在本公开的至少一个实施例中,对于上述sddl指令还提供状态寄存器以记录指令执行的状态,该寄存器可以称为执行(executed)寄存器,例如,这些状态的示例如下下表3所示:

[0210]

表3

[0211]

执行寄存器标志位说明000初始化状态(invalid)001可将指令分裂发送入缓存获取标记(get label)010获取标记失败,重新准备发送(label wakeup)011完成标记读取(done)100发送标记获取请求后进行等待(fired get label)101重新发送请求后进行等待(fired label wakeup)

[0212]

在图11中一并示出了执行寄存器(图示为“es”)的标志位的值,例如,在sddl指令被发射进入到lsu时,该执行寄存器的标志位的值为b000,而在该sddl指令分裂出ldl指令时,该执行寄存器的标志位的值为b001,等等。

[0213]

本公开实施例通过上述方法以及装置,可以防御攻击者利用缓冲区溢出或者uaf等攻击手段改变程序控制流走向,并最终实现事先准备的恶意代码段和与其类似的一系列攻击手段。

[0214]

例如,在有些机制下攻击者可以发现分配给内存的标记,从而能够实现非相邻内存访问、任意内存访问,并使用已被重新分配的释放内存,这些内存作为初始违例的一部分,可能还用于后续的原语。但是,在本公开的实施例中给定的内存标记是真随机数,攻击者无法获取生成真随机数的硬件生成器的值。面对释放的内存空间,本公开实施例中,将其保护的安全内存空间标记通过上述sdl指令赋值为0,则任何程序通过定制标记内存指令分配的安全指针的内存标记都是非0的标记值,因此能很好地避免指针对一个远距离未分配数据空间的访问出现一个随机性概率碰撞的问题,由此提高了系统的安全性。

[0215]

虽然标记产生单元用于随机分配的标记的数量受限于标记粒度的大小,但是标记内存为各种程序提供相当程度的概率性保护,而且在本公开的实施例中,例如使得每次标记匹配失败都中止程序进行异常处理,并且在新的程序中再次分配的内存标记在理论上只有很小的概率与之前分配的内存标记相同,因此本公开的实施例极大地保护了系统的安全性,防止受到此类攻击。

[0216]

本公开的一些实施例还提供了一种电子装置,该电子装置包括上述计算机装置,上述计算机装置包括上述缓存装置,或者可执行上述访存操作方法。

[0217]

图12为本公开至少一个实施例提供的一种电子装置的示意框图。本公开实施例中的电子装置可以包括但不限于诸如移动电话、笔记本电脑、数字广播接收器、pda(个人数字助理)、pad(平板电脑)、pmp(便携式多媒体播放器)、车载终端(例如车载导航终端)等等的移动终端以及诸如数字tv、台式计算机等等的固定终端。图12示出的电子装置1000仅仅是一个示例,不应对本公开实施例的功能和使用范围带来任何限制。

[0218]

例如,如图12所示,在一些示例中,电子装置1000包括处理装置,该处理装置可以包括上述任一实施例的处理装置,其可以根据存储在只读存储器(rom)1002中的程序或者从存储装置1008加载到随机访问存储器(ram)1003中的程序而执行各种适当的动作和处理。在ram 1003中,还存储有计算机系统操作所需的各种程序和数据。处理器1001、rom 1002以及ram1003通过总线1004被此相连。输入/输出(i/o)接口1005也连接至总线1004。

[0219]

例如,以下部件可以连接至i/o接口1005:包括例如触摸屏、触摸板、键盘、鼠标、摄像头、麦克风、加速度计、陀螺仪等的输入装置1006;包括诸如液晶显示器(lcd)、扬声器、振动器等的输出装置1007;包括例如磁带、硬盘等的存储装置1008;例如还可以包括诸如lan卡、调制解调器等的网络接口卡的通信装置1009。通信装置1009可以允许电子装置1000与其他设备进行无线或有线通信以交换数据,经由诸如因特网的网络执行通信处理。驱动器1010也根据需要连接至i/o接口1005。可拆卸存储介质1011,诸如磁盘、光盘、磁光盘、半导体存储器等等,根据需要安装在驱动器1010上,以便于从其上读出的计算机程序根据需要被安装入存储装置1008。虽然图12示出了包括各种装置的电子装置1000,但是应理解的是,并不要求实施或包括所有示出的装置。可以替代地实施或包括更多或更少的装置。

[0220]

例如,该电子装置1000还可以进一步包括外设接口(图中未示出)等。该外设接口可以为各种类型的接口,例如为usb接口、闪电(lighting)接口等。该通信装置1009可以通过无线通信来与网络和其他设备进行通信,该网络例如为因特网、内部网和/或诸如蜂窝电话网络之类的无线网络、无线局域网(lan)和/或城域网(man)。无线通信可以使用多种通信标准、协议和技术中的任何一种,包括但不局限于全球移动通信系统(gsm)、增强型数据gsm环境(edge)、宽带码分多址(w-cdma)、码分多址(cdma)、时分多址(tdma)、蓝牙、wi-fi(例如基于ieee 802.11a、ieee 802.11b、ieee 802.11g和/或ieee 802.11n标准)、基于因特网协议的语音传输(voip)、wi-max,用于电子邮件、即时消息传递和/或短消息服务(sms)的协议,或任何其他合适的通信协议。

[0221]

例如,电子装置1000可以为手机、平板电脑、笔记本电脑、电子书、游戏机、电视机、数码相框、导航仪、家用电器、通信基站、工业控制器、服务器等任何设备,也可以为任意的数据处理装置及硬件的组合,本公开的实施例对此不作限制。

[0222]

对于本公开,还有以下几点需要说明:

[0223]

(1)本公开实施例附图只涉及到与本公开实施例涉及到的结构,其他结构可参考通常设计。

[0224]

(2)在不冲突的情况下,本公开的实施例及实施例中的特征可以相互组合以得到新的实施例。

[0225]

以上仅是本公开的示范性实施方式,而非用于限制本公开的保护范围,本公开的保护范围由所附的权利要求确定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1