计算机系统以及可信计算方法与流程

1.本发明涉及一种可信计算,特别涉及可信计算的安全外设。

背景技术:

2.可信计算可以硬件划分方式提高计算机系统安全性。例如,计算机系统的系统内存可划分出隔离内存,只供可信计算。

3.如何设计可信计算的安全外设,为本技术领域一项重大课题。

技术实现要素:

4.根据本技术一种实施方式实现的一计算机系统包括一处理器、一系统内存、以及一芯片组。该处理器包括一般核、以及可信计算用的可信核。该系统内存提供一般内存、以及供可信计算使用的隔离内存。该芯片组耦接该处理器、该系统内存、以及多个外设,负责该处理器、该系统内存、以及该等外设之间的通信。该隔离内存备有一安全中断描述符表,相应该等外设中的安全外设所发起的安全中断。该可信核中一第一寄存器寄存一第一地址,指向该安全中断描述符表。该可信核的一局部高级可编程中断控制器提供有一中断仲裁器,仲裁该等外设经该芯片组所传来的中断。仲裁出的一目标中断是安全中断时,该中断仲裁器发出一安全中断请求信号、以及一安全中断向量,触发该可信核根据该第一寄存器,寻得该安全中断描述符表,并查找该安全中断描述符表决定一目标中断描述符,以执行相应的中断程序。

5.前述概念更用于实现一种可信计算方法。

6.本技术通过在芯片组中设置单独的安全中断控制器、或利用信息驱动中断(msi),在可信核中添加单独的安全中断描述符寄存器(第一寄存器)、安全中断描述符表、以及相应的安全中断处理机制,实现安全中断处理与一般中断处理的隔离。

7.下文特举实施例,并配合所附图示,详细说明本发明内容。

附图说明

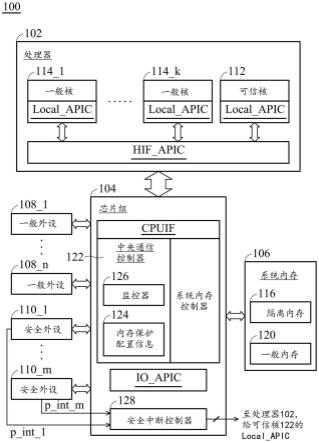

8.图1为根据本技术一种实施方式所实现的一计算机系统100;

9.图2以表格200说明内存保护配置信息124内容;

10.图3以表格300显示隔离内存116的基地址、以及隔离内存116的地址大小;

11.图4根据本技术一种实施方式图解处理器102端如何处理中断;

12.图5根据本技术一种实施方式图解安全中断控制器128细节;

13.图6根据本技术另一种实施方式图解安全中断控制器128细节;

14.图7根据本技术一种实施方式图解信息驱动中断(msi)的详细格式;

15.图8图解处理器102对外设的通信管理;且

16.图9图解外设对处理器102的通信管理。

17.【符号说明】

18.100:计算机系统;

19.102:处理器;

20.104:芯片组;

21.106:系统内存

22.108_1

…

108_n:一般外设;

23.110_1

…

110_m:安全外设;

24.112:可信核;

25.p_int_1

…

p_int_m:安全中断;

26.114_1

…

114_k:一般核;

27.116:隔离内存;

28.120:一般内存;

29.122:中央通信控制器;

30.124:内存保护配置信息;

31.126:监控器;

32.128:安全中断控制器;

33.200、300:表格;

34.204、206:字段;

35.404:中断仲裁器;

36.502:可编程中断控制器;

37.504、602:安全中断处理单元;

38.702:中断信息地址格式;

39.704:中断信息数据格式;

40.802:核辨识码;

41.804、904:地址;

42.902:外设辨识码;

43.cpuif:处理器接口;

44.hif_apic:主机接口高级可编程中断控制器;

45.idt、sidt:一般中断描述符表、安全中断描述符表;

46.idtr、sidtr:寄存器;

47.inta、sinta:一般中断响应信号、安全中断响应信号;

48.intr、sintr:一般中断请求信号、安全中断请求信号;

49.iv、siv:一般中断向量、安全中断向量;

50.io_apic:输入输出高级可编程中断控制器;

51.local_apic:局部高级可编程中断控制器。

具体实施方式

52.以下叙述列举本发明的多种实施例。以下叙述介绍本发明的基本概念,且并非意图限制本发明内容。实际发明范围应依照权利要求书界定。

53.关于可信计算,系统内存通常隔离出一段空间供其使用,称为隔离内存,与一般内

存区别。隔离内存并不允许非可信核(normal core,又称一般核)、以及非安全输入输出装置(normal device,又称一般外设)进行存取,只允许可信计算专用的可信核(trusted core,如tpcm技术的)、以及安全输入输出装置(security device,又称安全外设)进行访问。

54.本技术在芯片组(chipset)中,定义一组可配置的内存保护配置信息,除了记载隔离信息(如,以隔离内存各范围(range)的基地址、以及尺寸,标示隔离内存于系统内存的位置),更记载各外设(由外设辨识码识别)信息,如外设类型(例如一般外设、或安全外设)等。如此一来,根据芯片组中内存保护配置信息记载的信息(包含隔离信息、各外设信息),相应一般外设对该隔离内存所发起的存取请求,芯片组会确实将其回绝。反之,相应安全外设对该隔离内存所发起的存取请求,芯片组会准予执行。芯片组可允许一般外设访问一般内存。特别是,芯片组可禁止安全外设访问一般内存。

55.另外,操作系统分配给各外设(包括安全外设和一般外设)的输入输出范围(i/o range;使用的访问指令例如是in、或out等)、或内存映射输入输出范围(mimo range;使用的是内存访问指令,如mov)等信息,也可以记载在芯片组中(例如,记载在上述内存保护配置信息)。

56.一般核或可信核请求访问外设时,会发送一外设访问请求给芯片组。外设访问请求可带有核辨识码(core id),供芯片组辨别是一般核、还是可信核提出该外设访问请求。如此一来,若是一般核请求操作安全外设(即一般核要访问的地址落入芯片组所载的安全外设的输入输出范围、或安全外设内存映射输入输出范围),芯片组会将之回绝。反之,若是可信核请求操作安全外设,芯片组会准予执行。若是一般核要求操作一般外设,芯片组会准予执行。若是可信核要求操作一般外设,芯片组可将之回绝。具体细节后文会结合附图详述。

57.外设(一般外设或安全外设)请求存取系统内存时,会发送一系统内存存取请求给芯片组。系统内存存取请求可带有外设辨识码,根据芯片组中存储的各外设信息及外设辨识码,芯片组可辨别是一般外设、还是安全外设提出该系统内存存取请求。系统内存存取请求还带有地址,用于标识外设要存取的系统内存的地址。根据芯片组中存储的隔离信息和系统内存存取请求带有的地址,芯片组可辨别外设要访问的是一般内存还是隔离内存。如此一来,若是一般外设请求存取隔离内存,芯片组会将之回绝。反之,若是安全外设请求存取隔离内存,芯片组会准予执行。若是一般外设请求存取一般内存,芯片组会准予执行。若是安全外设请求存取一般内存,芯片组可将之回绝。具体细节后文会结合附图详述。

58.本技术更为安全外设设计中断技术。

59.图1为根据本技术一种实施方式所实现的一计算机系统100,包括一处理器102、一芯片组104、一系统内存106、多种外设(包括一般外设108_1

…

108_n、以及安全外设110_1

…

110_m,其中n和m为大于等于1的整数)。

60.处理器102为多处理器,这些可为同构(即这些的结构相同),其一可编程为可信核112(可信计算用),其余为一般核114_1

…

114_k(k为大于等于1的整数)。处理器102耦接芯片组104,且芯片组104还耦接系统内存106、一般外设108_1

…

108_n、以及安全外设110_1

…

110_m。芯片组104负责该处理器102、该系统内存106、以及该等外设(108_1

…

108_n与110_1

…

110_m)之间的通信。

61.系统内存106可为动态存取存储器(dram)、或者静态存取存储器(sram),其空间规划包括:隔离内存116、以及一般内存120。隔离内存116需对一般核114_1

…

114_k、以及一般外设108_1

…

108_n隔离,仅供可信核112、以及安全外设110_1

…

110_m存取,供可信计算使用。一般内存120则可以是规划给一般核114_1

…

114_k使用。

62.芯片组104是在中央通信控制器(central traffic controller,负责处理器102到外设、以及外设到处理器102的数据传输)122存储一组内存保护配置信息124、以及提供一监控器(monitor)126。内存保护配置信息124可用于存储前文所述的隔离信息、各外设信息,等信息。根据内存保护配置信息124所载内容,监控器126确实排除一般外设108_1

…

108_n对隔离内存116的存取,而允许安全外设110_1

…

110_m对隔离内存116的存取,并可允许一般外设108_1

…

108_n存取一般内存120。特别是,根据内存保护配置信息124所载内容(如前文所述的隔离信息、各外设信息等),监控器126可拒绝安全外设110_1

…

110_m存取一般内存120。具体细节,后文会结合第2、3、9图详述。

63.监控器126更会根据内存保护配置信息124所载内容(如前文所述的隔离信息、各外设信息等),阻绝一般核114_1

…

114_k操作安全外设110_1

…

110_m。根据内存保护配置信息124所载内容(如前文所述的隔离信息、各外设信息等),监控器126允许可信核112操作安全外设110_1

…

110_m,允许一般核114_1

…

114_k操作一般外设108_1

…

108_n,且更可阻绝可信核112操作一般外设108_1

…

108_n。具体细节,后文会结合第2、8图详述。

64.内存保护配置信息124可存储在芯片组104的一组寄存器、或一静态随机存储器中,本发明对此不做限制。内存保护配置信息124可以是如下设定。

65.系统上电后,可信核112会先于一般核114_1

…

114_k运行,校验可信固件(trusted firmware,如tpcm firmware)、以及基本输入输出系统(bios)。校验后,可信核112运行可信固件,配置可信核112所能访问的外设。不同外设是以外设辨识码(device id)区别。可信核112是令内存保护配置信息124记载配置之外设辨识码(device id)、输入输出范围(i/o range)204、以及内存映射输入输出范围(mimo range)206。内存保护配置信息124可更为各外设记载外设类型(安全外设、或一般外设)。内存保护配置信息124也可记载隔离内存116的隔离信息,标示该隔离内存116于该系统内存106的位置。一种实施方式中,隔离内存116是由分开的多段范围(range)组成,各范围的基地址、以及尺寸,都可载于内存保护配置信息124,以完整标示该隔离内存116。

66.特别是,只有可信核112可以修改内存保护配置信息124的内容。

67.图2以表格200说明图1的内存保护配置信息124内容,包括有效位(例如,0:内容无效;1:内容有效)、外设辩识码(id)、外设类型(例如,0:安全外设;1:一般外设)、输入输出范围(i/o range)204、内存映射输入输出范围(mimo range)206。输入输出范围(i/o range)204与内存映射输入输出范围(mimo range)206可择一填入,为外设与该处理器通信的一通信范围。需要注意的是,图2中列举的外设辨识码为5的安全外设只是一个例子,图2所示的表格200中可以包含多个安全外设的条目,还可以包含多个一般外设的条目,本发明中对此不做限制。

68.图3以表格300显示隔离内存116的基地址、以及隔离内存116的地址大小。需要注意的是,图3中列举的隔离内存基地址20000和隔离内存地址尺寸100只是一个例子。本发明中可以设置不同的隔离内存基地址和隔离内存地址尺寸,还可以在表格300中设置多个条

目以指示系统内存中的多个隔离内存。

69.一种实施方式中,相应一目标外设对该系统内存106的一存取请求(带有一外设辨识码),该监控器126将该组内存保护配置信息124记载的隔离信息(图3表300)与该存取请求的一存取地址进行比对,判断该存取地址是否落入该隔离内存116。该目标外设是安全外设110_1

…

110_m时(如图2表200该条目所示),该监控器126允许落入该隔离内存116的该存取请求的执行。该目标外设是一般外设108_1

…

108_n时,该监控器126禁止落入该隔离内存116的该存取请求的执行。该监控器126更在该目标外设为一般外设108_1

…

108_n时,允许落入该一般内存(隔离内存116外的空间)的该存取请求的执行。该监控器126更可在该目标外设为安全外设110_1

…

110_m时,禁止落入该一般内存(隔离内存116外的空间)的该存取请求的执行。

70.相应该处理器102的一目标核发出的一外设访问请求(带有一核辨识码),该监控器126可根据该外设访问请求的一访问地址,查询该组内存保护配置信息124,寻得符合的通信范围(比对图2中的字段204、206),并基于符合的通信范围,更自该组内存保护配置信息124寻得一目标外设辨识码、与一目标外设类型,从而得知该外设访问请求的一目标外设为何、以及该目标外设是安全外设(例如,图1中的安全外设110_1、

…

、或110_m)、还是一般外设(例如,图1中的一般外设108_1、

…

、或108_n)。例如,当一外设访问请求包含的访问地址是输入输出地址(io address)、且值为25时,由于图2中外设辨识码为5的外设对应的输入输出范围(字段204)值为23-26(25落入范围23-26),监控器126判断出该外设的辨识码为5、且该外设为安全外设(因为其外设类型为0)。当一外设访问请求包含的访问地址是内存映射输入输出地址(mmio address)、且值为10050时,由于图2中外设辨识码为5的外设对应的内存映射输入输出范围(字段206)值为10000-10100(10050落入范围10000-10100),监控器126判断出该外设的辨识码为5、且该外设为安全外设(因为其外设类型为0)。

71.该监控器126可根据该目标核的核辨识码(core id),判断该目标核为一般核(例如,图1中的一般核114_1、

…

、或114_k)、或可信核(例如图1中的可信核112)。该目标核为可信核112、且该目标外设为安全外设110_1

…

110_m时,该监控器126允许该目标核访问该目标外设。该目标核为一般核114_1

…

114_k、但该目标外设为安全外设110_1

…

110_m时,该监控器126禁绝该目标核访问该目标外设。该目标核为一般核114_1

…

114_k、且该目标外设为一般外设108_1

…

108_n时,该监控器126允许该目标核访问该目标外设。该目标核为可信核112、但该目标外设为一般外设108_1

…

108_n时,该监控器126可禁绝该目标核访问该目标外设。

72.回到图1,关于外设中断,芯片组104除了为一般外设108_1

…

108_n提供有输入输出高级可编程中断控制器io_apic(apic为advanced programmable interrupt controller简写),更为安全外设110_1

…

110_m设计一安全中断控制器128。安全外设110_1

…

110_m各以一外设-芯片组引脚连接到安全中断控制器128,以发出安全中断信号p_int_1

…

p_int_m。例如,安全外设110_1以一外设-芯片组引脚连接到安全中断控制器128,以发出安全中断p_int_1;安全外设110_m以一外设-芯片组引脚连接到安全中断控制器128,以发出安全中断p_int_m,等等。安全外设110_1

…

110_m发出的安全中断,将经安全中断控制器128传递给处理器102,交给可信核112搭配的局部高级可编程中断控制器local_apic处理。

73.安全外设110_1

…

110_m也可以信息方式发出中断。此实施例不须使用该安全中断控制器128。安全外设110_1

…

110_m可发出信息驱动中断(message signaled interrupt,简称msi),由芯片组104通过处理器接口cpuif传给处理器102,再由主机接口高级可编程中断控制器hif_apic交给可信核112搭配的局部高级可编程中断控制器local_apic处理。

74.可信核112包括相应安全外设110_1

…

110_m的设计,所搭配的局部高级可编程中断控制器local_apic也有相对调整。隔离内存116也需为安全外设110_1

…

110_m的安全中断,存储相应的安全中断描述符表。

75.图4根据本技术一种实施方式图解处理器102端如何处理中断。

76.如前所述,系统内存106包含一般内存120以及隔离内存116。一般内存120载有一般中断描述符表idt。隔离内存116载有一安全中断描述符表sidt。安全中断描述符表sidt条列安全中断描述符,相应该等安全外设110_1

…

110_m所发起的安全中断。根据安全中断描述符,可信核112可以查找并执行各安全中断对应的中断程序。一般外设108_1

…

108_n的一般中断描述符,则载于一般内存120的一般中断描述符表idt,相应该等一般外设108_1

…

108_n所发起的一般中断。根据一般中断描述符,一般核或可信核可以查找并执行各一般中断对应的中断程序。

77.可信核112的以寄存器idtr记载一般中断描述符表idt的地址,并以寄存器sidtr记载安全中断描述符表sidt的地址。为可信核112设计的局部高级可编程中断控制器local_apic包括一中断仲裁器(interrupt arbiter)404。根据中断类型(非关安全与否),中断仲裁器404进行优先级判断,以发出中断请求信号(一般中断请求信号intr、或安全中断请求信号sintr)、以及中断向量(一般中断向量iv、或安全中断向量siv)给可信核112的,等待可信核112的响应中断响应信号(一般中断响应信号inta、或安全中断响应信号sinta)。相应一般中断,可信核112的是根据寄存器idtr所载地址,使用一般中断向量iv查询一般中断描述符表idt,获得相应的一般中断描述符,以执行相应的一般中断程序。相应安全中断,可信核112的是根据寄存器sidtr所载地址,使用安全中断向量siv查询安全中断描述符表sidt,获得相应的安全中断描述符,以执行相应的安全中断程序。

78.图5根据本技术一种实施方式图解安全中断控制器128细节。安全中断控制器128包括一可编程中断控制器(pic)502、以及一安全中断处理单元504。安全外设110_1

…

110_m各自的外设-芯片组引脚是连接到可编程中断控制器502。可编程中断控制器502仲裁安全外设110_1

…

110_m发出的安全中断,相应优先级最高的安全中断,产生一安全中断请求信号sintr、以及一安全中断向量siv给安全中断处理单元504,待该安全中断处理单元504响应安全中断响应信号sinta。

79.安全中断处理单元504耦接于该可编程中断控制器502、以及该处理器102之间。该安全中断处理单元504是经对应该等安全外设110_1

…

110_m的多个芯片组-处理器引脚连接该处理器102,且根据该可编程中断控制器502提供的该安全中断向量siv,设置该等芯片组-处理器引脚中的对应引脚,以向该处理器102发送安全中断p_int_1

…

p_int_m。每个安全外设对应一个外设-芯片组引脚和一个芯片组-处理器引脚。例如,安全外设110_1对应一个外设-芯片组引脚和一个芯片组-处理器引脚,以向该处理器102发送安全中断p_int_1;安全外设110_m对应一个外设-芯片组引脚和一个芯片组-处理器引脚,以向该处理器102发送安全中断p_int_m;等等。如图所示,该等芯片组-处理器引脚是连接至该可信核112的该

局部高级可编程中断控制器local_apic。可信核112的该局部高级可编程中断控制器local_apic根据芯片组-处理器引脚设置状况,区别目前回报处理器102的安全中断是对应哪一个安全外设。在一实施例中,安全中断p_int_1为高电平、其它安全中断都为低电平时,可信核112的该局部高级可编程中断控制器local_apic判定目前回报处理器102的安全中断是对应安全外设110_1;当安全中断p_int_m为高电平、其它安全中断都为低电平时,可信核112的该局部高级可编程中断控制器local_apic判定目前回报处理器102的安全中断是对应安全外设110_m;等等。

80.图6根据本技术另一种实施方式图解安全中断控制器128细节。相较图5,安全中断处理单元602是直接将该可编程中断控制器502提供的该安全中断向量siv传递给该处理器102,由该可信核112的该局部高级可编程中断控制器local_apic接收、处理。

81.图5以及图6这种使用安全中断控制器128的技术,称为可编程中断控制模式(pic mode)。安全中断控制器128中具有可编程中断控制器(pic)502。安全外设110_1

…

110_m各以一外设-芯片组引脚将安全中断p_int_1

…

p_int_m送入该安全中断控制器128,经可编程中断控制器(pic)502所在路径转给该可信核112进行处理。至于可信核112如何处理接收到的安全中断p_int_1

…

p_int_m,前文中已结合图4做了说明,此处就不赘述了。

82.在一实施例中,如图1所示,安全外设110_1

…

110_m可不特别设置外设-芯片组引脚以连接到安全中断控制器128,而是以信息方式发出中断,称为高级可编程中断控制模式(apic mode)。安全外设110_1

…

110_m可采外设组件互连标准(peripheral component interconnect,简称pci),发出信息驱动中断(message signaled interrupt,简称msi)给芯片组104,再由芯片组104通过处理器接口cpuif传给处理器102,再由处理器102上的主机接口高级可编程中断控制器hif_apic交给可信核112搭配的局部高级可编程中断控制器local_apic处理。

83.图7根据本技术一种实施方式图解信息驱动中断(msi)702。如图7所示,芯片组104从外设接收到的信息驱动中断702的基地址字段值一般为0xfee。当芯片组104的监控器126判断此信息驱动中断702源自一安全外设时,会将其基地址字段改为一特定值,例如0xfea,以将此信息驱动中断702标注为安全中断。信息驱动中断702还包含其他字段,例如中断向量等等,此处就不赘述了。在另一实施例中,芯片组104的监控器126判断此信息驱动中断702源自一安全外设后,会将其基地址字段改为另一特定值,例如0xfeb。本发明对源自安全外设的信息驱动中断的基地址字段的具体值不做限定,只要与0xfee不同即可。

84.芯片组104是将信息驱动中断(msi)交给主机接口高级可编程中断控制器hif_apic。信息驱动中断702的基地址字段若为前述特定值(例如,0xfea或其他与0xfee不同的值),主机接口高级可编程中断控制器hif_apic会认定其为安全中断,并将之交给可信核112搭配的局部高级可编程中断控制器local_apic处理。可信核112处理安全中断的方式已在前文中结合图4做了介绍,此处就不赘述了。

85.图8、图9更根据本技术实施方式图解监控器126详细动作。

86.图8图解处理器102对外设的通信管理。请同时参考图1和图8,如前文所述,当处理器102请求访问外设时,会发送一外设访问请求给芯片组104。此外设访问请求包含核辨识码(core id)802、地址804以及数据806。地址804为输入输出地址(io address)或内存映射输入输出地址(mmio address)。数据806包含处理器102发送给外设的操作命令(例如,重置

外设的命令)或数据(例如,写入外设的数据)。处理器至外设信道包含多个位(bit),标注该核辨识码802。如前文所述,设置在芯片组104中央通信控制器122上的监控器126,可根据此核辨识码802,判断目前外设访问请求来自可信核112、或一般核114_1

…

114_k;监控器126可根据地址804判断处理器102请求访问的外设是一般外设还是安全外设;进而实现以下访问规则:

87.规则1:只有可信核112可以访问安全外设110_1

…

110_m;以及

88.规则2:只有一般核114_1

…

114_k可以访问一般外设108_1

…

108_n。

89.一种实施方式中,监控器126会根据请求访问的地址(addr)804查询内存保护配置信息124所载的表格200(图2)。根据表格200中,符合地址(addr)804的输入输出范围(i/o range)204、或内存映射输入输出范围(mimo range)206的条目,可以获知要求访问的外设类型(0:安全外设;1:一般外设),即可判断是否符合规则1以及规则2。更具体的说,当地址(addr)804为输入输出地址(io address)时,监控器126可以将地址804与表格200中的条目的输入输出范围(i/o range)204进行比较,从而获得符合地址(addr)804的条目。当地址(addr)804为内存映射输入输出地址(mmio address)时,监控器126可以将地址804与表格200中的条目的内存映射输入输出范围(mimo range)206进行比较,从而获得符合地址(addr)804的条目。更详细的比较操作细节,前文已经做过举例说明,此处就不赘述了。

90.图9图解外设对处理器102的通信管理。请同时参考图1和图9,如前文所述,当外设请求访问系统内存106(从系统内存106读取数据、或向系统内存106写入数据)时,会发送一存取请求给芯片组104。该存取请求包含外设辨识码902、地址904以及数据906。当外设请求向系统内存106写入数据时,数据906包含外设要写入系统内存106的数据。外设发出的系统内存存取请求会带有一外设辨识码(device id)902。如前文所述,设置在芯片组104中央通信控制器122上的监控器126,可根据此外设辨识码902,判断目前存取请求来自一般外设108_1

…

108_n、或安全外设110_1

…

110_m,进而实现以下访问规则:

91.规则3:允许安全外设110_1

…

110_m访问隔离内存116;

92.规则4:不允许安全外设110_1

…

110_m访问隔离内存116外的其它系统内存106空间(一般内存120);以及

93.规则5:允许一般外设108_1

…

108_n访问一般内存120,但不允许一般外设108_1

…

108_n访问隔离内存116。

94.一种实施方式中,监控器126会根据存取请求所带的外设辨识码902查询内存保护配置信息124所载的表格200(图2)。根据表格200中,符合的外设辨识码,找出发出请求的外设类型(0:安全外设;1:一般外设)。监控器126更会根据外设请求存取的地址(addr)904,查询图3的表格300,判断外设请求访问的是否为隔离内存116。如图3所示,当隔离内存基地址为20000、隔离内存地址尺寸为100时,表示的内存空间范围为从20000到20100。当外设请求存取的地址(addr)904为20050时,由于20050大于20000、且小于20100,监控器126判断外设请求访问的是隔离内存116。根据以上查表结果,监控器可判断外设对系统内存106发出的存取请求是否符合规则3、规则4、以及规则5。

95.以下举例说明多种外设使用。

96.外设需要访问系统内存106时,高速外设是使用直接存储器存取(dma)技术与处理器102交换数据。用于对高速外设进行配置的配置寄存器空间可以是内存映射输入/输出

(mimo)空间、或输入/输出(i/o)空间。直接存储器存取(dma)、内存映射输入/输出(mimo)操作、或输入/输出(i/o)操作执行时,芯片组104内设置的监控器126会检查是否访问隔离内存116、或操作目标是否为安全外设110_1

…

110_m。特别是,安全外设110_1

…

110_m使用的安全中断不同于一般外设108_1

…

108_n的一般中断。安全中断的相应处理程序存放在可信操作系统(trusted os),由可信核112执行,从而实现安全外设110_1

…

110_m与一般外设108_1

…

108_n之间的隔离。

97.外设可以主动要求存取系统内存106。

98.网卡为一种高速外设。操作网卡发送数据时,处理器102会将数据准备在系统内存106上,并通过网卡控制器的配置寄存器(例如,将配置寄存器的一个位(bit)的值由0改为1)通知网卡将数据取走。网卡是以直接存储器存取(dma)去系统内存106取走数据,再以中断通知处理器102做进一步处理。网卡接收到外来数据时,会使用处理器102预先在网卡控制器的配置寄存器中配置好的内存地址范围,用直接存储器存取(dma)将外来数据写入系统内存106,再产生中断通知处理器102处理做进一步处理。在一实施例中,网卡为安全外设,由可信核112操作,使用的是隔离内存116空间,采用的是安全中断。

99.串口(universal asynchronous receiver/transmitter,uart)装置

─

如键盘、鼠标等等

─

为一种低速外设。串口接收到数据后,会发中断给处理器102,使处理器102藉指令in自相应的串口地址取得数据。反之,操作串口发送数据时,处理器102通过输入/输出(i/o)操作,配置好相关的配置寄存器,藉指令out向相应的串口地址写数据。在输入/输出(i/o)操作时,芯片组104的监控器126会检查这些操作的目标是否为安全外设110_1

…

110_m,且安全外设是使用安全中断,确实与一般外设108_1

…

108_n隔离。至于芯片组104的监控器126如何检查这些操作的目标是否为安全外设110_1

…

110_m、安全外设如何使用安全中断等操作已在前面做了描述,此处就不赘述了。

100.本技术通过在芯片组中设置一组内存保护配置信息,将外设设置为一般外设或安全外设,并将系统内存分为一般内存和隔离内存,从而实现只允许安全外设访问隔离内存、只允许一般外设访问一般内存。另外,本技术通过在芯片组中设置单独的安全中断控制器、或利用信息驱动中断(msi),在可信核中添加单独的安全中断描述符寄存器、安全中断描述符表、以及相应的安全中断处理机制,实现安全中断处理与一般中断处理的隔离。通过上述设计,本技术实现的安全外设具有非常高的安全性。

101.虽然本发明已以优选实施例公开如上,然其并非用以限定本发明,本领域技术人员,在不脱离本发明的精神和范围内,当可做些许更动与润饰,因此本发明的保护范围当视所附权利要求书界定范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1