一种可双边沿采样的延时型强PUF

一种可双边沿采样的延时型强puf

技术领域

1.本发明涉及延时型强puf,尤其是涉及一种可双边沿采样的延时型强puf。

背景技术:

2.物理不可克隆函数(physical unclonable function,puf)利用半导体制造工艺过程中的随机和固有变化作为熵源,可生成一些具有随机性、唯一性、防篡改等特性的固有数字id,为低成本和轻量级设备的安全问题提供一种解决方案。

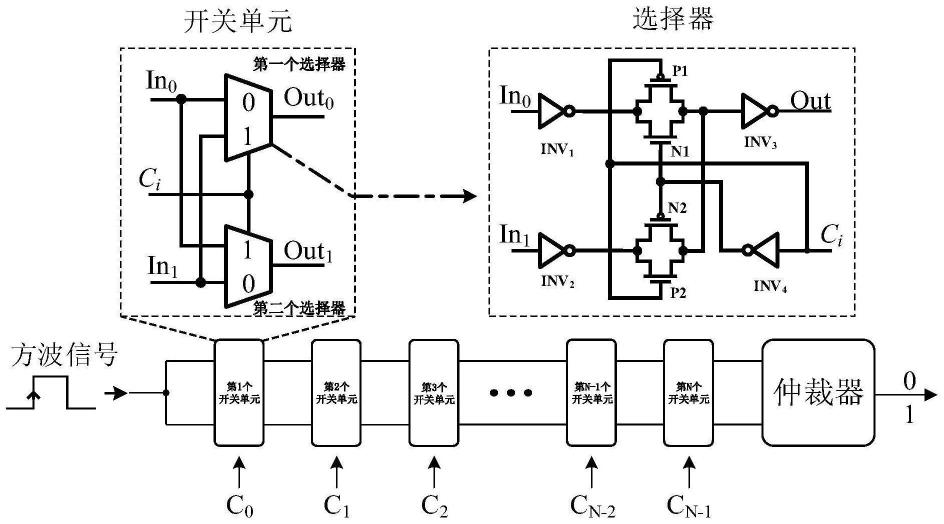

3.仲裁器puf(arbiter puf,apuf)电路作为最早提出的强puf电路之一,其结构如图1所示。该仲裁器puf中,当激励信号ci为低电平时,选择器中mos管p1与n1导通,p2与n2关断,选择器输出端out传输in0信号;反之,当激励信号ci为高电平时,选择器中mos管p1与n1关断,p2与n2导通,选择器输出端out传输in1信号。即当激励信号ci为低电平时,开关单元的输出端out0与out1分别传输in0与in1端信号,而当激励信号ci为高电平时,开关单元的输出端out0与out1分别传输in1与in0端信号。该仲裁器puf通过各级的激励信号,便可将同一方波信号沿不同的传输路径抵达仲裁器,再利用仲裁器测量两条传输路径上的延时便可提取电路存在的工艺偏差,获取得到激励响应对(challenge response pairs,crps),可在资源受限的物联网安全设备中实现设备认证,信息加密传输等。但随着机器学习的发展,科研工作者可以通过机器学习算法对传统强puf进行建模分析,从而对输出响应进行精准预测。文献《j. liu, y. zhu, c.

ꢀ‑

h. chan and r. p. martins, "a 0.04% ber strong puf with cell-bias-based crps filtering and background offset calibration," in ieee transactions on circuits and systems i: regular papers, vol. 67, no. 11, pp. 3853-3865, nov. 2020.》中提出了基于亚阈值电流阵列的动态放大器puf单元,该动态放大器puf单元具有高度非线性的亚阈值特性,可有效的抵御机器学习攻击,但该动态放大器puf单元在产生1.8

×

10

19

组crps时核心面积高达22400μm2。文献《a. venkatesh, a. b. venkatasubramaniyan, x. xi and a. sanyal, "0.3 pj/bit machine learning resistant strong puf using subthreshold voltage divider array," in ieee transactions on circuits and systems ii: express briefs, vol. 67, no. 8, pp. 1394-1398, aug. 2020.》中提出了一种基于亚阈值分压器的强puf,该强puf利用工作在阈值电压区域的mos的非线性电流-电压关系提升所提结构的抗机器学习攻击能力,该强puf产生1.8

×

10

19

组crps所需面积也到达2800μm2。文献《h. zhuang, x. xi, n. sun, and m. orshansky,

ꢀ“

a strong subthreshold current array puf resilient to machine learning attacks,

”ꢀ

ieee trans. circuits syst. i, reg. papers, vol. 67, no. 1, pp. 135

–

144, jan. 2020.》中提出了一种基于亚阈值电流阵列的强puf,该强puf利用pmos管阵列工作在亚阈值区域所表现出来的电流非线性关系,使电路具备抗机器学习攻击能力,但该强puf在产生3.7

×

10

19

组crps时,所需的面积达到了44400μm2。

4.上述几种强puf,虽然在抗机器学习攻击能力方面得到了提升,但往往都需要较大的硬件开销,不能实现抗机器学习攻击能力和小硬件开销的兼容,同时产生的激励响应对

数量未得到明显提升。

技术实现要素:

5.本发明要解决的技术问题是提供一种在具有较强抗机器学习攻击能力的同时,还具有较小的硬件开销,能够实现抗机器学习攻击能力和小硬件开销兼容,并且能够产生较多的激励响应对的可双边沿采样的延时型强puf。

6.本发明解决上述技术问题所采用的技术方案为:一种可双边沿采样的延时型强puf,包括n个开关单元,每个所述的开关单元均具有第一输入端、第二输入端、控制端、第一输出端和第二输出端,每个所述的开关单元的控制端均用于接入激励信号,每个所述的开关单元在其控制端接入的激励信号控制下,能够将其第一输入端和第二输入端接入的方波信号在其内部并行或者交叉传输至其第一输出端和第二输出端输出,第n个开关单元的第一输出端和第n+1个开关单元的第一输入端连接,第n个开关单元的第二输出端和第n+1个开关单元的第二输入端连接,n=1,2,

…

,n-1,所述的延时型强puf还包括两个仲裁器,将两个仲裁器分别称为第一仲裁器和第二仲裁器,所述的第一仲裁器和所述的第二仲裁器均具有第一输入端、第二输入端和输出端,第n个开关单元的第一输出端分别与所述的第一仲裁器的第一输入端和所述的第二仲裁器的第一输入端连接,第n个开关单元的第二输出端分别与所述的第一仲裁器的第二输入端和所述的第二仲裁器的第二输入端连接,所述的第一仲裁器用于判断其第一输入端和第二输入端接入的信号在上升沿处延时时长的先后顺序并生成相应信号在其输出端输出,所述的第二个仲裁器用于判断其第一输入端和第二输入端接入的信号在下降沿处延时时长的先后顺序并生成相应信号在其输出端输出;每个所述的开关单元均包括第一pmos管、第二pmos管、第三pmos管、第四pmos管、第五pmos管、第六pmos管、第七pmos管、第八pmos管、第一nmos管、第二nmos管、第三nmos管、第四nmos管、第五nmos管、第六nmos管、第七nmos管和第八nmos管,所述的第一pmos管的栅极和所述的第一nmos管的栅极连接且其连接端为所述的开关单元的第一输入端in0,所述的第一pmos管的源极、所述的第四pmos管的源极、所述的第五pmos管的源极和所述的第八pmos管的源极均接入电源电压vdd,所述的第一pmos管的漏极、所述的第一nmos管的漏极、所述的第二pmos管的栅极、所述的第二pmos管的源极、所述的第二nmos管的栅极和所述的第二nmos管的源极连接,所述的第二pmos管的漏极、所述的第二nmos管的漏极、所述的第三pmos管的源极和所述的第三nmos管的源极连接,所述的第三pmos管的栅极、所述的第三nmos管的栅极、所述的第七pmos管的栅极和所述的第七nmos管的栅极连接且其连接端为所述的开关单元的控制端ci,所述的第三pmos管的漏极、所述的第七nmos管的漏极、所述的第四pmos管的栅极和所述的第四nmos管的栅极连接,所述的第三nmos管的漏极、所述的第七pmos管的漏极、所述的第八nmos管的栅极和所述的第八pmos管的栅极连接,所述的第四pmos管的漏极和所述的第四nmos管的漏极连接且其连接端为所述的开关单元的第一输出端out0,所述的第一nmos管的源极、所述的第四nmos管的源极、所述的第五nmos管的源极和所述的第八nmos管的源极均接地,所述的第五pmos管的栅极和所述的第五nmos管的栅极连接且其连接端为所述的开关单元的第二输入端in1,所述的第五pmos管的漏极、所述的第五nmos管的漏极、所述的第六pmos管的栅极、所述的第六pmos管的源极、所述的第六nmos管的栅极和所述的第六nmos管的源极连接,所述的第六pmos管的漏极、所述的第六nmos管的漏极、所述的第七pmos

管的源极和所述的第七nmos管的源极连接,所述的第八pmos管的漏极和所述的第八nmos管的漏极连接且其连接端为所述的开关单元的第二输出端out1。

7.所述的第一仲裁器包括第一二输入与非门和第二二输入与非门,所述的第一二输入与非门和所述的第二二输入与非门均具有第一输入端、第二输入端和输出端,所述的第一二输入与非门的第一输入端为所述的第一仲裁器的第一输入端,所述的第一二输入与非门的输出端和所述的第二二输入与非门的第一输入端连接,所述的第二二输入与非门的第二输入端为所述的第一仲裁器的第二输入端,所述的第一二输入与非门的第二输入端与所述的第二二输入与非门的输出端连接且其连接端为所述的第二仲裁器的输出端;所述的第二仲裁器包括第一二输入或非门和第二二输入或非门,所述的第一二输入或非门和所述的第二二输入或非门均具有第一输入端、第二输入端和输出端,所述的第一二输入或非门的第一输入端为所述的第二仲裁器的第一输入端,所述的第一二输入或非门的输出端和所述的第二二输入或非门的第一输入端连接,所述的第二二输入或非门的第二输入端为所述的第二仲裁器的第二输入端,所述的第一二输入或非门的第二输入端与所述的第二二输入或非门的输出端连接且其连接端为所述的第二仲裁器的输出端。

8.与现有技术相比,本发明的优点在于通过设置第一仲裁器和第二仲裁器,第一仲裁器用于判断其第一输入端和第二输入端接入的信号在上升沿处延时时长的先后顺序并生成相应信号在其输出端输出,第二仲裁器用于判断其第一输入端和第二输入端接入的信号在下降沿处延时时长的先后顺序并生成相应信号在其输出端输出,且每个开关单元均通过第一pmos管、第二pmos管、第三pmos管、第四pmos管、第五pmos管、第六pmos管、第七pmos管、第八pmos管、第一nmos管、第二nmos管、第三nmos管、第四nmos管、第五nmos管、第六nmos管、第七nmos管和第八nmos管这8个mos管构成,当开关单元的第一输入端in0接入方波信号时,由第一pmos管和第一nmos管n1构成的反相器对开关单元的第一输入端in0接入的方波信号进行反相和整形,保证该方波信号达到第二pmos管与第二nmos管n2构成的延时单元前,方波信号的上升时间和下降时间均较小,由于第二pmos管与第二nmos管的栅极与源极作为延时单元的输入端,当到达该延时单元的输入端的方波信号为低电平时,会使第二pmos管导通,第二nmos管n2关断,但又由于pmos管在传输低电平时,存在阈值损失,致使由第二pmos管与第二nmos管n2的漏极构成的该延时单元的输出端无法快速的下拉到低电平(地电平vss),只能下拉至等于第二pmos管的阈值电压,然而由于工艺偏差,致使每个开关单元中第二pmos管的阈值电压各不同,因此每个开关单元中由第二pmos管与第二nmos管n2的漏极构成的延时单元的输出端下拉的电平的电压值也各不相同,最终就会导致每个开关单元中方波信号的延时各不相同;同理,当到达该延时单元的输入端的方波信号为高电平时,会致使第二nmos管n2导通,第二pmos管关断,由于nmos管在传输高电平时,存在阈值损失,致使由第二pmos管与第二nmos管n2的漏极构成的该延时单元的输出端无法快速的上拉至高电平(电源电压vdd),只能达到电源电压vdd减去第二nmos管n2的阈值电压;由于制造过程中无法避免的工艺偏差,使nmos管的阈值电压也各不相同,从而致使每个开关单元中第二nmos管n2的阈值电压各不同,因此每个开关单元中由第二pmos管与第二nmos管n2的漏极构成的延时单元的输出端下拉的电平的电压值也各不相同,最终就会导致每个开关单元中方波信号的延时各不相同;随后由第二pmos管与第二nmos管n2的漏极构成的延时单元的输出端输出的方波信号经由第三pmos管和第三nmos管n3这两个信号传输管,当控制端接入

的激励信号ci=0,第三pmos管导通,第三nmos管n3关闭,方波信号经过第三pmos管传输到由第四pmos管与第四nmos管n4构成的反相器的输入端,由第四pmos管与第四nmos管n4构成的反相器对其输入端接入的方波信号再次进行反相,从开关单元的第一输出端out0输出与其第一输入端in0接入的方波信号同相的方波信号。反之,当控制端接入的激励信号ci=1,第三pmos管关闭,第三nmos管n3导通,方波信号经过第三nmos管n3传输到由第八pmos管与第八nmos管n8构成的反相器的输入端,由第八pmos管与第八nmos管n8构成的反相器对其输入端接入的方波信号再次进行反相,从开关单元的第二输出端out1输出与其第一输入端in0接入的方波信号同相的方波信号。当开关单元的第二输入端in1接入方波信号时,由第五pmos管和第五nmos管n5构成的反相器对开关单元的第二输入端in1接入的方波信号进行反相和整形,保证该方波信号达到第六pmos管与第六nmos管n6构成的延时单元前,方波信号的上升时间和下降时间均较小。由于第六pmos管与第二nmos管的栅极与源极作为延时单元的输入端,当到达该延时单元的输入端的方波信号为低电平时,会使第六pmos管导通,第六nmos管n6关断,但又由于pmos管在传输低电平时,存在阈值损失,致使由第六pmos管与第六nmos管n6的漏极构成的该延时单元的输出端无法快速的下拉到低电平(vss),只能下拉至等于第六pmos管的阈值电压,然而由于工艺偏差,致使每个开关单元中第六pmos管的阈值电压各不同,因此每个开关单元中由第六pmos管与第六nmos管n6的漏极构成的延时单元的输出端下拉的电平的电压值也各不相同,最终就会导致每个开关单元中方波信号的延时各不相同;同理,当到达该延时单元的输入端的方波信号为高电平时,会致使第六nmos管n6导通,第六pmos管关断,由于nmos管在传输高电平时,存在阈值损失,致使由第六pmos管与第六nmos管n6的漏极构成的该延时单元的输出端无法快速的上拉至高电平(电源电压vdd),只能达到电源电压vdd减去第六nmos管n6的阈值电压。由于制造过程中无法避免的工艺偏差,使nmos管的阈值电压也各不相同,从而致使每个开关单元中第六nmos管n6的阈值电压各不同,因此每个开关单元中由第六pmos管与第六nmos管n6的漏极构成的延时单元的输出端下拉的电平的电压值也各不相同,最终就会导致每个开关单元中方波信号的延时各不相同;随后由第六pmos管与第六nmos管n6的漏极构成的延时单元的输出端输出的方波信号经由第七pmos管和第七nmos管n7这两个信号传输管,当控制端接入的激励信号ci=0,第七pmos管导通,第七nmos管n7关闭,方波信号经过第七pmos管传输到由第八pmos管与第八nmos管n8构成的反相器的输入端,由第八pmos管与第八nmos管n8构成的反相器对其输入端接入的方波信号再次进行反相,从开关单元的第一输出端out0输出与其第二输入端in1接入的方波信号同相的方波信号。反之,当控制端接入的激励信号ci=1,第七pmos管关闭,第七nmos管n7导通,方波信号经过第七nmos管n7传输到由第四pmos管与第四nmos管n4构成的反相器的输入端,由第四pmos管与第四nmos管n4构成的反相器对其输入端接入的方波信号再次进行反相,从开关单元的第一输出端out0输出与其第二输入端in1接入的方波信号同相的方波信号;由此本发明通过开关单元的简单结构设计,在具有较强抗机器学习攻击能力的同时,还具有较小的硬件开销,能够实现抗机器学习攻击能力和小硬件开销兼容,并且采用两个仲裁器实现双边沿采样,能够产生较多的激励响应对。

附图说明

9.图1为传统的仲裁器puf的结构示意图;

图2为本发明的可双边沿采样的延时型强puf的结构示意图;图3为本发明的可双边沿采样的延时型强puf的开关单元的电路图;图4为本发明的可双边沿采样的延时型强puf的第一仲裁器的电路图;图5为本发明的可双边沿采样的延时型强puf的第二仲裁器的电路图;图6为本发明的可双边沿采样的延时型强puf的开关单元的版图;图7为本发明的可双边沿采样的延时型强puf的开关单元与传统的仲裁器puf的开关单元进行1000次蒙特卡洛仿真波形图;图8(a)为本发明的可双边沿采样的延时型强puf的输出响应在上升沿处的灰度图(64

×

128);图8(b)为本发明的可双边沿采样的延时型强puf的输出响应在下降沿处的灰度图(64

×

128);图8(c)为本发明的可双边沿采样的延时型强puf的输出响应在上升沿处的平均灰度图;图8(d)为本发明的可双边沿采样的延时型强puf的输出响应在下降沿处的平均灰度图;图9为发明的可双边沿采样的延时型强puf的片间汉明距离测试图;图10为发明的可双边沿采样的延时型强puf的片内汉明距离测试图;图11为发明的可双边沿采样的延时型强puf与现有几种强puf机器学习攻击预测率曲线图。

具体实施方式

10.以下结合附图实施例对本发明作进一步详细描述。

11.实施例:如图2所示,一种可双边沿采样的延时型强puf,包括n个开关单元,每个开关单元均具有第一输入端、第二输入端、控制端、第一输出端和第二输出端,每个开关单元的控制端均用于接入激励信号,每个开关单元在其控制端接入的激励信号控制下,能够将其第一输入端和第二输入端接入的方波信号在其内部并行或者交叉传输至其第一输出端和第二输出端输出,第n个开关单元的第一输出端和第n+1个开关单元的第一输入端连接,第n个开关单元的第二输出端和第n+1个开关单元的第二输入端连接,n=1,2,

…

,n-1,延时型强puf还包括两个仲裁器,将两个仲裁器分别称为第一仲裁器和第二仲裁器,第一仲裁器和第二仲裁器均具有第一输入端、第二输入端和输出端,第n个开关单元的第一输出端分别与第一仲裁器的第一输入端和第二仲裁器的第一输入端连接,第n个开关单元的第二输出端分别与第一仲裁器的第二输入端和第二仲裁器的第二输入端连接,第一仲裁器用于判断其第一输入端和第二输入端接入的信号在上升沿处延时时长的先后顺序并生成相应信号在其输出端输出,第二个仲裁器用于判断其第一输入端和第二输入端接入的信号在下降沿处延时时长的先后顺序并生成相应信号在其输出端输出;如图3所示,每个开关单元均包括第一pmos管p1、第二pmos管p2、第三pmos管p3、第四pmos管p4、第五pmos管p5、第六pmos管p6、第七pmos管p7、第八pmos管p8、第一nmos管n1、第二nmos管n2、第三nmos管n3、第四nmos管n4、第五nmos管n5、第六nmos管n6、第七nmos管n7和第八nmos管n8,第一pmos管p1的栅极和第一nmos管n1的栅极连接且其连接端为开关单元的第一输入端in0,第一pmos管p1的源

极、第四pmos管p4的源极、第五pmos管p5的源极和第八pmos管p8的源极均接入电源电压vdd,第一pmos管p1的漏极、第一nmos管n1的漏极、第二pmos管p2的栅极、第二pmos管p2的源极、第二nmos管n2的栅极和第二nmos管n2的源极连接,第二pmos管p2的漏极、第二nmos管n2的漏极、第三pmos管p3的源极和第三nmos管n3的源极连接,第三pmos管p3的栅极、第三nmos管n3的栅极、第七pmos管p7的栅极和第七nmos管n7的栅极连接且其连接端为开关单元的控制端ci,第三pmos管p3的漏极、第七nmos管n7的漏极、第四pmos管p4的栅极和第四nmos管n4的栅极连接,第三nmos管n3的漏极、第七pmos管p7的漏极、第八nmos管n8的栅极和第八pmos管p8的栅极连接,第四pmos管p4的漏极和第四nmos管n4的漏极连接且其连接端为开关单元的第一输出端out0,第一nmos管n1的源极、第四nmos管n4的源极、第五nmos管n5的源极和第八nmos管n8的源极均接地,第五pmos管p5的栅极和第五nmos管n5的栅极连接且其连接端为开关单元的第二输入端in1,第五pmos管p5的漏极、第五nmos管n5的漏极、第六pmos管p6的栅极、第六pmos管p6的源极、第六nmos管n6的栅极和第六nmos管n6的源极连接,第六pmos管p6的漏极、第六nmos管n6的漏极、第七pmos管p7的源极和第七nmos管n7的源极连接,第八pmos管p8的漏极和第八nmos管n8的漏极连接且其连接端为开关单元的第二输出端out1。

12.如图4和图5所示,本实施例中,第一仲裁器包括第一二输入与非门nand1和第二二输入与非门nand2,第一二输入与非门nand1和第二二输入与非门nand2均具有第一输入端、第二输入端和输出端,第一二输入与非门nand1的第一输入端为第一仲裁器的第一输入端,第一二输入与非门nand1的输出端和第二二输入与非门nand2的第一输入端连接,第二二输入与非门nand2的第二输入端为第一仲裁器的第二输入端,第一二输入与非门nand1的第二输入端与第二二输入与非门nand2的输出端连接且其连接端为第二仲裁器的输出端;第二仲裁器包括第一二输入或非门nor1和第二二输入或非门nor2,第一二输入或非门nor1和第二二输入或非门nor2均具有第一输入端、第二输入端和输出端,第一二输入或非门nor1的第一输入端为第二仲裁器的第一输入端,第一二输入或非门nor1的输出端和第二二输入或非门nor2的第一输入端连接,第二二输入或非门nor2的第二输入端为第二仲裁器的第二输入端,第一二输入或非门nor1的第二输入端与第二二输入或非门nor2的输出端连接且其连接端为第二仲裁器的输出端。

13.本发明的可双边沿采样的延时型强puf的每个开关单元中,在其控制端接入的激励信号作用下,其第一输入端和第二输入端接入的方波信号在其内部会并行活着交叉传输至其第一输出端和第二输出端进行输出。当开关单元的第一输入端in0接入方波信号时,由第一pmos管p1和第一nmos管n1构成的反相器对开关单元的第一输入端in0接入的方波信号进行反相和整形,保证该方波信号达到第二pmos管p2与第二nmos管n2构成的延时单元前,方波信号的上升时间和下降时间均较小。由于第二pmos管p2与第二nmos管的栅极与源极作为延时单元的输入端,当到达该延时单元的输入端的方波信号为低电平时,会使第二pmos管p2导通,第二nmos管n2关断,但又由于pmos管在传输低电平时,存在阈值损失,致使由第二pmos管p2与第二nmos管n2的漏极构成的该延时单元的输出端无法快速的下拉到低电平(vss),只能下拉至等于第二pmos管p2的阈值电压,然而由于工艺偏差,致使每个开关单元中第二pmos管p2的阈值电压各不同,因此每个开关单元中由第二pmos管p2与第二nmos管n2的漏极构成的延时单元的输出端下拉的电平的电压值也各不相同,最终就会导致每个开关单元中方波信号的延时各不相同;同理,当到达该延时单元的输入端的方波信号为高电平

时,会致使第二nmos管n2导通,第二pmos管p2关断,由于nmos管在传输高电平时,存在阈值损失,致使由第二pmos管p2与第二nmos管n2的漏极构成的该延时单元的输出端无法快速的上拉至高电平(电源电压vdd),只能达到电源电压vdd减去第二nmos管n2的阈值电压。由于制造过程中无法避免的工艺偏差,使nmos管的阈值电压也各不相同,从而致使每个开关单元中第二nmos管n2的阈值电压各不同,因此每个开关单元中由第二pmos管p2与第二nmos管n2的漏极构成的延时单元的输出端下拉的电平的电压值也各不相同,最终就会导致每个开关单元中方波信号的延时各不相同;随后由第二pmos管p2与第二nmos管n2的漏极构成的延时单元的输出端输出的方波信号经由第三pmos管p3和第三nmos管n3这两个信号传输管,当控制端接入的激励信号ci=0,第三pmos管p3导通,第三nmos管n3关闭,方波信号经过第三pmos管p3传输到由第四pmos管p4与第四nmos管n4构成的反相器的输入端,由第四pmos管p4与第四nmos管n4构成的反相器对其输入端接入的方波信号再次进行反相,从开关单元的第一输出端out0输出与其第一输入端in0接入的方波信号同相的方波信号。反之,当控制端接入的激励信号ci=1,第三pmos管p3关闭,第三nmos管n3导通,方波信号经过第三nmos管n3传输到由第八pmos管p8与第八nmos管n8构成的反相器的输入端,由第八pmos管p8与第八nmos管n8构成的反相器对其输入端接入的方波信号再次进行反相,从开关单元的第二输出端out1输出与其第一输入端in0接入的方波信号同相的方波信号。当开关单元的第二输入端in1接入方波信号时,由第五pmos管p5和第五nmos管n5构成的反相器对开关单元的第二输入端in1接入的方波信号进行反相和整形,保证该方波信号达到第六pmos管p6与第六nmos管n6构成的延时单元前,方波信号的上升时间和下降时间均较小。由于第六pmos管p6与第二nmos管的栅极与源极作为延时单元的输入端,当到达该延时单元的输入端的方波信号为低电平时,会使第六pmos管p6导通,第六nmos管n6关断,但又由于pmos管在传输低电平时,存在阈值损失,致使由第六pmos管p6与第六nmos管n6的漏极构成的该延时单元的输出端无法快速的下拉到低电平(vss),只能下拉至等于第六pmos管p6的阈值电压,然而由于工艺偏差,致使每个开关单元中第六pmos管p6的阈值电压各不同,因此每个开关单元中由第六pmos管p6与第六nmos管n6的漏极构成的延时单元的输出端下拉的电平的电压值也各不相同,最终就会导致每个开关单元中方波信号的延时各不相同;同理,当到达该延时单元的输入端的方波信号为高电平时,会致使第六nmos管n6导通,第六pmos管p6关断,由于nmos管在传输高电平时,存在阈值损失,致使由第六pmos管p6与第六nmos管n6的漏极构成的该延时单元的输出端无法快速的上拉至高电平(电源电压vdd),只能达到电源电压vdd减去第六nmos管n6的阈值电压。由于制造过程中无法避免的工艺偏差,使nmos管的阈值电压也各不相同,从而致使每个开关单元中第六nmos管n6的阈值电压各不同,因此每个开关单元中由第六pmos管p6与第六nmos管n6的漏极构成的延时单元的输出端下拉的电平的电压值也各不相同,最终就会导致每个开关单元中方波信号的延时各不相同;随后由第六pmos管p6与第六nmos管n6的漏极构成的延时单元的输出端输出的方波信号经由第七pmos管p7和第七nmos管n7这两个信号传输管,当控制端接入的激励信号ci=0,第七pmos管p7导通,第七nmos管n7关闭,方波信号经过第七pmos管p7传输到由第八pmos管p8与第八nmos管n8构成的反相器的输入端,由第八pmos管p8与第八nmos管n8构成的反相器对其输入端接入的方波信号再次进行反相,从开关单元的第一输出端out0输出与其第二输入端in1接入的方波信号同相的方波信号。反之,当控制端接入的激励信号ci=1,第七pmos管p7关闭,第七nmos管n7导通,

方波信号经过第七nmos管n7传输到由第四pmos管p4与第四nmos管n4构成的反相器的输入端,由第四pmos管p4与第四nmos管n4构成的反相器对其输入端接入的方波信号再次进行反相,从开关单元的第一输出端out0输出与其第二输入端in1接入的方波信号同相的方波信号。

14.本实施例的可双边沿采样的延时型强puf中,当第n个开关单元的第一输出端和第二输出端输出两路方波信号时,第一仲裁器和第二仲裁器判决第n个开关单元的第一输出端out0和第二输出端out1的延时偏差。当两路方波信号进入第一仲裁器时,第一个仲裁器为根据由两个与非门构成的rs触发器,当其第一输入端和第二输入端接入的两路方波信号均为低电平时,其输出端输出高电平,但当其第一输入端和第二输入端接入的两路方波信号中,有一路方波信号先跳变为高电平,便会致使第一仲裁器发生不同的判决,当其上路信号(即其第一输入端接入的方波信号)先跳变为高电平,便会使其输出端输出高电平,当其下路信号(即其第二输入端接入的方波信号)先跳变为高电平时,会使输出端输出低电平,最终,当滞后的一路信号发生跳变时,此时两路输入信号均为高电平,不会使第一仲裁器的输出端的信号发生跳变,最终可以实现对第一仲裁器的输出端信号的保持。综上,即方波信号经由第一仲裁器时,实现判决输入其内的方波信号在上升沿处延时时长的先后。而第n个开关单元的第一输出端和第二输出端输出的两路方波信号输入第二仲裁器时,由于第二仲裁器是由两个或非门构成的rs触发器,当两路方波信号均为高电平时,第二仲裁器的输出端输出低电平,当上路信号(即其第一输入端接入的方波信号)先跳变为低电平时,第二仲裁器的输出端仍输出低电平,但当下路信号(即其第二输入端接入的方波信号)率先跳变为低电平时,第二仲裁器输出端则输出高电平,同理当滞后的一路信号也跳变为低电平后,第二仲裁器的输出端输出的信号仍然会保持不变。即第二个仲裁器可以实现判决两路方波信号在下降沿处延时时长的先后顺序。因此可以提取出puf电路在上升沿和下降沿处的激励响应对,实现可双边沿采集,puf电路工作完成。相较于采用一个仲裁器的传统apuf电路而言,激励响应对的数量可以实现倍增。

15.本发明的可双边沿采样的延时型强puf的开关单元的版图如图6所示,在开关单元的数量为64个时,本发明的可双边沿采样的延时型强puf面积仅为289μm2,而crps数量达到3.7

×

10

19

。由此可知本发明的可双边沿采样的延时型强puf可以实现较小的面积下产生较多的crps。

16.将同一方波信号输入至如图1所示的传统强puf的开关单元和本发明的可双边沿采样的延时型强puf开关单元后,进行1000次蒙特卡洛仿真,本发明的可双边沿采样的延时型强puf的开关单元与传统的仲裁器puf的开关单元进行1000次蒙特卡洛仿真波形图如图7所示。分析图7可知,本发明的可双边沿采样的延时型强puf的开关单元在上升沿和下降沿处拥有更大的延时偏差和更大的上升沿时长和下降沿时长,本发明的可双边沿采样的延时型强puf输出响应的稳定性得以提升。

17.通过灰度图可以直观的观测到puf的随机性,其中黑色像素点表示提取出的响应为逻辑“1”,相反白色像素点则表示提取的响应为逻辑“0”。对本发明的可双边沿采样的延时型强puf进行多次蒙特卡洛仿真,得到多个蒙特卡洛仿真图,从这些蒙特卡洛仿真图中随机选择一个在上升沿和下降沿处输出8192组响应的灰度图,如图8(a)与图8(b)所示,分析图8(a)可知,本发明的可双边沿采样的延时型强puf在上升沿处为“1”的概率为50.15%,分

析图8(b)可知,本发明的可双边沿采样的延时型强puf在下降沿处为“1”的概率为50.03%,十分接近于理想值(50%)。平均灰度图便是将各次仿真所得灰度图进行叠加求平均处理。对本发明的可双边沿采样的延时型强puf进行39次蒙特卡洛仿真,将双边沿各39

×

8192组响应做平均灰度图,本发明的可双边沿采样的延时型强puf的输出响应在上升沿处的平均灰度图如图8(c)所示,本发明的可双边沿采样的延时型强puf的输出响应在下降沿处的平均灰度图如图8(d)所示。分析图8(c)与图8(d)可知,本发明的可双边沿采样的延时型强puf在上升沿和下降沿处的灰度值均集中在50%左右,没有出现明显的空间伪影,有着优良的随机性。

18.对本发明的可双边沿采样的延时型强puf进行39次蒙特卡洛仿真,提取出方波信号上升沿和下降沿的响应,分别测试各边沿以及混合后的片间汉明距离,如图9所示。分析图9可知,显示任意两个puf上升沿和下降沿的片间汉明距离分别为49.863%和49.793%,且双边沿响应混合后的平均汉明距离为50.166%,均接近理想值50%,表明不仅两个延时型强puf相互独立,同一个延时型强puf的上升沿和下降沿提取出来的响应也是相互独立,可作为唯一的crps进行设备认证等安全措施。

19.通过改变本发明的可双边沿采样的延时型强puf工作温度,使其在-10

°

c到100

°

c之间工作。并调节电源电压vdd,使本发明的可双边沿采样的延时型强puf正常工作1.075v到1.25v之间。测量在标准条件(工作电压为1.2v,环境温度为27

°

c)与不同工作条件下响应之间的汉明距离,如图10所示。分析图10可知,在对方波信号上升沿进行仿真的曲线中,其片内汉明距离为0.06173,趋近于理想值0,即稳定性约为94%,在对方波信号的下降沿进行仿真的曲线中,其片内的汉明距离为0.06494,即稳定性为93.5%。实验表明本发明的可双边沿采样的延时型强puf在上升沿和下降沿均有良好的稳定性。

20.针对puf电路常见的机器学习攻击方式有逻辑回归(lr)、支持向量机(svm)和人工神经网络(ann)等算法,通过对puf电路的crps进行学习训练,最终达到对实际puf电路建模,以预测出puf电路产生的密钥。为验证本发明的可双边沿采样的延时型强puf的抗机器学习能力,分别对本发明的可双边沿采样的延时型强puf和传统的apuf进行测试,测试100组至5000组crps,预测结果如图11所示。图11中, apuf-lr为利用逻辑回归攻击apuf的预测结果图; apuf-svm为利用支持向量机攻击apuf的预测结果图;apuf-ann为利用人工神经网络攻击apuf的预测结果图; re-puf-lr为利用逻辑回归攻击本发明的可双边沿采样的延时型强puf,在上升沿处预测结果图; fe

ꢀ‑

puf-lr为利用逻辑回归攻击本发明的可双边沿采样的延时型强puf,在下降沿处预测结果图; re-puf-svm为利用支持向量机攻击本发明的可双边沿采样的延时型强puf,在上升沿处预测结果图; fe

ꢀ‑

puf-svm为利用支持向量机攻击本发明的可双边沿采样的延时型强puf,在下降沿处预测结果图; re-puf-ann为利用人工神经网络机攻击本发明的可双边沿采样的延时型强puf,在上升沿处预测结果图; fe

ꢀ‑

puf-ann为利用人工神经网络攻击本发明的可双边沿采样的延时型强puf,在下降沿处预测结果图;分析图11可知,传统apuf进行抗机器学习攻击能力测试时,当训练集达到5000组数时,lr、svm以及ann的预测率分别为96.95%,95.50%以及97.93%,其apuf容易被机器学习攻击建模。而本发明的可双边沿采样的延时型强puf的上升沿(rising edge,re)处的crps与下降沿(falling edge,fe)处的crps进行抗机器学习攻击测试,在上升沿处lr、svm以及ann的预测率则分别为52.65%,48.75%和50.45%,下降沿处的lr、svm以及ann预测率分别为

50.40%,50.55%和50.65%。本发明的可双边沿采样的延时型强puf抗机器学习能力较传统apuf显著提升。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1