将存储器模型映射至FPGA片内存储器的方法及系统与流程

将存储器模型映射至fpga片内存储器的方法及系统

技术领域

1.本发明涉及芯片仿真设计领域,尤其涉及一种将硬件描述语言的存储器模型映射至fpga片内存储器的方法及系统。

背景技术:

2.ic芯片产业快速发展,为了验证芯片功能是否正常,芯片开发初期通常需要进行芯片仿真验证。当芯片规模较大时,采用纯软件仿真会耗费大量时间,使用芯片仿真加速器可大大缩短仿真验证时间。芯片仿真加速器将可综合的代码实现到fpga运行,仿真速度将会得到极大提高,或者直接使用fpga做原型验证。得益于fpga强大的并行运算特性,基于fpga的芯片仿真加速器或芯片原型验证系统都可极大提高芯片仿真验证速度。

3.芯片仿真加速及原型验证系统中,传统rtl memory模型映射至fpga片内存储器的方法为直接采用fpga厂家提供的eda工具编译生成,存在以下不足:

4.多端口读/写memory无法映射至fpga片内存储器,只能采用查找表或寄存器实现;

5.异步memory无法映射至fpga片内存储器,只能采用查找表或寄存器实现;

6.当待测试验证的设计规模较大,存在映射至fpga资源的不确定性。

7.当rtl memory无法转换映射至fpga片内存储器时,会占用非常有限且宝贵的fpga查找表或寄存器资源,成为芯片仿真加速及原型验证系统上的瓶颈,工程编译出错,验证失败。因此,如何提供一种将rtl memory模型映射至fpga片内存储器系统是业界亟待解决的问题。

技术实现要素:

8.本发明的目的是针对现有技术的一些类型的硬件描述语言的存储器模型无法映射至fpga片内存储器的技术问题,本发明提出一种将硬件描述语言的存储器模型映射至fpga片内存储器的方法及系统。

9.本发明实施例中,提供了一种将硬件描述语言的存储器模型映射至fpga片内存储器的方法,其包括:

10.从硬件描述语言中识别出描述存储器的二维数组,识别出存储器的参数并生成实例化的存储器模块;

11.根据存储器的参数选择相应规格的fpga并采用fpga片内存储器原语重构相同规格的存储器ip;

12.对重构的存储器ip进行实例化,并替换所述实例化的存储器模块。

13.本发明实施例中,所述存储器的参数包括数据宽度、地址深度、读写模式和端口数量。

14.本发明实施例中,根据存储器的参数选择相应规格的fpga并采用fpga片内存储器原语重构相同规格的存储器ip,还包括:

15.根据识别出的存储器的端口数,采用快速时钟将识别出的存储器的多端口并行处

理转换为单端口串行处理,来适配fpga片内存储器原语接口。

16.本发明实施例中,根据存储器的参数选择相应规格的fpga并采用fpga片内存储器原语重构相同规格的存储器ip,还包括:

17.根据存储器的读写模式来对其进行等价处理,将其转换为可综合fpga片内存储器的同步读写模式。

18.本发明实施例中,对重构的存储器ip进行实例化,并替换所述实例化的存储器模块,包括:

19.对重构的存储器ip进行实例化时,将其内部增加的快速时钟端口拉线连接至系统快速时钟;

20.写数据、写地址及写使能端口分别连接所述实例化的存储器模块的写侧信号;

21.读数据、读地址及读使能端口同样分别连接所述实例化的存储器模块的读侧信号。

22.本发明实施例中,还提供了一种将硬件描述语言的存储器模型映射至fpga片内存储器的系统,其包括:

23.存储器识别模块,用于从硬件描述语言中识别出描述存储器的二维数组,识别出存储器的参数并生成实例化的存储器模块;

24.存储器ip重构模块,用于根据存储器的参数选择相应规格的fpga并采用fpga片内存储器原语重构相同规格的存储器ip;

25.存储器替换模块,用于对重构的存储器ip进行实例化,并替换所述实例化的存储器模块。

26.本发明实施例中,所述存储器的参数包括数据宽度、地址深度、读写模式和端口数量。

27.本发明实施例中,所述存储器ip重构模块还用于根据识别出的存储器的端口数,采用快速时钟将识别出的存储器的多端口并行处理转换为单端口串行处理,来适配fpga片内存储器原语接口。

28.本发明实施例中,所述存储器ip重构模块还用于根据存储器的读写模式来对其进行等价处理,将其转换为可综合fpga片内存储器的同步读写模式。

29.本发明实施例中,所述存储器替换模块对重构的存储器ip进行实例化,并替换所述实例化的存储器模块,包括:

30.对重构的存储器ip进行实例化时,将其内部增加的快速时钟端口拉线连接至系统快速时钟;

31.写数据、写地址及写使能端口分别连接所述实例化的存储器模块的写侧信号;

32.读数据、读地址及读使能端口同样分别连接所述实例化的存储器模块的读侧信号。

33.与现有技术相比较,采用本发明的将硬件描述语言的存储器模型映射至fpga片内存储器的方法及系统,可实现自动将硬件描述语言的存储器模型转换为fpga片内存储器,极大地减少了fpga查找表和寄存器资源使用,从而解决芯片仿真加速器及原型验证过程中一些类型的硬件描述语言的存储器模型无法映射至fpga片内存储器的技术问题。

附图说明

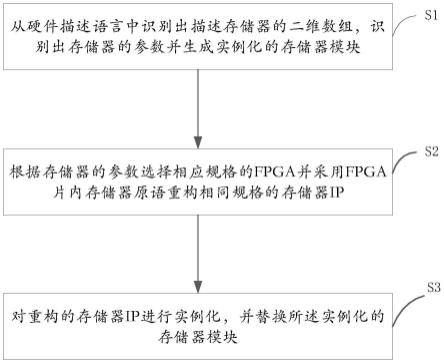

34.图1是本发明实施例的将硬件描述语言的存储器模型映射至fpga片内存储器的方法的流程图。

35.图2是本发明实施例的将硬件描述语言的存储器模型映射至fpga片内存储器的系统的结构示意图。

具体实施方式

36.如图1所示,本发明实施例中,提供了一种将硬件描述语言的存储器模型映射至fpga片内存储器的方法,其包括步骤s1-s3。下面分别进行说明。

37.步骤s1:从硬件描述语言中识别出描述存储器的二维数组,识别出存储器的参数并生成实例化的存储器模块。

38.需要说明的是,集成电路硬件描述语言通常采用rtl源代码,在rtl源代码涉及中存在定义的用于描述存储器的二维数组信号user_memory,写侧访问信号由写时钟、写数据、写地址与写使能构成;读侧访问信号由读时钟、读数据、读地址与读使能构成。本发明实施例中,对用户rtl源代码进行细化处理,并识别出二维数组user_memory,提取出相关参数并创建生成对应的实例化的存储器模块,将实例化的存储器模块的写侧和读侧端口固定。所述存储器的参数包括数据宽度、地址深度、读写模式和端口数量。

39.步骤s2:根据存储器的参数选择相应规格的fpga并采用fpga片内存储器原语重构相同规格的存储器ip。

40.需要说明的是,fpga片内存储器主要包括lutram及bram。lutram具有多而快的特点,总体容量较小,适用于小容量的memory;bram是块存储器,最小单位为36kbits或20kbits,总体容量适中,适用于中等容量的memory。这里将小于8kbits的user memory类型设为lutram,否则类型设为bram,从而使得选择的fpga片内存储器与硬件描述语言中的存储器的规格相适应。为使重构的存储器ip,确定性映射至lutram或bram,需要调用厂家原语实现来实现存储器的实体部分。

41.由于fpga片内存储器通常是只有一个串行数据端口,为了与原来的存储器的多端口进行匹配,本发明实施例中,根据识别出的存储器的端口数,采用快速时钟将识别出的存储器的多端口并行处理转换为单端口串行处理,来适配fpga片内存储器原语接口。本发明实施例中,采用时分复用的方法,引入快速时钟fast_clk,将多端口存储器操作采用时分复用的模式进行处理,即低速的多端口并行处理转换为高速的单端口串行处理;另外,对于异步读操作模式,要求ip在单个时钟周期完成,这里采用快速时钟实现对重构的存储器ip进行同步读写,以达到低频时钟域异步读行为等同的效果。

42.进一步地,本步骤中,还根据存储器的读写模式来对其进行等价处理,将其转换为可综合fpga片内存储器的同步读写模式。本步骤中,需要生成重构的存储器ip的控制器,所述控制器用于生成快速时钟域信号对重构的存储器ip的读写进行控制,分别为写侧通道控制和读侧通道控制,其控制方式分别如下:

43.写侧通道

44.1)各端口写数据、写地址及写使能都使用写时钟同步寄存一拍;

45.2)各端口快速时钟提取慢速写时钟上升沿,作为快速时钟域写使能信号;

46.3)各端口提取快速时钟域写使能信号生效时刻对应的写数据,作为快速时钟域写数据信号;

47.4)各端口提取快速时钟域写使能信号生效时刻对应的写地址,作为快速时钟域写地址信号;

48.5)各端口轮询,生成快速时钟域串行写使能、写数据及写地址信号,接入memory存储实体端口。

49.读侧通道

50.1)各端口读使能及读地址使用快速时钟同步寄存一拍;

51.2)各端口轮询,生成快速时钟域串行读使能及读地址信与,接入memory存储实体端口;

52.3)各端口轮询时生成对应的端口读id;

53.4)通过读id和memory存储实体端口的串行读数据,恢复各端口的读数据。

54.步骤s3:对重构的存储器ip进行实例化,并替换所述实例化的存储器模块。

55.本发明实施例中,对重构的存储器ip进行实例化,并替换所述实例化的存储器模块,包括:

56.对重构的存储器ip进行实例化时,将其内部增加的快速时钟端口拉线连接至系统快速时钟;

57.写数据、写地址及写使能端口分别连接所述实例化的存储器模块的写侧信号;

58.读数据、读地址及读使能端口同样分别连接所述实例化的存储器模块的读侧信号。

59.如图2所示,本发明实施例中,还提供了一种将硬件描述语言的存储器模型映射至fpga片内存储器的系统,其包括存储器识别模块1、存储器ip重构模块2和存储器替换模块3。下面分别进行说明。

60.所述存储器识别模块1,用于从硬件描述语言中识别出描述存储器的二维数组,识别出存储器的参数并生成实例化的存储器模块。所述存储器的参数包括数据宽度、地址深度、读写模式和端口数量。

61.所述存储器ip重构模块2,用于根据存储器的参数选择相应规格的fpga并采用fpga片内存储器原语重构相同规格的存储器ip。所述存储器ip重构模块2还用于根据识别出的存储器的端口数,采用快速时钟将识别出的存储器的多端口并行处理转换为单端口串行处理,来适配fpga片内存储器原语接口。进一步地,所述存储器ip重构模块2还用于根据存储器的读写模式来对其进行等价处理,将其转换为可综合fpga片内存储器的同步读写模式。具体的,若为存储器的读写模式同步模式,则将原时钟先打拍再进行等价处理;若为异步模式,无需打拍,直接进行等价处理。

62.所述存储器替换模块3,用于对重构的存储器ip进行实例化,并替换所述实例化的存储器模块。

63.本发明实施例中,所述存储器替换模块3对重构的存储器ip进行实例化,并替换所述实例化的存储器模块,包括:

64.对重构的存储器ip进行实例化时,将其内部增加的快速时钟端口拉线连接至系统快速时钟;

65.写数据、写地址及写使能端口分别连接所述实例化的存储器模块的写侧信号;

66.读数据、读地址及读使能端口同样分别连接所述实例化的存储器模块的读侧信号。

67.综上所述,采用本发明的将硬件描述语言的存储器模型映射至fpga片内存储器的方法及系统,可实现自动将硬件描述语言的存储器模型转换为fpga片内存储器,极大地减少了fpga查找表和寄存器资源使用,从而解决芯片仿真加速器及原型验证过程中一些类型的硬件描述语言的存储器模型无法映射至fpga片内存储器的技术问题。

68.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1