用于AI推理芯片的芯片验证方法、装置、设备及介质与流程

用于ai推理芯片的芯片验证方法、装置、设备及介质

技术领域

1.本发明涉及芯片验证领域,具体涉及一种用于ai推理芯片的芯片验证方法、装置、设备及介质。

背景技术:

2.ai推理芯片的验证工作需要在芯片设计生产不同阶段对不同抽象层级模型进行验证,包括软件层面的寄存器传输模型(rtl)验证以及硬件层面的硬件模型验证。

3.寄存器传输模型验证一般使用verilog/vhdl语言实现,具体包括ip级别和soc级别的验证。ip级别的寄存器传输模型验证通常采用uvm(universal verification methodology)实现。在实现过程中,需要验证工程师基于uvm编写针对不同测试场景的测试用例。soc级别的寄存器传输模型验证可以采用uvm或systemc实现。在采用uvm实现的过程中,需要验证工程师基于uvm编写针对不同测试场景的测试用例。在采用systemc的实现过程中,需要验证工程师基于systemc编写针对不同测试场景的测试用例。

4.硬件模型验证包括模拟模型(emu)验证和芯片(silicon)验证。emu验证和silicon的验证通常采用c++实现。在实现过程中,需要验证工程师基于c++编写针对不同的测试场景的测试用例。

5.由于现代芯片规模越来越大并且功能越来越复杂,在芯片设计阶段,为了全面验证功能正确性,验证工程师通常需要针对不同的应用场景开发用于rtl验证模型(ip级别或soc级别)的测试用例。在芯片流片后,为了发现生产过程中工艺等原因引发的制造缺陷,验证工程师通常需要在芯片诊断测试阶段针对不同的芯片功能开发用于硬件验证模型(emu或silicon)的测试用例。由于针对不同验证模型平台的测试用例相互并不能复用,因此芯片验证工程师往往需要分别在ip/soc/emu/silicon等验证平台上重复开发大量的测试用例,从而导致芯片验证的工作效率较低。

6.因此,需要提出一种能够跨平台使用的芯片验证方法,以便提高芯片验证的工作效率。

技术实现要素:

7.本技术提供一种于ai推理芯片的芯片验证方法、芯片验证装置、电子设备、计算机可读存储介质和计算机程序产品。

8.根据本技术的一方面,提供了一种用于ai推理芯片的芯片验证方法,该方法包括:获取测试用例数据包,测试用例数据包包括结构索引数据和预定条数的层数据,层数据包括寄存器配置数据、推理数据、训练权重数据和操作指令数据;从测试用例数据包中提取结构索引数据,结构索引数据包括寄存器配置数据、推理数据、训练权重数据和操作指令数据的地址信息;解析测试用例数据包,获得层数据中的寄存器配置数据、推理数据、训练权重数据以及操作指令数据;

根据层数据中的寄存器配置数据、推理数据、训练权重数据以及操作指令数据控制ai推理芯片的ai加速引擎执行操作指令,其中寄存器配置数据用于配置ai加速引擎的寄存器,推理数据用于ai加速引擎的输入,训练权重数据用于配置运行在ai推理芯片的ai加速引擎上的神经网络;将ai加速引擎的执行结果与参考结果数据进行比较,获得验证结果。

9.根据本技术一实施例,测试用例数据包还包括参考结果数据。

10.根据本技术一实施例,推理数据包括图像数据、音频数据或视频数据。

11.根据本技术一实施例,层数据的条数对应于运行在ai推理芯片的ai加速引擎的神经网络的层数。

12.根据本技术一实施例,操作指令数据采用预定长度的编码格式,包括指令类型字段,用于指示操作指令的类型,指令类型包括寄存器配置指令、发送中断指令、接收中断指令以及读取寄存器指令。

13.根据本技术一实施例,操作指令数据还包括至少一个指令参数字段,用于提供操作指令的指令参数。

14.根据本技术一实施例,芯片验证方法用于ip级别或soc级别的rtl模型验证。

15.根据本技术一实施例,根据层数据中的寄存器配置数据、推理数据、训练权重数据以及操作指令数据控制ai推理芯片的ai加速引擎执行操作指令的步骤包括:将寄存器配置数据、推理数据、训练权重数据和操作指令数据导入system verilog测试平台;将训练权重数据和推理数据写入rtl模型的内存中;根据操作指令数据和uvm虚拟序列,向rtl模型实现的ai加速引擎加载激励。

16.根据本技术一实施例,uvm虚拟序列用于根据操作指令调用对应于配置寄存器指令的uvm序列、对应于发送中断指令的uvm序列、对应于接收中断指令的uvm序列、和/或对应于读取寄存器指令的uvm序列。

17.根据本技术一实施例,芯片验证方法用于硬件模型验证,硬件模型验证是emu验证或silicon验证。

18.根据本技术一实施例,根据层数据中的寄存器配置数据、推理数据、训练权重数据以及操作指令数据控制ai推理芯片的ai加速引擎执行操作指令的步骤包括:将结构索引数据、寄存器配置数据、训练权重数据、推理数据和操作指令数据写入硬件内存中;mcu固件根据操作指令数据调用相应的指令函数,将激励加载到ai加速引擎。

19.根据本技术一实施例,指令函数包括对应于配置寄存器指令的指令函数、对应于接收中断指令的指令函数、和/或对应于读取寄存器指令的指令函数。

20.根据本技术的一方面,提供了一种用于ai推理芯片的芯片验证装置,该装置包括:获取模块,用于获取测试用例数据包,测试用例数据包包括结构索引数据和预定条数的层数据,层数据包括寄存器配置数据、推理数据、训练权重数据和操作指令数据;提取模块,用于从测试用例数据包中提取结构索引数据,结构索引数据包括寄存器配置数据、推理数据、训练权重数据和操作指令数据的地址信息;解析模块,用于解析测试用例数据包,获得层数据中的寄存器配置数据、推理数

据、训练权重数据以及操作指令数据;控制模块,用于根据层数据中的寄存器配置数据、推理数据、训练权重数据以及操作指令数据控制ai推理芯片的ai加速引擎执行操作指令,其中寄存器配置数据用于配置ai加速引擎的寄存器,推理数据用于ai加速引擎的输入,训练权重数据用于配置运行在ai推理芯片的ai加速引擎上的神经网络;比较模块,用于将ai加速引擎的执行结果与参考结果数据进行比较,获得验证结果。

21.根据本技术一实施例,测试用例数据包还包括参考结果数据。

22.根据本技术一实施例,推理数据包括图像数据、音频数据或视频数据。

23.根据本技术一实施例,层数据的条数对应于运行在ai推理芯片的ai加速引擎的神经网络的层数。

24.根据本技术一实施例,操作指令数据采用预定长度的编码格式,包括指令类型字段,用于指示操作指令的类型,指令类型包括寄存器配置指令、发送中断指令、接收中断指令以及读取寄存器指令。

25.根据本技术一实施例,操作指令数据还包括至少一个指令参数字段,用于提供操作指令的指令参数。

26.根据本技术一实施例,芯片验证装置用于ip级别或soc级别的rtl模型验证。

27.根据本技术一实施例,控制模块包括:导入模块,用于将寄存器配置数据、推理数据、训练权重数据和操作指令数据导入system verilog测试平台;第一写入模块,用于将训练权重数据和推理数据写入rtl模型的内存中;第一激励加载模块,用于根据操作指令数据和uvm虚拟序列,向rtl模型实现的ai加速引擎加载激励。

28.根据本技术一实施例,uvm虚拟序列用于根据操作指令调用对应于配置寄存器指令的uvm序列、对应于发送中断指令的uvm序列、对应于接收中断指令的uvm序列、和/或对应于读取寄存器指令的uvm序列。

29.根据本技术一实施例,芯片验证装置用于硬件模型验证,硬件模型验证是emu验证或silicon验证。

30.根据本技术一实施例,控制模块包括:第二写入模块,用于将结构索引数据、寄存器配置数据、训练权重数据、推理数据和操作指令数据写入硬件内存中;第二激励加载模块,用于根据操作指令数据调用相应的指令函数,将激励加载到ai加速引擎。

31.根据本技术一实施例,指令函数包括对应于配置寄存器指令的指令函数、对应于接收中断指令的指令函数、和/或对应于读取寄存器指令的指令函数。

32.根据本技术的一方面,提供了一种电子设备,包括:处理器和存储器,存储器上存储有计算机程序,当计算机程序被处理器执行时,使处理器执行以上描述的芯片验证方法。

33.根据本技术的一方面,提供了一种计算机可读存储介质,其上存储有计算机程序,计算机程序被处理器执行时,使处理器执行以上描述的芯片验证方法。

34.根据本技术的一方面,提供了一种计算机程序产品,包括计算机程序,该计算机程序被处理器执行时,使处理器执行以上描述的芯片验证方法。

35.由于本技术的芯片验证方法中使用的测试用例数据包包括了ai推理芯片的验证所需的数据,并且这些数据与验证模型无关,因此本技术的芯片验证方法具有通用性,既可以实现rtl模型验证(ip级别或soc级别),也可以实现硬件模型(emu或silicon)验证。验证工程师只需根据不同的应用场景开发出各种测试用例数据包,就可以在不同模型验证平台上实现芯片验证,从而大幅提高了芯片验证的工作效率。

附图说明

36.附图用来提供对本技术技术方案的进一步理解,并且构成说明书的一部分,与本技术的实施例一起用于解释本技术的技术方案,但并不构成对本技术技术方案的限制。

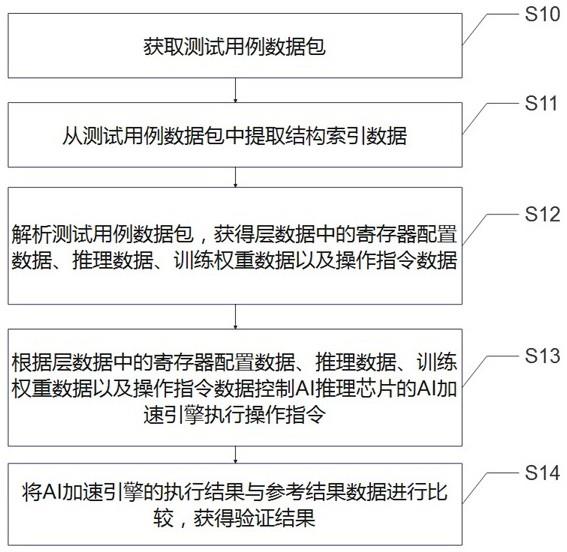

37.图1是图示出根据示例性实施例的用于ai推理芯片的芯片验证方法的流程图;图2是图示出根据示例性实施例的ai推理芯片的测试用例数据包的结构示意图;图3是图示出根据示例性实施例的微控制单元的操作指令的编码结构的示意图;图4是图示出根据示例性实施例的ip/soc验证平台的示意图;图5是图示出根据示例性实施例的emu/silicon验证平台的示意图;图6是图示出根据另一示例性实施例的用于ai推理芯片的芯片验证方法的流程图;图7是图示出根据示例性实施例的用于ai推理芯片的芯片验证装置的结构框图。

具体实施方式

38.在本技术中,除非另有说明,否则使用术语“第一”、“第二”等来描述各种要素不意图限定这些要素的位置关系、时序关系或重要性关系,这种术语只是用于将一个元件与另一元件区分开。在一些示例中,第一要素和第二要素可以指向该要素的同一实例,而在某些情况下,基于上下文的描述,它们也可以指代不同实例。

39.在本技术中对各种示例的描述中所使用的术语只是为了描述特定示例的目的,而并非旨在进行限制。除非上下文另外明确地表明,如果不特意限定要素的数量,则该要素可以是一个也可以是多个。如本文使用的,术语“多个”意指两个或更多,并且术语“基于”应解释为“至少部分地基于”。此外,术语“和/或”以及

“……

中的至少一个”涵盖所列出的项目中的任何一个以及全部可能的组合方式。

40.在芯片设计阶段,验证工程师需要针对rtl模型(ip级别或soc级别)验证开发测试用例。在芯片流片后,验证工程师还需要针对硬件模型(emu或silicon)验证开发相应的测试用例。由于针对rtl模型验证和硬件模型验证的测试用例相互并不能复用,因此芯片验证工程师往往需要分别针对rtl模型验证和硬件模型验证重复开发大量的测试用例,从而导致芯片验证的工作效率较低。

41.基于此,本技术提出一种芯片验证方法,其能够解析通用的测试用例数据包,并从测试用例数据包中获得rtl模型验证和硬件模型验证都需要的寄存器配置数据、推理数据、训练权重数据以及操作指令数据。验证工程师只需开发一套测试用例就可以实现rtl模型验证和硬件模型验证,从而使芯片验证的工作效率大幅提高。

42.下面结合附图详细描述本技术的示例性实施例。

43.图1是图示出根据示例性实施例的用于ai推理芯片的芯片验证方法的流程图。如图1所示,用于ai推理芯片的芯片验证方法,包括:步骤s10:获取测试用例数据包,测试用例数据包包括结构索引数据和预定条数的层数据,层数据包括寄存器配置数据、推理数据、训练权重数据和操作指令数据;步骤s11:从测试用例数据包中提取结构索引数据;步骤s12:解析测试用例数据包,获得层数据中的寄存器配置数据、推理数据、训练权重数据和操作指令数据;步骤s13:根据层数据中的寄存器配置数据、推理数据、训练权重数据以及操作指令数据控制ai推理芯片的ai加速引擎执行操作指令,其中寄存器配置数据用于配置ai加速引擎的寄存器,推理数据用于ai加速引擎的输入,训练权重数据用于配置运行在ai推理芯片的ai加速引擎上的神经网络;步骤s14:将ai加速引擎的执行结果与参考结果数据进行比较,获得验证结果。

44.根据本实施例的用于ai推理芯片的芯片验证方法既可以用于rtl模型验证,也可以用于硬件模型验证。rtl模型验证可以是ip级别或soc级别的rtl模型验证。硬件模型验证可以是emu验证或silicon验证。

45.在步骤s10中,获取测试用例数据包。测试用例数据包是芯片验证工程师根据需要验证的设计功能开发的。这些测试用例数据包具有通用性,可以应用在不同模型的验证测试中。

46.在步骤s11中,从测试用例数据包中提取结构索引数据。结构索引数据包括寄存器配置数据、推理数据、训练权重数据和操作指令数据的地址信息。可以根据结构索引数据的预设位置,从测试用例数据包中提取出结构索引数据。提取出的结构索引数据可以写入内存,供后续使用。

47.在步骤s12中,解析测试用例数据包,获得层数据中的寄存器配置数据、推理数据、训练权重数据以及操作指令数据。结构索引数据中包括寄存器配置数据、推理数据、训练权重数据以及操作指令数据分别在内存中的起始地址和长度信息,因此从测试用例数据包中提取出相应的数据,然后再将这些数据写入内存供后续使用。由于测试用例数据包中可能包括多条层数据,因此可以依次读取各条层数据,分别获得各条层数据中的寄存器配置数据、推理数据、训练权重数据以及操作指令数据并将其写入内存。

48.无论对于rtl模型(ip级别或soc级别)验证还是硬件模型(emu或silicon)验证,寄存器配置数据、推理数据、训练权重数据以及操作指令数据都是完成芯片验证所需要的数据。因此,通过步骤s12从测试用例数据包中获得的这些数据既可以用于rtl模型(ip级别或soc级别)验证,也可以用于硬件模型(emu或silicon)验证。

49.在步骤s13中,根据层数据中的寄存器配置数据、推理数据、训练权重数据以及操作指令数据控制ai推理芯片的ai加速引擎执行操作指令。寄存器配置数据用于配置ai加速引擎的寄存器。推理数据是需要ai加速引擎处理的数据,用于ai加速引擎的输入。推理数据例如包括图像数据、音频数据或视频数据等。训练权重数据用于配置运行在ai推理芯片的ai加速引擎上的神经网络。后续将结合不同的模型验证平台,详细描述步骤s13的执行过程。

50.在步骤s14中,将ai加速引擎的执行结果与参考结果数据进行比较,获得验证结果。若ai加速引擎的执行结果与参考结果相同,则验证通过。反之,若ai加速引擎的执行结果与参考结果不同,则验证未通过,需要后续找出错误的来源。在一些实施例中,参考结果数据可以包括在测试用例数据包中,在步骤s12中可以从测试用例数据包中提取出参考结果数据。在另一些实施例中,参考结果数据也可以单独提供,不必包括在测试用例数据包中。

51.图1示出的芯片验证方法够解析测试用例数据包,并从测试用例数据包中获得rtl模型验证和硬件模型验证都需要的寄存器配置数据、推理数据、训练权重数据以及操作指令数据。验证工程师只需开发一套测试用例就可以实现rtl模型验证和硬件模型验证,从而使芯片验证的工作效率大幅提高。

52.图2是图示出根据示例性实施例的ai推理芯片的测试用例数据包的结构示意图。如图2所示,测试用例数据包包括结构索引数据和预定条数的层数据。在本实施例中,层数据共有六条:layer 0至layer 5。在其他实施例中,层数据的条数可以是预先设定的,对应于运行在ai推理芯片的ai加速引擎上的神经网络的层数。

53.层数据(例如layer 2)中具体包括寄存器配置数据、推理数据、训练权重数据、操作指令数据以及可选的参考结果数据。寄存器配置数据用于配置ai推理芯片的寄存器。推理数据用于ai推理芯片的ai加速引擎的输入,例如包括图像数据、音频数据或视频数据等需要ai加速引擎处理的数据。训练权重数据用于配置运行在ai推理芯片的ai加速引擎上的神经网络。操作指令数据包括向ai加速引擎发送的操作指令,用于控制ai加速引擎;参考结果数据,用于验证测试结果。应当理解,参考结果数据也可以独立于测试用例数据包而提供,不必包括在测试用例数据包中。图2中仅示例性示出了层数据layer 2中的数据内容,应当理解的是,其他层数据也包括与层数据layer 2中相同类型的数据。

54.结构索引数据包括测试用例数据包中数据的组织结构信息,例如数据包中数据的树状结构信息。具体地,结构索引数据包可以包括结构索引数据的起始地址和长度、层数据的条数,每条层数据的起始地址和长度,每条层数据中包括的寄存器配置数据、推理数据、训练权重数据、操作指令数据、参考结果数据的各自的起始地址和长度等信息。结构索引数据在测试用例数据包中的位置可以是预先设定的。当测试用例数据包的解析器收到一个测试用例数据包时,可以从预订位置提取出结构索引数据,然后再从测试用例数据包中提取出各条层数据以及各条层数中的寄存器配置数据、推理数据、训练权重数据、操作指令数据和参考结果数据。

55.在一种实施例中,操作指令具体包括寄存器配置指令、发送中断指令、接收中断指令以及读取寄存器指令,用于使ai推理芯片中的微控制单元(mcu)控制ai加速引擎进行数据处理。操作指令数据可以采用预定长度的编码格式,包括指令类型字段,用于指示操作指令的类型。操作指令数据还可以包括至少一个指令参数字段,用于提供相应操作指令的指令参数。

56.图3是图示出根据示例性实施例的微控制单元的操作指令的编码结构的示意图。在本实施例中,操作指令数据采用固定的128比特进行编码。在图3中,csr cfg指令和csr en指令均表示寄存器配置指令,其中csr cfg指令用于配置某个寄存器地址所对应的寄存器的完整值,而csr en指令用于配置某个寄存器地址中的某一比特。send指令、recv指令和

poll指令分别表示发送中断指令、接收中断指令以及读取寄存器指令。

57.在图3中示出的以固定的128比特编码的操作指令数据中,指令类型字段位于第127至120比特(共8比特)。指令类型字段的值0、1、2、3、4分别表示csr cfg指令、csr en指令、send指令、recv指令以及poll指令。在图2中示出的以固定的128比特编码的操作指令数据中还包括参数字段。例如,在csr cfg指令中,第119至64比特为保留字段,第63至32比特为寄存器地址字段,第31至0比特为寄存器值字段。在csr en指令中,119至41比特为保留字段,第40比特为比特值字段,第39至32比特为比特域字段,第31至0比特为寄存器地址字段。在send指令中,第119至32比特为保留字段,第31至24比特为目的id字段,第23至16比特为源的id字段,第15至0比特为中断信息id字段。在recv指令中,第119至112比特为中断编号字段,第111至104比特为目的id字段,第103至96比特为源id字段,第95至64比特为寄存器访问方式字段,第63至32为寄存器地址字段,第31至0比特为寄存器值字段。在poll指令中,第119至72为保留字段,第71至64比特为读取次数字段,第63至32比特为寄存器地址字段,第31至0为期望值字段。保留字段可以使操作指令的编码格式具有扩展性。例如,当ai推理芯片具有多个mcu时,可以在保留字段中指示mcu的编号。通过使用以上参数字段可以为操作指令提供参数,以便完成相应操作指令的执行。

58.由于根据本技术实施例的测试用例数据包包括了ai推理芯片的验证所需的数据,并且这些数据与验证模型无关,因此这些测试用例数据包具有通用性,既可以在rtl模型验证(ip级别或soc级别)中使用,也可以在硬件模型(emu或silicon)模型验证中使用。验证工程师只需根据不同的应用场景开发出各种测试用例数据包,就可以实现在不同模型验证平台上实现芯片验证,而不再需要针对不同的模型验证平台定制开发相应的测试用例。

59.图4是图示出根据示例性实施例的ip/soc验证平台的示意图。该验证平台用于执行rtl模型验证。如图4所示,ip/soc验证平台包括模拟mcu行为的vip组件、待测ai加速引擎(由rtl模型实现)以及rtl模型内存(ddr或ddr vip)。使用测试用例数据包在图4示出的验证平台进行rtl模型验证时,需要预先为每一种mcu的操作指令编写对应的uvm序列(uvm sequence)。例如,与寄存器配置指令对应的uvm序列编码为00,该uvm序列有两个成员变量,分别是寄存器地址和寄存器值。与读取寄存器指令对应的uvm序列编码为04,该uvm序列有三个成员变量,分别是寄存器地址、期望值和尝试读寄存器次数。与接收中断指令的uvm序列编码为03,该uvm序列有六个成员变量,分别是中断编号、接收中断mcu、发送中断的ai引擎、接收中断后是否读写寄存器、寄存器地址和寄存器值。uvm序列可以加载到vip sequencer上以执行相应的操作指令。

60.在进行rtl模型验证过程中,在执行图1中示出方法的步骤s12时,需要使用预先编写的解析函数(例如使用c语言编写),对测试用例数据包进行解析,提取出各条层数据中的寄存器配置数据、推理数据、训练权重数据以及操作指令数据。

61.在进行rtl模型验证过程中,当执行图1中示出的步骤s13时,具体执行以下操作:将寄存器配置数据、推理数据、训练权重数据和操作指令数据通过例如dpi接口导入system verilog测试平台;将训练权重数据和推理数据写入rtl模型的内存中(例如通过前门或后门);根据操作指令数据和uvm虚拟序列,向rtl模型实现的ai加速引擎加载激励。uvm虚拟序列用于调用与操作指令对应的uvm序列,例如对应于配置寄存器指令的uvm序列、对应

于发送中断指令的uvm序列、对应于接收中断指令的uvm序列、和/或对应于读取寄存器指令的uvm序列。

62.图5是图示出根据示例性实施例的emu/silicon验证平台的示意图。该验证平台用于实现ai推理芯片的硬件验证。如图5所示,emu/silicon验证平台包括驱动程序和硬件soc。硬件soc中包括pcie接口、mcu、待测ai加速引擎和ddr内存。使用测试用例数据包在图5示出的验证平台进行硬件模型验证时,需要预先在mcu固件中为每一种mcu的操作指令编写对应的指令函数。例如,与寄存器配置指令对应的指令函数编码为00,该指令函数有两个成员变量,分别是寄存器地址和寄存器值。与读取寄存器指令对应的指令函数编码为04,该指令函数有三个成员变量,分别是寄存器地址、期望值和尝试读寄存器次数。与接收中断指令的指令函数编码为03,该指令函数有六个成员变量,分别是中断编号、接收中断mcu、发送中断的ai引擎、接收中断后是否读写寄存器、寄存器地址和寄存器值。mcu固件可以通过执行指令函数来执行对应的操作指令。

63.在进行硬件(emu/silicon)模型验证过程中,在执行步骤s12时,需要使用预先在ai推理芯片的驱动程序中编写的解析函数,对测试用例数据包进行解析,提取出层数据中的寄存器配置数据、推理数据、训练权重数据以及操作指令数据。

64.在进行硬件(emu/silicon)模型验证过程中,当执行步骤s13时,具体执行以下操作:将结构索引数据、寄存器配置数据、训练权重数据、推理数据和操作指令数据写入硬件内存中,同时可以将结构索引数据写入硬件内存并将内存指针赋予mcu;mcu固件根据操作指令数据调用相应的指令函数,将激励加载到ai加速引擎。具体地,mcu固件可以通过解析结构索引数据得到寄存器配置数据、训练权重数据、推理数据和操作指令数据的内存地址,读取操作指令逐条解析,然后调用相应的操作指令的指令函数,将激励加载到ai引擎。

65.图6是图示出根据另一示例性实施例的用于ai推理芯片的芯片验证方法的流程图。该验证方法既可以用于rtl模型(ip级别或soc级别)验证也可以硬件模型(emu或silicon)验证。

66.在步骤60中,从预先获得的测试用例数据包中提取出结构索引数据,并将结构索引数据写入内存。通过解析结构索引数据,可以获得测试用例数据包中的数据结构。

67.在步骤61中,判断当前处理的层是否为合法层。事实上,在解析测试用例数据包的过程中,需要逐层从各条层数据中提取数据。在提取完一层的层数据之后,若下一层存在,则下一层为合法层,需要继续提取下一层的层数据;若下一层不存在(即已经处理完所有层的层数据),则下一层为非法层,此时不再需要提取层数据,跳转至步骤s63。

68.在步骤62中,根据解析结构索引数据解析测试用例数据包,从层数据中提取出寄存器配置数据、推理数据、训练权重数据以及操作指令数据,并将这些数据写入内存。通过循环执行步骤61和步骤62,可以将测试用例数据包中所有层中的寄存器配置数据、推理数据、训练权重数据以及操作指令数据提取出来并写入内存,然后退出循环并进入步骤63。

69.在步骤63中,存储在内存中的结构索引数据的指针被赋给vip(在rtl模型验证中)或mcu(在硬件模型验证中),vip或mcu进而可以通过结构索引数据的指针读取出结构索引数据。

70.在步骤64中,为了逐层执行各层中的操作指令,需要首先判断当前层是否为合法层。当处理完一层的操作指令之后,若下一层存在,则下一层为合法层,需要继续执行下一层的操作指令;若下一层不存在(即已经执行完所有层的操作指令),则下一层为非法层,此时各层的操作指令已执行完毕,直接跳转到步骤s69。

71.在步骤65中,vip或mcu可以根据结构索引数据获得操作指令数据的指针,然后根据操作指令数据的指针从内存中获得操作指令数据。针对rtl模型验证,uvm虚拟序列根据操作指令调用对应于配置寄存器指令的uvm序列、对应于发送中断指令的uvm序列、对应于接收中断指令的uvm序列、和/或对应于读取寄存器指令的uvm序列;针对硬件模型验证,将操作指令翻译成指令序列,指令序列包括要调用的一个或多个mcu固件中的指令函数。

72.在步骤66中,判断是否需要进行寄存器配置。若操作指令是寄存器配置指令,则需要进行寄存器配置,在这种情况下,首先执行步骤67读取寄存器配置数据,然后执行步骤68执行寄存器配置指令;若操作指令数据中不包括寄存器配置指令,则不需要进行寄存器配置,直接执行步骤68。

73.在步骤67中,vip或mcu需要从内存中读取寄存器配置数据。

74.在步骤68中,vip或mcu根据uvm虚拟序列或指令序列,向ai加速引擎发送操作指令。

75.通过循环执行步骤64至步骤68,可以将测试用例数据包中所有层中的操作指令依次执行完成,ai加速引擎因此完成了神经网络模型中各层的操作,从而可以获得ai加速引擎的执行结果并跳转至步骤69。

76.在步骤69中,将ai加速引擎的执行结果与参考结果数据进行比较,若ai加速引擎的执行结果与参考结果相同,则验证通过。反之,若ai加速引擎的执行结果与参考结果不同,则验证未通过,需要后续找出错误的来源。在一种实施例中,参考结果数据可以包括在测试用例数据包中。在其他实施例中,参考结果数据也可以单独提供,不必包括在测试用例数据包中。

77.通过本技术实施例的芯片验证方法,在芯片设计阶段,可以针对所有的设计功能开发测试用例,用于芯片设计阶段的rtl模型验证。在芯片流片后,在芯片设计阶段开发的测试用例可以立即全部复用到硬件模型(emu或silicon)验证中,从而提高了芯片验证的工作效率。另外,在硬件模型(emu或silicon)验证中出现错误的测试用例也可以直接在rtl模型验证环境中复现出同样的错误现象,从而降低了测试用例的调试难度。可以采用控制变量法,通过在硬件模型验证中使用rtl模型验证中的相似测试用例,快速定位制造缺陷。

78.图7是图示出根据示例性实施例的用于ai推理芯片的芯片验证装置的结构框图。如图5所示,该芯片验证装置包括获取模块70,用于获取测试用例数据包,测试用例数据包包括结构索引数据和预定条数的层数据,层数据包括寄存器配置数据、推理数据、训练权重数据和操作指令数据;提取模块71,用于从测试用例数据包中提取结构索引数据,结构索引数据包括寄存器配置数据、推理数据、训练权重数据和操作指令数据的地址信息;解析模块72,用于解析测试用例数据包,获得层数据中的寄存器配置数据、推理数据、训练权重数据以及操作指令数据;控制模块73,用于根据层数据中的寄存器配置数据、推理数据、训练权重数据以及操作指令数据控制ai推理芯片的ai加速引擎执行操作指令,其中寄存器配置数据用于配置ai加速引擎的寄存器,推理数据用于ai加速引擎的输入,训练权重数据用于配

置运行在ai推理芯片的ai加速引擎上的神经网络;比较模块74,用于将ai加速引擎的执行结果与参考结果数据进行比较,获得验证结果。

79.应当理解,图7中所示芯片验证装置的各个模块可以与参考图1描述的芯片验证方法中的各个步骤相对应。由此,上面针对芯片验证方法描述的操作、特征和优点同样适用于芯片验证装置及其包括的模块,并且上面针对芯片验证方法描述的操作、特征和优点同样适用于芯片验证装置及其包括的模块。为了简洁起见,某些操作、特征和优点在此不再赘述。

80.根据一些实施例,芯片验证装置用于rtl模型验证。rtl模型验证是ip级别或soc级别的rtl模型验证。在这些实施例中,芯片验证装置中的控制模块73包括:导入模块,用于将寄存器配置数据、推理数据、训练权重数据和操作指令数据通过例如dpi接口导入system verilog测试平台;第一写入模块,用于将训练权重数据和推理数据写入rtl模型的内存中(例如通过前门或后门);第一激励加载模块,用于根据操作指令数据和uvm虚拟序列,向rtl模型实现的ai加速引擎加载激励。

81.根据一些实施例,芯片验证装置用于硬件模型验证。硬件模型验证是emu验证或silicon验证。在这些实施例中,芯片验证装置中的控制模块73包括:第二写入模块,用于将结构索引数据、寄存器配置数据、训练权重数据、推理数据和操作指令数据写入硬件内存中,同时还可以将结构索引数据写入硬件内存并将内存指针赋予mcu;第二激励加载模块,用于根据操作指令数据调用相应的指令函数,将激励加载到ai加速引擎。具体地第二加载模块可以通过解析结构索引数据得到寄存器配置数据、训练权重数据、推理数据和操作指令数据的内存地址,读取操作指令逐条解析,然后调用相应的操作指令的指令函数,将激励加载到ai引擎。第二写入模块可以在ai推理芯片的驱动程序中实现。第二激励加载模块可以在mcu的固件中实现。

82.虽然上面参考特定模块讨论了特定功能,但是应当注意,本文讨论的各个模块的功能可以分为多个模块,和/或多个模块的至少一些功能可以组合成单个模块。本文讨论的特定模块执行动作包括该特定模块本身执行该动作,或者替换地该特定模块调用或以其他方式访问执行该动作(或结合该特定模块一起执行该动作)的另一个组件或模块。因此,执行动作的特定模块可以包括执行动作的该特定模块本身和/或该特定模块调用或以其他方式访问的、执行动作的另一模块。

83.还应当理解,本技术可以在软件硬件元件或程序模块的一般上下文中描述各种技术。上面关于图7描述的各个模块可以在硬件中或在结合软件和/或固件的硬件中实现。例如,这些模块可以被实现为计算机程序代码/指令,该计算机程序代码/指令被配置为在一个或多个处理器中执行并存储在计算机可读存储介质中。可替换地,这些模块可以被实现为硬件逻辑/电路。

84.根据本技术的一方面,提供了一种电子设备,包括处理器和存储器,存储器上存储有计算机程序,当计算机程序被处理器执行时,使处理器执行上述任意一种芯片验证方法。应当理解,处理器和存储计算机程序的存储器既可以是独立的器件,也可以集成在一个器件中,本发明对此不作限制。

85.根据本技术的一方面,提供了一种计算机可读存储介质,其上存储有计算机程序,计算机程序被处理器执行时,使处理器执行上述任意一种芯片验证方法。计算机存储介质

可包括以用于存储例如计算机可读指令、数据结构、程序模块或其它数据的信息的任何方法或技术实现的易失性和非易失性、可移动和不可移动的介质。例如,计算机可读存储介质包括但不限于,易失性存储器,例如随机存储器(ram、dram、sram);以及非易失性存储器,例如闪存、各种只读存储器(rom、prom、eprom、eeprom)、磁性和铁磁/铁电存储器(mram、feram);以及磁性和光学存储设备(硬盘、磁带、cd、dvd);或其它已知的介质或今后开发的能够存储供计算机系统使用的计算机可读信息/数据。

86.根据本技术的一方面,提供了一种计算机程序产品,包括计算机程序,该计算机程序被处理器执行时,使处理器执行上述任意一种芯片验证方法。

87.虽然在附图和前面的描述中已经详细地说明和描述了本技术,但是这样的说明和描述应当被认为是说明性的和示意性的,而非限制性的;本技术不限于所公开的实施例。通过研究附图、公开内容和所附的权利要求书,本领域技术人员在实践所要求保护的主题时,能够理解和实现对于所公开的实施例的变型。在权利要求书中,词语“包括”不排除未列出的其他元件或步骤,不定冠词“一”或“一个”不排除多个,术语“多个”是指两个或两个以上。在相互不同的从属权利要求中记载了某些措施的仅有事实并不表明这些措施的组合不能用来获益。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1