FPGA芯片间数据传输方法、装置、系统及存储介质与流程

本发明涉及fpga及通信,尤指一种fpga芯片间数据传输方法、装置、系统及存储介质。

背景技术:

1、大规模天线技术(massive mimo)是5g nr(new radio)的关键技术之一。在massive mimo系统中,天线数通常可以达到64甚至更多,例如:128或256。随着天线数的增加,系统容量也成倍增加,另外系统实现的复杂度也随之增加,因此需要处理的数据量是非常巨大的,且对数据传输的速率和稳定度要求也较高。为了实现massive mimo系统,通常需要多片fpga(field programmable gate array,现场可编程门阵列)协同工作,因此数据在多片fpga之间如何稳定传输非常关键。

2、在多片fpga协同工作的系统中,pcie、serial rapidio(srio)和aurora64b/66b是其中数据传输常用的三种协议。其中pcie定义了物理层、数据链路层、事务层和软件层;srio定义了物理层、传输层和逻辑层;aurora64b/66b仅定义了链路层和物理层,相比pcie和srio,aurora64b/66b协议比较简单,开销更小,且链路数目和链路速率选择都比较灵活,因此aurora64b/66b是多片fpga间互联常用的协议之一。

3、以硬件设计架构基于xilinx fpga的系统为例,假设整个系统有5片fpga,其中1片fpga作为主片,主要实现eth mac、oran接口的功能,另外4片fpga作为从片,主要实现下行数据的发送和上行数据的接收,这样,oran接口从上层接收到的数据,以及需要oran接口上传到上层去的数据,都需要在一个主片和几个从片之间传输。

4、由于aurora64b/66b需要定期进行时钟补偿,因此数据的发送是不连续的,这就意味着aurora64b/66b的接收和发送时钟,与实际数据传输的并行时钟速率是不匹配的,因此需要对数据进行缓存的处理,当数据线速率较高,数据链路较多时,进行数据缓存处理需要消耗大量的bram(block ram)资源。因此,现有的主片和从片之间的传输方案数据开销较大,不适合高速率数据传输。

5、为了平衡数据开销以及速率和链路,目前亟待提出一种简单轻量级的fpga芯片间数据传输方法,用于多片fpga互联进行数据传输时,可以实现数据连续传输,提高数据的传输效率和可靠性,以解决现有技术中因数据开销较大而不适合高速率数据传输的问题。

技术实现思路

1、有鉴于此,本发明实施例提供一种fpga芯片间数据传输方法、装置、系统及存储介质,本发明提供的技术方案通过在主fpga芯片与从fpga芯片之间建立数据链路,然后主fpga芯片与从fpga芯片基于该数据链路传输数据,由于该数据链路仅传输数据信息而不传输控制信息,因此提高了数据的传输效率;另外,通过在发送数据时将用户数据从用户时钟域跨到传输时钟域,在接收时再将所接收的数据从传输时钟域跨到用户时钟域,这样能保持数据在传输前后都在用户时钟域中,不需要再做额外的处理,数据开销小,从而实现了数据连续传输,进一步提高了数据传输速率;在多数据链路时,通过在发送端或接收端设置同步缓存器,可使每条数据链路的数据对齐,从而提高了数据的可靠性,解决了现有技术中因数据开销较大而不适合高速率数据传输的问题。经过测试在常温下长跑无误码,高低温下长跑误码率很低。

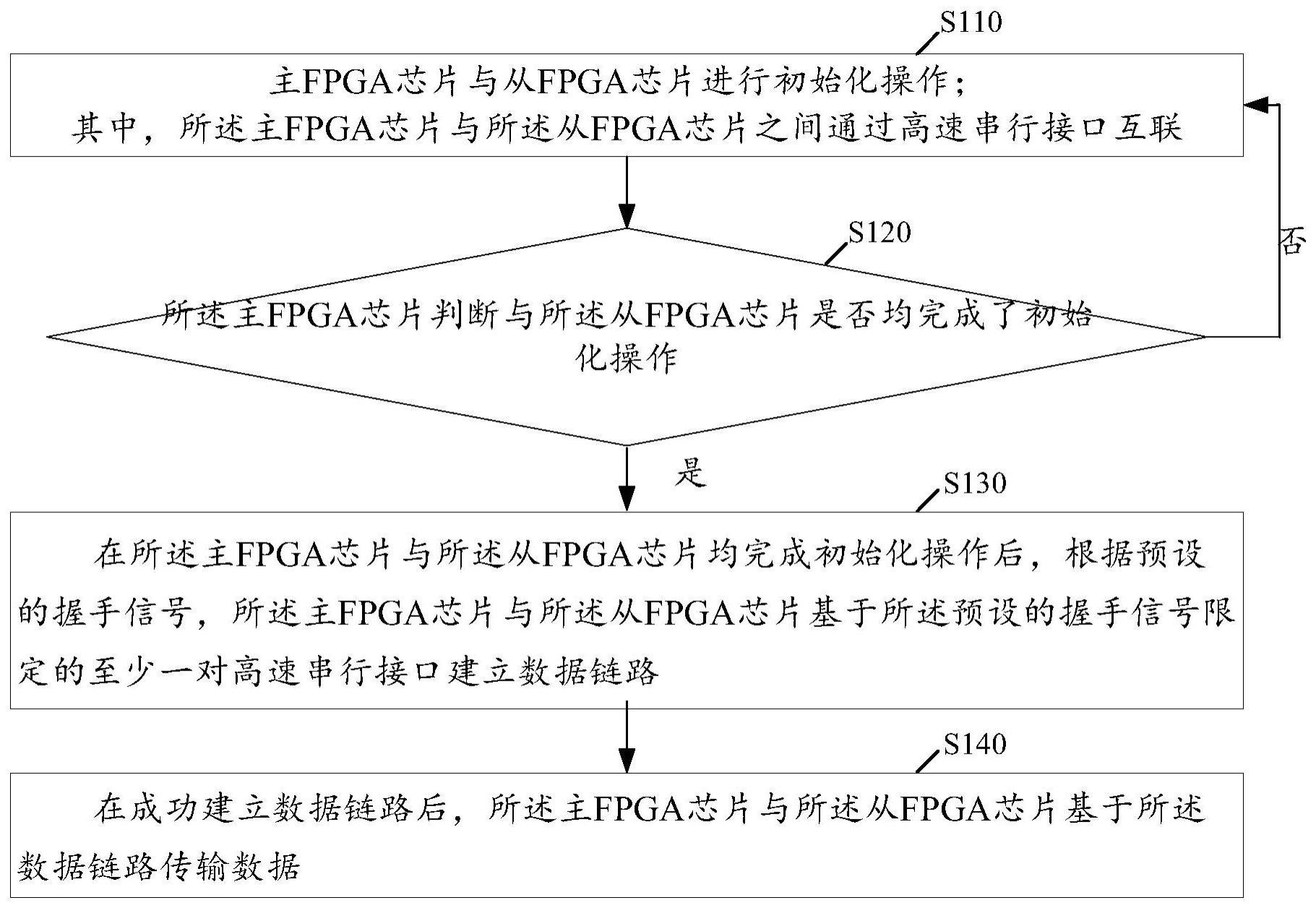

2、第一方面,本发明实施例提供了一种数据传输方法,所述方法包括:

3、主fpga芯片与从fpga芯片进行初始化操作;其中,所述主fpga芯片与所述从fpga芯片之间通过高速串行接口互联;

4、所述主fpga芯片判断与所述从fpga芯片是否均完成了初始化操作;

5、在所述主fpga芯片与所述从fpga芯片均完成初始化操作后,根据预设的握手信号,所述主fpga芯片与所述从fpga芯片基于所述预设的握手信号限定的至少一对高速串行接口建立数据链路;

6、在成功建立数据链路后,所述主fpga芯片与所述从fpga芯片基于所述数据链路传输数据。

7、优选地,其中,所述主fpga芯片和所述从fpga芯片包括高速串行收发器模块,所述进行初始化操作,具体包括:

8、将所述高速串行收发器模块中的时钟模块进行复位;

9、判断所述时钟模块是否锁定,在所述时钟模块锁定后对所述高速串行收发器模块中的数据发送模块和/或数据接收模块进行复位。

10、优选地,其中,通过如下方式判断所述主fpga芯片与所述从fpga芯片是否均完成初始化操作:

11、当所述主fpga芯片进行初始化操作时,向所述从fpga芯片发送主片初始化开始指示信号;

12、当所述从fpga芯片收到所述主片初始化开始指示信号后,判断本地是否完成初始化操作,若完成初始化操作,则向所述主fpga芯片回复从片初始化完成指示信号;

13、当所述主fpga芯片收到所述从片初始化完成指示信号后,判断本地是否完成初始化操作,若完成初始化操作,则向所述从fpga芯片发送主片初始化完成指示信号;

14、当所述从fpga芯片收到所述主片初始化完成指示信号后,则向所述主fpga芯片回复确认收到主片初始化完成指示信号;

15、当所述主fpga芯片收到所述确认收到主片初始化完成指示信号时,判断所述主fpga芯片与所述从fpga芯片均完成初始化操作。

16、优选地,所述根据预设的握手信号,所述主fpga芯片与所述从fpga芯片基于所述预设的握手信号限定的至少一对高速串行接口建立数据链路,具体包括:

17、所述主fpga芯片与所述从fpga芯片按照预设的握手步骤进行握手,当连续成功握手达到预设次数时,所述主fpga芯片与所述从fpga芯片在所述预设的握手信号传输的高速串行接口之间建立数据链路成功,当建立数据链路成功时,所述主fpga芯片向所述从fpga芯片发送建立数据链路成功指示信号;

18、其中,所述预设的握手信号包括预设的第一握手信号和预设的第二握手信号,所述握手步骤如下:

19、所述主fpga芯片向所述从fpga芯片发送所述预设的第一握手信号;

20、当所述从fpga芯片收到所述预设的第一握手信号后,则向所述主fpga芯片回复所述预设的第二握手信号;

21、当所述主fpga芯片收到所述从fpga芯片发送的所述预设的第二握手信号后,则成功握手一次。

22、优选地,当所述主fpga芯片与所述从fpga芯片基于所述预设的握手信号限定的多对高速串行接口建立多条数据链路时,所述方法还包括:

23、当所述主fpga芯片或所述从fpga芯片收到对方所发送的预设的握手信号时,记录下每条数据链路中收到所述预设的握手信号的时刻;

24、根据每条数据链路中收到所述预设的握手信号的时刻,确定每条数据链路的链路延时;

25、使用每条数据链路的链路延时配置每条数据链路的接收端同步缓存器,或者,将每条数据链路的链路延时发送给对方以使对方配置对应数据链路的发送端同步缓存器。

26、优选地,其中,所述主fpga芯片与所述从fpga芯片包括高速串行收发器ip核,所述主fpga芯片与所述从fpga芯片基于所述数据链路传输数据,具体包括:

27、当所述主fpga芯片或所述从fpga芯片基于所述数据链路将用户数据发送给对方时,执行如下操作:

28、对用户数据进行跨时钟处理,得到第一处理数据;

29、给所述第一处理数据添加数据同步头,得到第二处理数据;

30、对所述第二处理数据中除所述数据同步头之外的数据进行加扰操作,得到第三处理数据;其中,所述第三处理数据包括所述数据同步头和进行加扰操作后的数据;

31、将所述第三处理数据发送给所述高速串行收发器ip核,经由其处理后发送给对方;

32、当所述主fpga芯片或所述从fpga芯片基于所述数据链路接收到从对方发送过来的数据时,执行如下操作:

33、通过所述高速串行收发器ip核得到接收数据;

34、对所述接收数据进行解扰操作;

35、判断是否存在多数据链路,如果存在,则将解扰后的接收数据缓存到当前数据链路的接收端同步缓存器,再从所述当前数据链路的接收端同步缓存器中读取所述解扰后的接收数据,以使每条数据链路的数据同步;

36、对所述解扰后的接收数据进行跨时钟处理。

37、优选地,其中,所述主fpga芯片与所述从fpga芯片包括高速串行收发器ip核,所述主fpga芯片与所述从fpga芯片基于所述数据链路传输数据,具体包括:

38、当所述主fpga芯片或所述从fpga芯片基于所述数据链路将用户数据发送给对方时,执行如下操作:

39、对用户数据进行跨时钟处理,得到第一处理数据;

40、判断是否存在多数据链路,如果存在,则将所述第一处理数据缓存到当前数据链路的发送端同步缓存器,再从所述当前数据链路的发送端同步缓存器中读取所述第一处理数据,以使每条数据链路的数据同步;

41、给所述第一处理数据添加数据同步头,得到第二处理数据;

42、对所述第二处理数据中除所述数据同步头之外的数据进行加扰操作,得到第三处理数据;其中,所述第三处理数据包括所述数据同步头和进行加扰操作后的数据;

43、将所述第三处理数据发送给所述高速串行收发器ip核,经由其处理后发送给对方;

44、当所述主fpga芯片或所述从fpga芯片基于所述数据链路接收到从对方发送过来的数据时,执行如下操作:

45、通过所述高速串行收发器ip核得到接收数据;

46、对所述接收数据进行解扰操作;

47、对所述解扰后的接收数据进行跨时钟处理。

48、优选地,其中,

49、所述对用户数据进行跨时钟处理,具体包括:

50、将所述用户数据从用户时钟跨到传输时钟;

51、所述对所述解扰后的接收数据进行跨时钟处理,具体包括:

52、将所述解扰后的接收数据从传输时钟跨到用户时钟。

53、第二方面,本发明实施例提供了一种fpga芯片间数据传输装置,所述装置包括:

54、初始化模块,设置为主fpga芯片与从fpga芯片进行初始化操作;其中,所述主fpga芯片与所述从fpga芯片之间通过高速串行接口互联;

55、初始化完成判断模块,设置为所述主fpga芯片判断与所述从fpga芯片是否均完成了初始化操作;

56、建链模块,设置为在所述主fpga芯片与所述从fpga芯片均完成初始化操作后,根据预设的握手信号,所述主fpga芯片与所述从fpga芯片基于所述预设的握手信号限定的至少一对高速串行接口建立数据链路;

57、数据传输模块,设置为在成功建立数据链路后,所述主fpga芯片与所述从fpga芯片基于所述数据链路传输数据。

58、第三方面,本发明实施例提供了一种数据传输系统,包括:一个主fpga芯片和一个或多个从fpga芯片,其中,所述主fpga芯片与所述从fpga芯片之间通过高速串行接口互联;

59、所述主fpga芯片,被设置为进行初始化操作,并判断与所述从fpga芯片是否均完成了初始化操作,与所述从fpga芯片均完成初始化操作后,根据预设的握手信号,与所述从fpga芯片基于所述预设的握手信号限定的至少一对高速串行接口建立数据链路,在成功建立数据链路后,与所述从fpga芯片基于所述数据链路传输数据;

60、所述从fpga芯片,被设置为进行初始化操作,并与所述主fpga芯片均完成初始化操作后,根据预设的握手信号,与所述主fpga芯片基于所述预设的握手信号限定的至少一对高速串行接口建立数据链路,在成功建立数据链路后,与所述主fpga芯片基于所述数据链路传输数据。

61、第四方面,本发明实施例提供了一种存储介质,所述存储介质用于存储计算机程序,所述计算机程序用于实现第一方面所述的方法。

- 还没有人留言评论。精彩留言会获得点赞!