一种多CPU架构中置换CPU重启的装置的制作方法

一种多cpu架构中置换cpu重启的装置

技术领域

1.本实用新型涉及多cpu重启管理领域,尤其是涉及一种多cpu架构中置换cpu重启的装置。

背景技术:

2.目前相关intel的架构下,在多cpu(central processing unit,中央处理器)系统的架构下,设计时会先决定其中一个cpu为legacy socket(系统开机所在的cpu),也就是开机cpu,意旨如果是两cpu的系统,必须至少有一颗cpu安装legacy socket,系统才能正常开机,以此类推多cpu系统也必须遵守且符合此规定。

3.legacy socket cpu的dmi(direct media interface,直接媒体接口)讯号需连接到南桥(pch),导致于系统在运作时,在某些情况下发生cpu0(开机cpu)损毁,维护人员只能通过更换硬件设备的方式让系统重启,由于现在边缘运算服务器的放置地点,多数为比较偏远或难马上抵达的地方,维护人员无法马上到达且更换,假使legacy socket cpu0损坏时,系统可以自行通过其他cpu的方式来启动,并通过系统降级来延展系统的使用寿命,让维护人员抵达前,系统还可以提供一定的功能运作。

4.但是,目前现有技术中,系统与南桥通信,是通过dmi将legacy socket cpu0和南桥通信连接,所以现在2cpu或多cpu的系统架构下,一定要有安装legacy socket,cpu0才能开机,并跟南桥沟通,若没有安装legacy socket,则无法开机;而且系统开机状态下,legacy socket cpu0损坏时,只能透过更换硬件设备的方式才能解决并重启,不利于提高多cpu架构下应用可靠性。

技术实现要素:

5.本实用新型为了解决现有技术中存在的问题,创新提出了一种多cpu架构中置换cpu重启的装置,在legacy socket cpu0损坏时,使用第一控制模块进行切换模块切换,达到置换系统开机cpu的功能,提高了多cpu架构下应用可靠性。

6.本实用新型第一方面提供了一种多cpu架构中置换cpu重启的装置,包括:第一控制模块、切换模块、第一cpu、第二cpu、南桥芯片,所述第一控制模块的数据接收端与第一cpu的错误信号发送端通信连接,所述第一控制模块的切换控制输出端与切换模块的切换控制端通信连接,所述第一控制模块的重启控制输出端与第二cpu的重启控制端通信连接,用于在第一cpu故障情况下将南桥芯片切换为与第二cpu通信,所述切换模块的第一数据通信端与第一cpu的数据通信端通信连接,所述切换模块的第二数据通信端与第二cpu的数据通信端通信连接,所述切换模块的第三数据通信端与南桥芯片的数据通信端通信连接,其中,第一cpu为系统开机cpu,第二cpu为除系统开机cpu以外的其他cpu。

7.可选地,还包括第二控制模块,所述第二控制模块与第一控制模块通信连接。

8.进一步地,所述第二控制模块为基板管理控制器。

9.可选地,第二cpu的重启控制端为第二cpu的功能配置引脚,第一控制模块的重启

控制输出端与第二cpu的功能配置引脚通信连接。

10.进一步地,第一控制模块的开机调节控制输出端与第一cpu的功能配置引脚通信连接。

11.可选地,切换模块为多路选择器。

12.可选地,第一控制模块为可编程逻辑控制器件。

13.进一步地,第一控制模块与第二控制模块通过i2c通信连接。

14.可选地,第一cpu的数据通信端、第二cpu的数据通信端、南桥芯片的数据通信端均为dmi接口。

15.本实用新型采用的技术方案包括以下技术效果:

16.本实用新型在legacy socket cpu0损坏时,使用第一控制模块进行切换模块切换,达到置换系统开机cpu的功能,提高了多cpu架构下应用可靠性。

17.本实用新型技术方案实现legacy socket cpu0损坏时,系统降级重启,对于运用在偏远维护困难的地区的多cpu架构有很重要的作用,便于争取工作人员进行系统维护的时间。

18.本实用新型技术方案还包括第二控制模块,可以便于管理者根据接收到的信息及时了解当前cpu运行情况,决定是否停用维护。

19.应当理解的是以上的一般描述以及后文的细节描述仅是示例性和解释性的,并不能限制本实用新型。

附图说明

20.为了更清楚说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单介绍,显而易见的,对于本领域普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

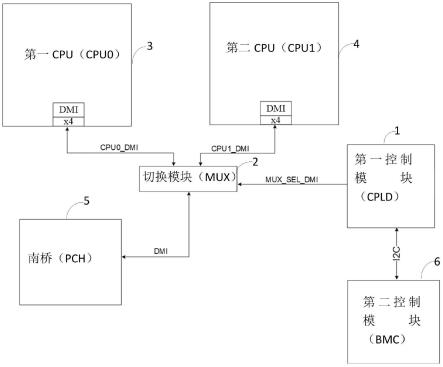

21.图1为本实用新型方案中实施例一装置的结构示意图;

22.图2为本实用新型方案中实施例一依照intel系统设计架构下,多cpu架构下legacy socket cpu以及其他cpu的引脚设置示意图;

23.图3为本实用新型方案中实施例一cpld、cpu0、cpu1通信的示意图。

具体实施方式

24.为能清楚说明本方案的技术特点,下面通过具体实施方式,并结合其附图,对本实用新型进行详细阐述。下文的公开提供了许多不同的实施例或例子用来实现本实用新型的不同结构。为了简化本实用新型的公开,下文中对特定例子的部件和设置进行描述。此外,本实用新型可以在不同例子中重复参考数字和/或字母。这种重复是为了简化和清楚的目的,其本身不指示所讨论各种实施例和/或设置之间的关系。应当注意,在附图中所图示的部件不一定按比例绘制。本实用新型省略了对公知组件和处理技术及工艺的描述以避免不必要地限制本实用新型。

25.实施例一

26.本实用新型实施例一为描述方便,采用两个cpu为例进行说明,但不限于两个cpu,也可以是其他数量的cpu,本实用新型在此不做限制。如图1所示,本实用新型提供了一种多

cpu架构中置换cpu重启的装置,包括:第一控制模块1、切换模块2、第一cpu3(cpu0)、第二cpu4(cpu1)、南桥芯片5,第一控制模块1的数据接收端与第一cpu3的错误信号发送端通信连接,第一控制模块1的切换控制输出端与切换模块2的切换控制端通信连接,第一控制模块1的重启控制输出端与第二cpu4的重启控制端通信连接,用于在第一cpu3故障情况下将南桥芯片5切换为与第二cpu4通信,切换模块2的第一数据通信端与第一cpu3的数据通信端通信连接,切换模块2的第二数据通信端与第二cpu4的数据通信端通信连接,切换模块2的第三数据通信端与南桥芯片5的数据通信端通信连接,其中,第一cpu3为系统开机cpu,即cpu0,第二cpu4为除系统开机cpu以外的其他cpu,即cpu1。

27.进一步地,还包括第二控制模块6,第二控制模块6与第一控制模块1通信连接。具体地,第二控制模块6为基板管理控制器。

28.进一步地,第二cpu4的重启控制端为第二cpu4的功能配置引脚(strap pin),第一控制模块1的重启控制输出端与第二cpu4的功能配置引脚通信连接。

29.具体地,第一控制模块1的开机调节控制输出端与第一cpu3的功能配置引脚(strap pin)通信连接。

30.系统开机cpu设计是依照intel系统设计说明书的架构下,调整strap pin脚位来设计legacy socket cpu,如图2所示。

31.legacy_skt、frmagent、dmimode_override和bmcinit来决定legacy socket cpu和其他cpu。

32.进一步地,如图3所示,第一控制模块1(cpld)在接收到第一cpu3(cpu0)的错误信号(cpu0_err)后,第一控制模块1(cpld)的开机调节控制输出端与第一cpu3的功能配置引脚(strap pin)通信连接,用于调整第一cpu3功能配置引脚(strap pin)的电平,使得第一cpu3不再是legacy socket cpu,即系统开机cpu,第一控制模块1(cpld)的重启控制输出端与第二cpu4的功能配置引脚(strap pin)通信连接,用于调整第二cpu4功能配置引脚(strap pin)的电平,使得第二cpu4替换第一cpu3,成为legacy socket cpu,即系统开机cpu,以达到系统降低重启的目的。即将第一cpu3(cpu0)的legacy_skt、frmagent、dmimode_override的引脚调整为低电平,将第二cpu4(cpu0)的legacy_skt、frmagent、dmimode_override的引脚调整为高电平。

33.具体地,切换模块2可以为多路选择器,即mux芯片。mux芯片的切换控制端(mux_sel_dmi)与第一控制模块1(cpld)的切换控制输出端通信连接,mux芯片的第一数据通信端(cpu0_dmi)与第一cpu3的数据通信端(dmi)通信连接,mux芯片的第二数据通信端(cpu1_dmi)与第二cpu4的数据通信端(dmi)通信连接,mux芯片的第三数据通信端(dmi)与南桥芯片5的数据通信端(dmi)通信连接,第一控制模块1可以为可编程逻辑控制器件,即cpld(complex programmable logic device,复杂可编程逻辑器件),第一控制模块1与第二控制模块6通过i2c通信连接。第一cpu3的数据通信端、第二cpu4的数据通信端、南桥芯片5的数据通信端均可以为dmi接口。

34.工作原理是:第一控制模块1(cpld)来控制各个cpu的strap pin准位,使得第二cpu4(即cpu1)取代第一cpu3(cpu0),置换成legacy socket cpu,strap pin准位需依照图2中的intel pdg设定,来区分cpu0和cpu1,当系统cpu0损坏时,第一控制模块1(cpld)接收cpu0发送错误讯号,控制cpu1的strap pin,切换成legacy socket cpu设定,这样系统的

legacy socket cpu就由cpu0变成了cpu1,同时cpld调整切换模块2(多路选择器mux芯片)把dmi切到cpu1接口,同时第二控制模块6(bmc)接收第一控制模块1(cpld)发送的cpu0错误讯号后,把系统关回s5状态(关闭状态),使系统去作降级重启使用。

35.本实用新型在legacy socket cpu0损坏时,使用第一控制模块进行切换模块切换,达到置换系统开机cpu的功能,提高了多cpu架构下应用可靠性。

36.本实用新型技术方案实现legacy socket cpu0损坏时,系统降级重启,对于运用在偏远维护困难的地区的多cpu架构有很重要的作用,便于争取工作人员进行系统维护的时间。

37.本实用新型技术方案还包括第二控制模块以及上位机,可以便于管理者根据接收到的信息及时了解当前cpu运行情况,决定是否停用维护。

38.上述虽然结合附图对本实用新型的具体实施方式进行了描述,但并非对本实用新型保护范围的限制,所属领域技术人员应该明白,在本实用新型的技术方案的基础上,本领域技术人员不需要付出创造性劳动即可做出的各种修改或变形仍在本实用新型的保护范围以内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1