一种高性能处理器智能核心板的制作方法

1.本实用新型涉及智能板技术领域,尤其涉及一种高性能处理器智能核心板。

背景技术:

2.核心板是将mini pc的核心功能打包封装的一块电子主板。大多数核心板集成了cpu,存储设备和引脚,通过引脚与配套底板连接在一起从而实现某个领域的系统芯片。人们也常常将这样一套系统称之为单片机,或者说是嵌入式开发平台。因为核心板集成了核心的通用功能,所以它具有一块核心板可以定制各种不同的底板的通用性,这大大提高了单片机的开发效率。因为核心板作为一块独立的模块分离出来,所以也降低了开发的难度,增加了系统的稳定性和可维护性。

3.传统的核心板在做底板开发时,会产生pcb布线困难、不同速率接口之间有串扰、方向错误时烧坏核心板等问题,会增加开发的难度和成本。

技术实现要素:

4.针对现有技术的不足,本实用新型提供了一种高性能处理器智能核心板,以解决了上述背景技术中提出的问题。

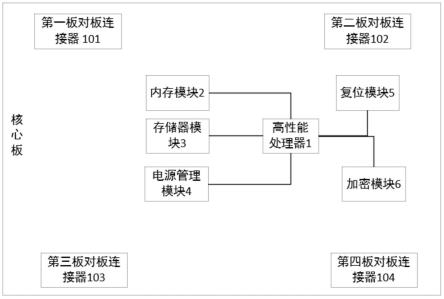

5.本实用新型提供了一种高性能处理器智能核心板,核心板包括高性能处理器(1)、内存模块(2)、存储器模块(3)、电源管理模块(4)、复位模块(5)、加密模块(6)和四个对称设置的板对板连接器;所述高性能处理器(1)分别与内存模块(2)、存储器模块(3)、电源管理模块(4)、复位模块(5)和加密模块(6)相连;所述板对板连接器和所述核心板的底板接口相连,所述板对板连接器的引脚按照预设方式设置排布;所述四个对称设置的板对板连接器分别位于核心板同一平面的四个端点处。

6.进一步的,所述高性能处理器(1)为renesas g2x处理器。

7.进一步的,所述四个对称设置的板对板连接器分为第一板对板连接器(101)、第二板对板连接器(102)、第三板对板连接器(103)和第四板对板连接器(104);

8.第一板对板连接器(101)具有若干audio接口、scif接口、hscif接口、ssi接口、gpio接口、sd卡接口、数据收发通信接口和i2c接口;所述若干audio接口、scif接口、hscif接口、gpio接口、sd卡接口、数据收发通信接口和i2c接口均与高性能处理器(1)电性连接;

9.第二板对板连接器(102)具有若干avb接口、显示接口、扩展总线接口、scif接口、can接口、iic接口和i2c接口;所述若干avb接口、显示接口、扩展总线接口、scif接口、can接口、iic接口和i2c接口均与高性能处理器(1)电性连接;

10.第三板对板连接器(103)具有若干jtag接口、usb接口、gpio接口和pcie接口;所述若干jtag接口、usb接口、gpio接口和pcie接口均与高性能处理器(1)电性连接;

11.第四板对板连接器(104)具有若干qspi接口、csi接口、gpio接口、hdmi接口和lvds接口;所述若干qspi接口、csi接口、hdmi接口和lvds接口均与高性能处理器(1)电性连接。

12.进一步的,第一板对板连接器(101)的第一引脚、第二引脚和第四引脚为audio接

口,第六引脚、第八引脚、第十引脚和第十二引脚为ssi接口,第六十一引脚、第六十二引脚、第七十七引脚、第七十八引脚、第七十九引脚和第八十引脚为i2c接口,第十三引脚、第十四引脚、第二十一引脚、第二十二引脚、第三十一引脚、第三十二引脚、第四十引脚、第四十七引脚、第四十八引脚、第五十六引脚、第六十三引脚和第六十四引脚接地。

13.进一步的,第二板对板连接器(102)的第一引脚、第二引脚、

……

、第十三引脚、第十五引脚、第十六引脚、第十七引脚和第十八引脚为avb接口,第六十九引脚、第七十引脚、第七十一引脚、第七十二引脚为can接口,第七十五引脚、第七十六引脚、第七十七引脚和第七十八引脚为i2c接口,第七十九引脚和第八十引脚为iic接口,第十九引脚、第二十引脚、第七十三引脚和第七十四引脚接地。

14.进一步的,第三板对板连接器(103)的第一引脚、第二引脚、

……

、第五引脚为jtag接口,第九引脚、第十引脚、

……

、第十九引脚、第二十三引脚、第二十四引脚、第二十五引脚、第二十六引脚、第二十九引脚、第三十引脚、

……

、第三十四引脚为usb接口,第四十五引脚、第四十六引脚、第四十七引脚、第四十八引脚、第五十一引脚、第五十二引脚、第五十三引脚、第五十四引脚、第五十七引脚、第五十八引脚、第五十九引脚和第六十引脚为pcie接口,第七引脚、第八引脚、第二十一引脚、第二十二引脚、第二十七引脚、第二十八引脚、第四十三引脚、第四十四引脚、第四十九引脚、第五十引脚、第五十五引脚、第五十六引脚、第六十一引脚和第六十二引脚接地。

15.进一步的,第四板对板连接器(104)的第一引脚、第二引脚、

……

、第六引脚为qspi接口,第十二引脚、第十四引脚、第十八引脚、第二十引脚、第二十四引脚、第二十六引脚、第三十引脚、第三十二引脚、第三十六引脚、第三十八引脚、第四十引脚和第四十二引脚为hdmi接口,第九引脚、第十引脚、第十五引脚、第十六引脚、第二十二引脚、第二十八引脚、第三十四引脚、第三十七引脚、第四十四引脚、第五十一引脚、第五十七引脚和第六十六引脚接地。

16.进一步的,每个板对板连接器包含80个引脚。

17.进一步的,所述每个板对板连接器的引脚间距为0.5mm。

18.进一步的,所述电源管理模块(4)为pmic电源管理模块。

19.与现有技术相比,本实用新型提供的一种高性能处理器智能核心板,具备以下有益效果:

20.(1)本实用新型提供的一种高性能处理器智能核心板,包括四个板对板连接器,板对板连接器按照预设引脚排布方式进行设置,本实用新型通过合理安排不同速率接口之间的引脚间距、同一功能接口统一放置引出、增加防反插保护、cpu引脚全部引出等方法,让使用者快速简单地设计出不同的产品、降低设计成本以及降低开发难度。

21.(2)本实用新型提供的一种高性能处理器智能核心板,布局合理,且包含多路功能不同的接口,延展性较好,功能性较强,能够缩短产品的开发时间。

附图说明

22.图1为本技术实施例提供的一种高性能处理器智能核心板的模块示意图;

23.图2为本技术实施例提供的一种高性能处理器智能核心板的结构示意图;

24.图3是本技术实施例提供的第一板对板连接器的电路原理图;

25.图4是本技术实施例提供的第二板对板连接器的电路原理图;

26.图5是本技术实施例提供的第三板对板连接器的电路原理图;

27.图6是本技术实施例提供的第四板对板连接器的电路原理图

具体实施方式

28.下面结合附图来具体描述本实用新型的优选实施例,其中,附图构成本技术一部分,并与本实用新型的实施例一起用于阐释本实用新型的原理,并非用于限定本实用新型的范围。

29.图1为本技术实施例提供的一种高性能处理器智能核心板的模块示意图,如图1所示,一种高性能处理器智能核心板,核心板包括高性能处理器1、内存模块2、存储器模块3、电源管理模块4、复位模块5、加密模块6和四个对称设置的板对板连接器;所述高性能处理器1分别与内存模块2、存储器模块3、电源管理模块4、复位模块5和加密模块6相连;所述板对板连接器和所述核心板的底板接口相连,所述板对板连接器的引脚按照预设方式设置排布;所述四个对称设置的板对板连接器分别位于核心板同一平面的四个端点处。值得注意的是,该高性能处理器智能核心板中的模块可根据实际需要删除或者增加,主要保护的是板对板连接器的设置。存储器模块3优选flash存储器,电源管理模块4优选pmic电源管理模块,pmic电源管理模块,负责cpu的上电时序及cpu需求各种不同电压的输出。

30.图2给出了本技术实施例提供的一种高性能处理器智能核心板的结构示意图,高性能处理器1为renesas g2x处理器,四个对称设置的板对板连接器分别为第一板对板连接器101、第二板对板连接器102、第三板对板连接器103和第四板对板连接器104;第一板对板连接器101和第二板对板连接器102设置于核心板的同一侧,第三板对板连接器103和第四板对板连接器104设置于核心板的另一侧;第一板对板连接器102与第三板对板连接器103对称设置,第二板对板连接器102和第四板对板连接器104对称设置;四个板对板连接器的位置可以根据实际情况进行排布,不仅限于本技术这一种排布方式。本实施例提供的每个板对板连接器均包含80个引脚,且每个板对板连接器的引脚间距均为0.5mm。

31.如图2所示,左下侧的板对板连接器为第一板对板连接器101,其第一引脚从右上角开始右左交替依次向下排列,共80个引脚;左上侧的板对板连接器为第二板对板连接器102,其第一引脚从右上角开始右左交替依次向下排列,共80个引脚;右下侧的板对板连接器为第三板对板连接器103,其第一引脚从右上角开始右左交替依次向下排列,共80个引脚;右上侧的板对板连接器为第四板对板连接器104,其第一引脚从右上角开始右左交替依次向下排列,共80个引脚;四个板对板连接器共320个引脚。

32.具体的,第一板对板连接器101和第二板对板连接器102设置于核心板的同一侧,第三板对板连接器103和第四板对板连接器104设置于核心板的另一侧;第一板对板连接器102与第三板对板连接器103对称设置,第二板对板连接器102和第四板对板连接器104对称设置,可以防止用户在使用过程中出现倒插的现象。

33.图3是本技术实施例提供的第一板对板连接器101的电路原理图,图3给出了第一板对板连接器101的具体引脚电路,该电路中的引脚位置和定义均为特殊设计用以解决串扰、布线困难的问题。其中,第一板对板连接器101具有若干audio接口、scif接口、hscif接口、ssi接口、gpio接口、sd卡接口、数据收发通信接口和i2c接口;所述若干audio接口、scif

接口、hscif接口、gpio接口、sd卡接口、数据收发通信接口和i2c接口均与高性能处理器1电性连接。结合图3来看,第一板对板连接器包括1路audio接口、4路scif接口、2路hscif接口、1路ssi接口、3路sd卡接口、1路msiof接口、3路i2c接口和4路gpio接口;所述1路audio接口、4路scif接口、2路hscif接口、1路ssi接口、3路sd卡接口、1路msiof接口、3路i2c接口和4路gpio接口均与高性能处理器1电性连接。

34.值得注意的是,本实施例中scif接口、hscif接口均为uart串口,scif接口和hscif接口的功能、作用、定义、性质均与uart串口一致,本实施例中只是标号采用自定义标号,实际使用过程中功能、作用、定义、性质均与uart串口一致;网络标号为msiof的接口为数据收发通信接口;网络标号为gp的接口为gpio接口,gpio接口表示通用输入输出接口;本实施例定义的接口类型为公知常识,本实施例未提及的接口定义可参照下表和图3,此处不再赘述。

35.示例性的,其中第一板对板连接器101的第一引脚、第二引脚和第四引脚为audio接口,第六引脚、第八引脚、第十引脚和第十二引脚为ssi接口,第六十一引脚、第六十二引脚、第七十七引脚、第七十八引脚、第七十九引脚和第八十引脚为i2c接口,第十三引脚、第十四引脚、第三十一引脚、第三十二引脚、第四十七引脚、第四十八引脚、第六十三引脚和第六十四引脚接地。第十一引脚、第三十九引脚、第五十三引脚、第五十五引脚、第六十七引脚、第六十八引脚、

……

、第七十六引脚为gpio接口,第二十三引脚、第二十四引脚、

……

、第三十引脚、第三十三引脚、第三十四引脚、

……

、第三十八引脚,第四十一引脚、第四十二引脚、

……

、第四十六引脚为sd卡接口。上述仅为选取的具备代表性的引脚示例,其他引脚位置和定义关系参见下表以及附图3,此处不再赘述。

36.图4是本技术实施例提供的第二板对板连接器102的电路原理图,图4给出了第二板对板连接器102的具体引脚电路,该电路中的引脚位置和定义均为特殊设计用以解决串扰、布线困难的问题。其中,第二板对板连接器102具有若干avb接口、显示接口、扩展总线接口、scif接口、can接口、iic接口、pwm接口和i2c接口;所述若干avb接口、gpio接口、显示接口、扩展总线接口、scif接口、can接口、iic接口、pwm接口和i2c接口均与高性能处理器1电性连接。结合图4来看,第二板对板连接器102包括1路avb接口、1路显示接口、1路扩展总线接口、1路scif接口、2路can接口、2路i2c接口、1路pwm接口和1路iic接口;所述1路avb接口、1路显示接口、1路扩展总线接口、1路scif接口、2路can接口、2路i2c接口、1路pwm接口和1路iic接口均与高性能处理器1电性连接。

37.值得注意的是,本实施例中的avb接口为多媒体数据传输接口;网络标号为du的接口表示显示接口;网络标号为ex的接口表示扩展总线接口;scif接口的功能、作用、定义、性质均与uart串口一致,本实施例中只是标号采用自定义标号,实际使用过程中功能、作用、定义、性质均与uart串口一致;pwm接口表示pwm脉冲输出接口;本实施例定义的接口类型为公知常识,本实施例未提及的接口定义可参照下表和图4,此处不再赘述。

38.示例性的,第二板对板连接器102的第一引脚、第二引脚、

……

、第十三引脚、第十五引脚、第十六引脚、第十七引脚和第十八引脚为avb接口,第六十九引脚、第七十引脚、第七十一引脚、第七十二引脚为can接口,第七十五引脚、第七十六引脚、第七十七引脚和第七十八引脚为i2c接口,第七十九引脚和第八十引脚为iic接口,第十九引脚、第二十引脚、第七十三引脚和第七十四引脚接地。第五十二引脚为pwm接口。上述仅为选取的具备代表性的

引脚示例,其他引脚位置和定义关系参见下表以及附图4,此处不再赘述。

39.图5是本技术实施例提供的第三板对板连接器103的电路原理图,图5给出了第三板对板连接器103的具体引脚电路,该电路中的引脚位置和定义均为特殊设计用以解决串扰、布线困难的问题。其中,第三板对板连接器103具有若干jtag接口、usb接口、gpio接口和pcie接口;所述若干jtag接口、usb接口、gpio接口和pcie接口均与高性能处理器1电性连接。结合图5来看,第三板对板连接器103包括1路jtag接口、5路usb接口、1路gpio接口和2路pcie接口;所述1路jtag接口、5路usb接口、1路gpio接口和2路pcie接口均与高性能处理器1电性连接。

40.值得注意的是,pcie接口为高速串行总线接口;gpio接口为通用输入输出接口;本实施例定义的接口类型为公知常识,本实施例未提及的接口定义可参照下表和图5,此处不再赘述。

41.示例性的,第三板对板连接器103的第一引脚、第二引脚、

……

、第五引脚为jtag接口,第九引脚、第十引脚、

……

、第十九引脚、第二十三引脚、第二十四引脚、第二十五引脚、第二十六引脚、第二十九引脚、第三十引脚、

……

、第三十四引脚为usb接口,第四十五引脚、第四十六引脚、第四十七引脚、第四十八引脚、第五十一引脚、第五十二引脚、第五十三引脚、第五十四引脚、第五十七引脚、第五十八引脚、第五十九引脚和第六十引脚为pcie接口,第七引脚、第八引脚、第二十一引脚、第二十二引脚、第二十七引脚、第二十八引脚、第四十三引脚、第四十四引脚、第四十九引脚、第五十引脚、第五十五引脚、第五十六引脚、第六十一引脚和第六十二引脚接地。上述仅为选取的具备代表性的引脚示例,其他引脚位置和定义关系参见下表以及附图5,此处不再赘述。

42.图6是本技术实施例提供的第四板对板连接器104的电路原理图,图6给出了第四板对板连接器104的具体引脚电路,该电路中的引脚位置和定义均为特殊设计用以解决串扰、布线困难的问题。其中,第四板对板连接器104具有若干qspi接口、csi接口、gpio接口、hdmi接口和lvds接口;所述若干qspi接口、csi接口、hdmi接口和lvds接口均与高性能处理器1电性连接。结合图6来看,第四板对板连接器104具有若干qspi接口、csi接口、gpio接口、hdmi接口和lvds接口;所述若干qspi接口、csi接口、hdmi接口和lvds接口均与高性能处理器1电性连接。结合图6来看,第四板对板连接器104包括1路qspi接口、1路gpio接口、1路hdmi接口、2路csi接口和1路lvds接口;所述1路qspi接口、1路gpio接口、1路hdmi接口、2路csi接口和1路lvds接口均与高性能处理器1电性连接。

43.值得注意的是,qspi接口属于spi接口的拓展;csi接口为相机串行接口;本实施例定义的接口类型为公知常识,本实施例未提及的接口定义可参照下表和图6,此处不再赘述。

44.示例性的,第四板对板连接器104的第一引脚、第二引脚、

……

、第六引脚为qspi接口,第十二引脚、第十四引脚、第十八引脚、第二十引脚、第二十四引脚、第二十六引脚、第三十引脚、第三十二引脚、第三十六引脚、第三十八引脚、第四十引脚和第四十二引脚为hdmi接口,第九引脚、第十引脚、第十五引脚、第十六引脚、第二十二引脚、第二十八引脚、第三十四引脚、第三十七引脚、第四十四引脚、第五十一引脚、第五十七引脚和第六十六引脚接地。第十一引脚和第十三引脚为gpio接口。上述仅为选取的具备代表性的引脚示例,其他引脚位置和定义关系参见下表以及附图6,此处不再赘述。

45.具体的引脚位置设置和定义中,将高速率接口引脚设置在芯片靠外的两侧,如usb接口对应的引脚,同时多个不同类型的数据传输引脚之间通过gnd接地引脚相隔,由此防止二者之间出现串扰现象,同时,相同类型的引脚设置在一起,如i2c接口、iic接口等功能性引脚设置在相邻位置。下表中板对板连接器的引脚与处理器中的cpu管脚一一对应,具体对应关系如下表所示,在此不再赘述。

46.本实用新型提供的一种高性能处理器智能核心板,包括四个板对板连接器,板对板连接器按照预设引脚排布方式进行设置,本实用新型通过合理安排不同速率接口之间的引脚间距、同一功能接口统一放置引出、增加防反插保护、cpu引脚全部引出等方法,让使用者快速简单地设计出不同的产品、降低设计成本以及降低开发难度。

47.本实用新型提供的一种高性能处理器智能核心板,布局合理,且包含多路功能不同的接口,延展性较好,功能性较强,能够缩短产品的开发时间。

48.核心板引脚功能定义如下:

49.第一板对板连接器101:

50.[0051][0052]

第二板对板连接器102:

[0053]

[0054][0055]

第三板对板连接器103:

[0056]

[0057][0058]

第四板对板连接器104:

[0059]

[0060][0061]

本方案中,通过对板对板连接器的引脚位置的设置和具体的连接关系实现了合理安排不同速率接口之间的引脚间距、同一功能接口统一放置引出、增加防反插保护、cpu引脚全部引出等方法,让使用者快速简单地设计出不同的产品、降低设计成本,并且cpu引脚

复用功能维持原定义、扩展或转换功能重新定义并通过板对板连接器引出,用户可参考评估板进行设计,以配合产品标准驱动的开发,且本方案中能够缩短产品开发时间,加快产品开发速度,提高产品的开发效率。本方案提供的核心板布局合理,延展性好,同一功能接口统一放置引出,有利于使用者提高产品的开发效率,降低开发和维护成本。解决了现有核心板模块做管脚引出时产生的pcb布线困难、不同速率接口之间有串扰、方向错误时烧坏核心板的问题,可让使用者快速简单进行产品开发,降低开发和维护成本,在设计aiot、智能识别、深度学习等领域产品时,能够快速根据不同应用场合做出设计时。

[0062]

在本实用新型的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”、“顺时针”、“逆时针”、“轴向”、“径向”、“周向”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本实用新型和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本实用新型的限制。

[0063]

在本实用新型中,除非另有明确的规定和限定,术语“设置”、“安装”、“相连”、“连接”、“固定”等术语应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或成一体;可以是机械连接,可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通或两个元件的相互作用关系。对于本领域的普通技术人员而言,可以根据具体情况理解上述术语在本实用新型中的具体含义。

[0064]

此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本实用新型的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

[0065]

需要说明的是,在本实用新型中,除非另有明确的规定和限定,第一特征在第二特征“上”或“下”可以是第一和第二特征直接接触,或第一和第二特征通过中间媒介间接接触。而且,第一特征在第二特征“之上”、“上方”和“上面”可是第一特征在第二特征正上方或斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”可以是第一特征在第二特征正下方或斜下方,或仅仅表示第一特征水平高度小于第二特征。

[0066]

以上所述,仅为本实用新型较佳的具体实施方式,但本实用新型的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本实用新型揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1