一种计算机主板用控制器模式配置电路的制作方法

1.本实用新型涉及计算机主板技术领域,具体涉及一种计算机主板用控制器模式配置电路。

背景技术:

2.开发板是用来进行嵌入式系统开发的电路板,包括中央处理器、存储器、输入设备、输出设备、数据通路/总线和外部资源接口等一系列硬件组件。部分开发板提供有基础集成开发环境和软件源代码和硬件原理图等,开发者依据获开发板环境进行研究设计。为更高翔的集成开发板环境,节省开发板的外设接口数量,通常会在开发板上增设大量多功能接口,应此需要一种能够调整接口功能的电路,方便开发板上外设接口功能的转换。

技术实现要素:

3.有鉴于此,本实用新型要解决的问题是提供一种计算机主板用控制器模式配置电路,能够调整外设接口功能的电路,以便任意改变开发板上外设接口的功能。

4.为解决上述技术问题,本实用新型采用的技术方案是:

5.一种计算机主板用控制器模式配置电路,包括有用于与外设连接的cn4 插排,所述cn4插排连接有用于数据处理的主控芯片,所述主控芯片连接有存储芯片,所述cn4插排的a11端口连接有sw1选择开关的2接口,所述sw1选择开关的1接口连接有rc配置电路,

6.所述rc配置电路包括有输出端与u7与逻辑门的1输入端连接的外控复位电路,所述u7与逻辑门的2输入端连接有主控芯片的gpio总线扩展接口,所述u7与逻辑门的4输出端通过第一导通电路与sw1选择开关的1 接口,用于使cn4插排连接的外设与主控芯片数据互通。

7.进一步的,所述sw1选择开关的3接口连接有ep配置电路,所述ep 配置电路包括有输入端与sw1选择开关连接的第二导通电路,所述第二导通电路的输出端与主控芯片的主控复位接口连接;

8.所述第二导通电路的输出端连接有r233电阻的一端,另一端与存储芯片的存储复位接口连接,所述r233电阻并接有第三导通电路,所述第三导通电路的输入端与存储复位接口连接。

9.进一步的,所述第一导通电路、第二导通电路和第三导通电路的结构相同,所述第一导通电路包括有栅极与u7与逻辑门的4输出端连接的第一 mos管,所述第一mos管的漏极与第二mos管的栅极连通,所述第二 mos管漏极与sw1选择开关的1接口。

10.进一步的,所述外控复位电路包括有sw4轻触开关,所述sw4轻触开关的一端接地设置,另一端与u4复位芯片的输入端连接,所述u4复位芯片的输出接口与u7与逻辑门连接。

11.进一步的,所述外控复位电路的输出端与存储芯片的存储复位接口连接。

12.进一步的,所述sw4轻触开关的输出端分别连接有c32电容和d26瞬态电压抑制器的一端,另一端均接地设置,用于降低sw4轻触开关产生的瞬态激励。

13.进一步的,所述u4复位芯片的输出端接有用于整流的d16二极管。

14.进一步的,所述主控芯片连接有sw2四路拨码开关的一端,另一端接地设置,用于控制主控芯片运行rc功能或ep功能。

15.进一步的,所述cn4插排的信号可为pcie_edge。

16.本实用新型具有的优点和积极效果是:

17.通过在开发板上设置同时具有的rc和ep两种模式的cn4插排,cn4 插排的a11端口连接有sw1选择开关的2端口,sw1选择开关的1端口连接有rc配置电路,sw1选择开关3端口连接有ep配置电路,可依据实际的使用需要改变sw1选择开关的位置,使sw1选择开关与对应的电路连接,以调整外设接口的功能,以便任意改变开发板上外设接口的功能。

附图说明

18.附图用来提供对本实用新型的进一步理解,并且构成说明书的一部分,与本实用新型的实施例一起用于解释本实用新型,并不构成对本实用新型的限制。在附图中:

19.图1是本实用新型的一种计算机主板用控制器模式配置电路中cn4插排与sw1选择开关的连接电路图;

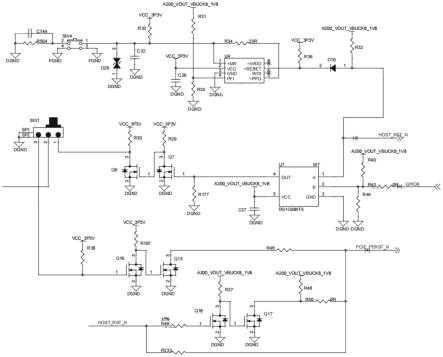

20.图2是本实用新型的一种计算机主板用控制器模式配置电路中rc配置电路和ep配置电路与sw1选择开关的连接电路图;

21.图3是本实用新型的一种计算机主板用控制器模式配置电路中sw2四路拨码开关的连接电路图。

具体实施方式

22.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

23.需要说明的是,当组件被称为“固定于”另一个组件,它可以直接在另一个组件上或者也可以存在居中的组件。当一个组件被认为是“连接”另一个组件,它可以是直接连接到另一个组件或者可能同时存在居中组件。当一个组件被认为是“设置于”另一个组件,它可以是直接设置在另一个组件上或者可能同时存在居中组件。本文所使用的术语“垂直的”、“水平的”、“左”、“右”以及类似的表述只是为了说明的目的。

24.除非另有定义,本文所使用的所有的技术和科学术语与属于本实用新型的技术领域的技术人员通常理解的含义相同。本文中在本实用新型的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本实用新型。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

25.本实用新型提供一种计算机主板用控制器模式配置电路,计算机主板内包括有主控芯片,主控芯片用于依据内部程序控制连接的外设动作。主控芯片连接有存储芯片,用于存储外设运行时产生的数据。

26.如图1个图2所示,包括有用于用于与主控芯片数据互通的cn4插排,优选的,cn4插排的型号可为pcie_edge。cn4插排包括有rc模式和ep 模式,当为rc模式时,cn4插排将外设

与主控芯片数据互通,用于与外设数据互通或接收外设提供的反馈。当为ep模式时,cn4插排主要用于接收针对主控芯片内的读写工作,读取主控芯片内数据或导入数据等。

27.如图3所示,主控芯片连接有sw2四路拨码开关的一端,另一端接地设置,可手动设定sw2四路拨码开关的导通和断开状态,往主控芯片内输入指令,以控制主控芯片运行rc功能或ep功能。例如:主控芯片运行rc 功能时,sw2四路拨码开关的为0100,即只断开第二个开关。

28.cn4插排的cn4插排的a11端口为转换端口,常规时cn4插排为ep 模式,当给a11端口一个激励,cn4插排转变为rc模式。cn4插排的a11 端口连接有sw1选择开关的2接口,sw1选择开关的1接口连接有rc配置电路,sw1选择开关的3接口连接有ep配置电路。

29.rc配置电路包括有外控复位电路,外控复位电路包括有sw4轻触开关, sw4轻触开关的一端并接有c144电容和r564电阻的一端,另一端接地设置。sw4轻触开关的另一端与u4复位芯片的输入端连接,u4复位芯片的输出端连接有存储芯片的存储复位口。当开启计算机主板并测试设备功能时,手动轻触sw4轻触开关使外控复位电路导通,对存储器进行复位。

30.u4复位芯片的输出端接有d16二极管,可对u4复位芯片输出端的信号进行整流,以保证u4复位芯片输出电压的平稳性。优选的,d16二极管为肖特二极管。sw4轻触开关的输出端连接有c32电容和d26瞬态电压抑制器的一端,另一端均接地设置,用于降低sw4轻触开关产生的瞬态激励,以保证sw4轻触开关产生的信号的平稳性,降低u4复位芯片误开启的概率。

31.外控复位电路的输出端连接有u7与逻辑门的1输入端,u7与逻辑门的 2输入端连接有主控芯片的gpio总线扩展接口,u7与逻辑门的4输出端通过第一导通电路与sw1选择开关的1接口。第一导通电路包括有栅极与u7 与逻辑门的4输出端连接的第一mos管,第一mos管的漏极与第二mos 管的栅极连通,第二mos管漏极与sw1选择开关的1接口连接。当u7与逻辑门导通使,u7与逻辑门的4输出端输出的电压依次使第一mos管和第二mos管导通。

32.计算机主板运行时,手动闭合sw4轻触开关使外控复位电路导通(设置刚开始运行时,进行一次复位操作),主控芯片的gpio总线扩展接口同时输出高电平以使u7与逻辑门导通,拨动sw1选择开关使1接口与2接口连通,cn4插排接收到信号并转换成rc模式,主控芯片可与外设数据互通,控制外设动作和接收外设给出的反馈。

33.sw1选择开关的3端口通过第二导通电路与存储芯片的控制复位端口数据互通,第二导通电路的结构与第一导通电路的结构相同,且第二导通电路的导通电压低于第一导通电路的电压。第二导通电路的输出端与存储复位端口之间串接有r233电阻,拨动sw1选择开关使2接口与3接口导通,cn4插排的a11端口输出的电压使第二导通电路导通,使得主控芯片和存储芯片同时复位,以便芯片后续的读写操作,且通常往芯片内烧录程序之前,均需要作复位处理。

34.r233电阻并接有第三导通电路,第三导通电路的输入端与存储芯片的复位接口连接,第三导通电路的结构也与第一导通电路的结构相同。当第三导通电路导通后,可保证存储芯片和主控芯片同时复位,且不受外部磁场设备磁场的干扰。

35.本实用新型的工作原理和工作过程如下:

36.使用开发板进行开发设计时,开发者依据开发的功能往开发板内烧录入程序,给

开发板通电,cn4插排的初始模式为ep模式,并拨动sw1选择开关使2接口与3接口导通,cn4插排的a11端口的电压使第二导通电路导通,主控芯片的控制复位端口接收到信号,主控芯片进行复位操作,第二导通电路的输出电压经过r233电阻后输入至第三导通电路的输入端,并使第三导通电路导通,由于第三导通电路由两个mos管串接构成,当mos 管导通后相当于一条导线(电流正反方向流都可以),存储复位端口接收到信号,存储芯片作复位动作。通过cn4插排往主控芯片和存储芯片内存入数据。

37.程序烧录完成后主控芯片开始运行,主控芯片的gpio总线扩展接口输出高电平,使得u7与逻辑门的2输入端接入高电平。按下sw4轻触开关, u4复位芯片接收到信号并输出复位反馈,复位反馈输入至存储复位端口,存储芯片作复位动作。同时复位反馈使u7与逻辑门的1输入端接入高电平, u7与逻辑门导通,拨动sw1选择开关使2接口与1接口导通,cn4插排接收到信号并转变成rc模式,通过cn4插排与若干外设连接,若干外设与主控芯片数据互通。

38.以上对本实用新型的实施例进行了详细说明,但所述内容仅为本实用新型的较佳实施例,不能被认为用于限定本实用新型的实施范围。凡依本实用新型范围所作的均等变化与改进等,均应仍归属于本专利涵盖范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1