一种时钟停振检测电路及SOC芯片的制作方法

一种时钟停振检测电路及soc芯片

技术领域

1.本实用新型涉及芯片半导电体电路技术领域,尤其涉及一种时钟停振检测电路及soc芯片。

背景技术:

2.时钟信号为数字系统提供基本的频率信号,对于soc芯片是不可或缺的,是soc芯片正常工作最重要的信号之一。为了适用更多的应用场景,很多soc芯片会同时支持使用片内的rc时钟以及片外的晶振时钟。片内rc时钟的可靠性高且成本较低,但是,时钟频率精度随着温度等因素变化范围较大,在出厂前需要做好校准,甚至还要做实时的温度补偿。片外晶振时钟的精度高且成本高,主要应用于对时钟精度要求较高的应用场景,比如无线通信、高精度定时等。

3.片外晶振时钟在芯片外部,有多种原因可能导致晶振时钟信号无法正常起阵,进而导致soc芯片无法正常接收到晶振产生的时钟信号。导致晶振时钟无法正常工作的原因通常包括:晶振虚焊或者连锡、晶振损坏、晶振旁路电容不匹配等。

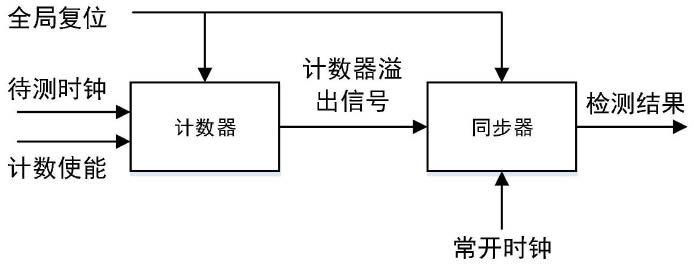

4.当前通常使用计数器的方式进行时钟停振检测,其检测逻辑具体如下所述。

5.如图1所示,使用一个计数器。在待测时钟域下进行计数,计满保持。全局复位信号可以复位计数器,将计数值清零,全局复位释放后打开计数使能则计数器开始计数,在每个待测时钟的上升沿加1。计数器计满后保持并产生计数器溢出信号,计数器溢出信号通过同步器同步到常开时钟,同步后的信号即为检测结果信号。如果待测时钟正常,则计数器能够累加到溢出,产生高电平的检测结果信号;如果待测时钟异常,则计数器值不累加或无法累加到最大值产生溢出有效信号。待测时钟正常工作情况下,计数器计满之后如果需要再次检测时钟停振,则需要将计数器复位。soc系统在打开计数使能之后等待合适的时间再去检查检测结果,检测结果为高说明待测时钟正常,低说明待测时钟异常。

6.如图2中所示,使用两个计数器。其中计数器1在待测时钟域进行累加,计满溢出到0重新计数;计数器2在常开时钟域进行累加,计满保持。当计数器1大于等于预先设置好的比较阈值则产生计数器2复位信号,去复位计数器2。如果待测时钟正常的情况下,计数器1正常计数,则会周期性产生计数器复位信号,计数器2无法计满溢出;如果待测时钟异常,则计数器2复位信号无法产生,则计数器2可以计到溢出,产生的计数器2溢出信号作为检测结果,高表示待测时钟异常,低表示待测时钟正常。

7.现有技术中,当soc芯片无法接收到正常的晶振时钟信号时,有可能会导致soc无法正常工作甚至停止工作,从而也无法上报错误信息,导致系统面临死机的风险。

技术实现要素:

8.为解决背景技术中存在的技术问题,本实用新型提出一种时钟停振检测电路,能够实时地监测时钟的状态,快速地检测出时钟是否停振,并上报检测结果。

9.本实用新型提出一种时钟停振检测电路,包括:同步器、异或门、三位计数器、第一

d触发器,比较器、第二d触发器;

10.同步器的两个输入可分别与参考时钟和待测时钟连接,同步器的两个输出分别与异或门的两个输入连接,异或门的输出与三位计数器的第一输入连接,三位计数器的第二输入可与待测时钟连接,三位计数器的输出与第一d触发器的第一输入连接,第一d触发器的第二输入可与参考时钟连接,三位计数器的输出和第一d触发器的输出分别与比较器的两个输入连接,比较器的输出与第二d触发器的第一输入连接,第二d触发器的第二输入可与参考时钟连接,第二d触发器输出时钟检测信号。

11.优选地,同步器具有两个输入端和两个输出端;输入端d可与参考时钟连接,输入端clk可与待测时钟连接,输出端syn2和syn3分别与异或门的两个输入端连接。

12.优选地,异或门具有两个输入端和一个输出端;两个输入端分别与同步器的输出端syn2和syn3连接;输出端与三位计数器的输入端en连接。

13.优选地,三位计数器具有两个输入端和一个输出端;输入端clk可与待测时钟连接,输入端en与异或门的输出端连接;输出端cnt[2:0]与第一d触发器和比较器连接。

[0014]

优选地,第一d触发器具有两个输入端和一个输出端;第一输入端d与三位计数器的输出端cnt[2:0]连接,第二输入端可与参考时钟连接;输出端q与比较器连接。

[0015]

优选地,比较器具有两个输入端和一个输出端;第一输入端与三位计数器的输出端cnt[2:0]端连接,第二输入端与第一d触发器的输出端q连接;输出端与第二d触发器连接;

[0016]

优选地,第二d触发器具有两个输入端和一个输出端;第一输入端d与比较器的输出端连接,第二输入端可与参考时钟连接;输出端q输出时钟检测信号。

[0017]

本实用新型提出了一种soc芯片,包括中央处理器cpu、片内总线、晶振电路、rc时钟电路、时钟分频电路、系统控制/时钟选择电路,集成了上述的时钟停振检测电路;

[0018]

系统控制/时钟选择电路通过片内总线挂载在中央处理器cpu上;

[0019]

晶振电路与时钟停振检测电路连接,时钟分频与时钟停振检测电路连接,rc时钟电路与时钟分频电路连接;晶振电路、时钟停振检测电路、时钟分频电路、rc时钟电路分别与系统控制/时钟选择电路连接。

[0020]

本实用新型的一种时钟停振检测电路中,包括:同步器、异或门、三位计数器、第一d触发器,比较器、第二d触发器。使用异或门在待测时钟的时钟域下检测参考时钟的跳变沿,当参考时钟信号发生上升沿或者下降沿的跳变时,产生一个高电平信号使得三位计数器的计数值加1,d触发器计数值延迟一个时钟周期后与原计数值通过比较器进行比较。如果待测时钟正常工作,则两者不相等,比较器始终输出0;如果待测时钟停振,则计数器停止计数并保持原计数值,一个参考时钟周期后,比较器的两个输入值相等,比较器的输出信号变为1。比较器的输出信号经过d触发器延迟一个时钟周期后输出信号,通知系统或其它模块当前时钟停振检测结果。如果待测时钟停振,可以在三个参考时钟周期内快速地检测出来,并上报检测结果。通过实时地监测时钟的状态,可以快速地检测出时钟是否停振,并上报检测结果。

附图说明

[0021]

图1为典型的一个计数器下的时钟停振检测电路的结构示意图。

[0022]

图2为典型的两个计数器下的时钟停振检测电路的结构示意图。

[0023]

图3为本实用新型的实施例中一种时钟停振检测电路的结构示意图。

[0024]

图4为本实用新型的实施例中同步器的电路结构示意图。

[0025]

图5为本实用新型的实施例中待测时钟正常工作时的信号时序图。

[0026]

图6为本实用新型的实施例中待测时钟停振后的信号时序图。

[0027]

图7为本实用新型中一种soc芯片的结构示意图。

具体实施方式

[0028]

本实用新型提出一种时钟停振检测电路,使用片内rc时钟实时地监测晶振时钟,当检测到晶振时钟停振时上报系统,soc系统可以自动切换到片内rc时钟。soc使用rc时钟可以保持基本的功能继续工作,进行错误处理等。

[0029]

如图3和图7所示,本实用新型实施例提出的一种时钟停振检测电路,包括:同步器10、异或门20、三位计数器30、第一d触发器40,比较器50、第二d触发器60。

[0030]

同步器10,如图4所示,具有两个输入端和两个输出端;输入端d与参考时钟连接,参考时钟与时钟分频连接(内部时钟),输入端clk与待测时钟连接,待测时钟与晶振电路连接(外部时钟);输出端syn2和syn3分别与异或门20的两个输入端连接,输出端syn2的输出信号为s1,输出端syn3的输出信号为s2。

[0031]

异或门20,具有两个输入端和一个输出端;两个输入端分别与同步器10的输出端syn2和syn3连接;输出端与三位计数器30的输入端en连接,该输出端的输出信号为s3;

[0032]

三位计数器30,具有两个输入端和一个输出端;输入端clk与待测时钟连接,待测时钟与晶振电路连接(外部时钟),输入端en与异或门20的输出端连接;输出端cnt[2:0]与第一d触发器40和比较器50连接,该输出端的输出信号为s4;

[0033]

第一d触发器40,具有两个输入端和一个输出端;第一输入端d与三位计数器30的输出端cnt[2:0]连接,第二输入端与参考时钟连接,参考时钟与时钟分频连接(内部时钟);输出端q与比较器50连接,该输出端的输出信号为s5;

[0034]

比较器50,具有两个输入端和一个输出端;第一输入端与三位计数器30的输出端cnt[2:0]端连接,第二输入端与第一d触发器的输出端q连接;输出端与第二d触发器60连接,该输出端的输出信号为s6;

[0035]

第二d触发器60,具有两个输入端和一个输出端;第一输入端d与比较器50的输出端连接,第二输入端与参考时钟连接,参考时钟与时钟分频连接(内部时钟);输出端q与clk_fail连接,clk_fail与系统控制/时钟选择连接。

[0036]

在本实施例中,关于时钟频率,参考时钟的时钟频率需要小于待测时钟的时钟频率的1/8,即freg

参考时钟

《freg

待测时钟

/8。

[0037]

在本实施例中,s1为同步器10的syn2的输出,s2为同步器10的syn3的输出;s1和s2输入至异或门20,异或门20输出s3,s3输入至三位计数器30;三位计数器30输出s4,s4经过第一d触发器40延迟一个时钟周期产生s5,s4与s5输入到比较器50中进行比较,比较结果输出s6;s6通过第二d触发器60延迟一个时钟周期,产生最终的时钟检测信号clk_fail。

[0038]

在本实施例中,异或门20是在待测时钟的时钟域下检测参考时钟的跳变沿,当参考时钟信号发生上升沿或者下降沿的跳变时,s3信号会产生高电平;当s3信号为高电平时

使得三位计数器30的计数值加1,第一d触发器40将三位计数器30的计数值s4延迟一个时钟周期,之后再进行比较。

[0039]

如果待测时钟正常工作,则s4始终会大于s5,s4与s5不相等,s6始终为0;如果待测时钟停振,则计数器30停止计数并保持原计数值,即s4保持不变。在接下来的参考时钟上升沿,s4延迟一个参考时钟周期后输出s5,由于s4保持不变,使得s5等于s4,则比较器50的输出信号s6变为1。

[0040]

为了避免组合逻辑电路产生的毛刺,s6经过第二d触发器60延迟一个时钟周期,寄存器输出信号clk_fail,通知系统或其它模块当前时钟停振检测结果。

[0041]

如图5所示,在本实施例中,当待测时钟正常工作时,其逻辑如下所述:

[0042]

s1和s2信号之间有一个待测时钟的延时,异或后的s3信号在参考时钟的上升沿和下降沿分别产生了高电平;

[0043]

s4计数器在s3高电平有效时进行累加,在参考时钟上升沿时从0变成1,在参考时钟下降沿时从1变成2;

[0044]

s5计数器默认值为7,在第二个参考时钟的上升沿时将s4的值存入其中d触发器,由7变为1;

[0045]

s4和s5的值始终不相等,因此s6始终为低电平;

[0046]

clk_fail信号初始为高电平,忽略不计,从s4开始计时后变为低电平,表示待测时钟时钟工作正常。

[0047]

如图6所示,在本实施例中,当待测时钟停振时,其逻辑如下所述:

[0048]

为了方便说明,在图6中缩短了单位时间9~16内参考时钟的时钟周期:

[0049]

待测时钟在1~8单位时间内工作正常,在这期间s1和s2正常工作,异或后的s3信号在参考时钟的上升沿产生了高电平;

[0050]

待测时钟在9~18单位时间内停振,在这期间s1和s2保持高电平不变,参考时钟的下降沿在s1和s2电平上未体现,s3就只产生一次高电平;

[0051]

s4计数器在s3高电平时进行累加,在参考时钟上升沿时从0变成1,之后保持1的值不变;

[0052]

s5计数器默认值为7,在第二个参考时钟的上升沿时将s4的值存入其中d触发器,由7变为1;

[0053]

s5的值变为1后,s4和s5的值相等,因此s6变为高电平;

[0054]

clk_fail信号初始为高电平,忽略不计,clk_fail相对s6延迟一个参考时钟后变为高电平,表示待测时钟时钟停振。

[0055]

如图7所示,本实用新型实施例提出了一种soc芯片,集成了该时钟停振检测电路,该芯片主要组成部分包括:中央处理器cpu、片内总线、晶振电路、rc时钟电路、时钟分频电路、系统控制电路、时钟停振检测电路。

[0056]

时钟停振检测电路具有两个输入端口和一个输出端口,输入端口(待测时钟)和输入端口(参考时钟)分别与晶振电路和时钟分频连接,其中时钟分频与rc时钟电路连接,输出端口clk_fail与系统控制/时钟选择连接;

[0057]

晶振电路具有两个输入端口和两个输出端口,两个输入端口为芯片管脚外接晶振,其中一个输出端口(待测时钟)作为时钟停振检测电路的输入端,另外一个输出端口(晶

振时钟)作为系统控制/时钟选择的输入端;

[0058]

rc时钟电路具有两个输出端口,其中一个输出端口(rc时钟)与时钟分频连接作为它的输入,另外一个输出端口(rc时钟)与系统控制/时钟选择连接;

[0059]

时钟分频电路具有两个输入端口和一个输出端口,其中一个输入端口(rc时钟)与rc时钟电路连接,另外一个输入端口(分频系数)与系统控制/时钟选择连接,输出端口(参考时钟)与时钟停振检测电路连接;

[0060]

系统控制/时钟选择电路具有三个输入端口和三个输出端口,其中一个输入端口(晶振时钟)与晶振电路连接,另外一个输入端口(rc时钟)与rc时钟电路连接,还有一个输入端口clk_fail与时钟停振检测电路连接;其中一个输出端口(分频系数)与时钟分频连接,另外两个输出端口分别于中央处理器cpu和其它模块连接;

[0061]

系统控制/时钟选择电路通过片内总线挂载在中央处理器cpu上,以用于中央处理器cpu通过片内总线对其进行参数配置,在具体实施例中,片内总线上还可以挂载其他各种外设接口。

[0062]

外部晶振的晶体通过两个管脚与片内晶振电路连接,晶振电路产生的晶振时钟连接到时钟停振检测电路作为待测时钟,同时连接到系统控制作为系统时钟的来源之一。内部rc时钟电路产生的rc时钟进行时钟分频后连接到时钟停振检测电路作为参考时钟,同时连接到系统控制作为系统时钟的来源之一,时钟分频是为了保证参考时钟的频率小于待测时钟的1/8。时钟停振检测电路输出clk_fail信号连接到系统控制,系统控制挂载到系统总线上,根据用户配置和clk_fail电平选择合适的来源产生系统时钟。

[0063]

在系统工作过程中,系统默认选择rc时钟作为系统时钟,晶振时钟默认不使能;用户配置打开晶振时钟使能后将系统时钟切换到晶振时钟,同时相应的配置时钟分频,使能时钟停振检测电路。当时钟停振检测电路检测到晶振时钟停振,则clk_fail信号为高电平;系统控制接收到clk_fail信号高电平,则将系统时钟切换到rc时钟,同时上报cpu进行错误处理。

[0064]

以上所述,仅为本实用新型较佳的具体实施方式,但本实用新型的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本实用新型揭露的技术范围内,根据本实用新型的技术方案及其实用新型构思加以等同替换或改变,都应涵盖在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1