一种固态硬盘及固态硬盘访问控制系统

1.本实用新型涉及存储技术领域,尤其涉及一种固态硬盘及固态硬盘访问控制系统。

背景技术:

2.固态硬盘(solid state disk或solid state drive,ssd)是传统机械式硬盘的替代品。一个典型的固态硬盘,其内部电路包括主控芯片、ddr内存颗粒、nand flash闪存芯片颗粒、spi flash颗粒等。在某些应用场景下,对固态硬盘会有数据安全性的要求,也即确保只有获得授权的人员的允许才可以对固态硬盘中的数据进行访问,对于非法使用者则应拒绝其访问请求。目前采用的一种安全访问方式是采用固定的授权码、固定的系统id(identity document,身份标识号)值,其安全性较差,无法抵抗“重放攻击”,只要攻击者能够采用非法手段监测到1次正常的访问过程,之后采用相同的授权码、相同的id值,即可骗过固态硬盘的安全系统,实现破解。

3.因此,目前需要一种能够较好的抵抗“重放攻击”的访问控制方式。

技术实现要素:

4.鉴于上述问题,本实用新型提出了一种固态硬盘及固态硬盘访问控制系统,可有效抵抗“重放”攻击,提高固态硬盘的数据安全性。

5.第一方面,本技术通过一实施例提供如下技术方案:

6.一种固态硬盘,包括:被配置为存储原始密钥的密钥存储器;密钥读取控制电路;被配置为产生随机数的随机数发生器;被配置为接收访问硬盘的主机的序列号的第一输入控制电路;被配置为基于所述原始密钥和主机的序列号进行哈希计算获得第一摘要值,以及被配置为基于所述第一摘要值和所述随机数进行哈希计算获得第二摘要值的摘要值计算电路;被配置为接收访问硬盘得主机输入的基于所述第一摘要值和所述随机数进行哈希计算获得的第三摘要值的第二输入控制电路;被配置为比较所述第二摘要值和所述第三摘要值是否相同的比较电路;被配置为向主机输出所述随机数的输出控制电路以及接口电路;所述密钥存储器与所述密钥读取控制电路连接;所述密钥读取控制电路、所述第一输入控制电路以及所述随机数发生器均与所述摘要值计算电路连接;所述摘要值计算电路和所述第二输入控制电路均与所述比较电路连接;所述输出控制电路与所述随机数发生器连接;所述接口电路与所述比较电路控制连接。

7.可选的,所述摘要值计算电路包括:被配置为基于所述原始密钥和所述序列号进行哈希计算获得第一摘要值的第一杂凑算法电路;和被配置为基于所述第一摘要值和所述随机数进行哈希计算获得第二摘要值的第二杂凑算法电路;

8.所述第一杂凑算法电路的输入端连接所述密钥读取控制电路和所述第一输入控制电路;所述第一杂凑算法电路的输出端连接所述第二杂凑算法电路的输入端,所述第二杂凑算法电路的输入端还连接随机数发生器;所述第二杂凑算法电路的输出端连接所述比

较电路的输入端。

9.可选的,还包括第一缓存寄存器,所述第一杂凑算法电路通过所述第一缓存寄存器与所述第二杂凑算法电路连接。

10.可选的,所述摘要值计算电路包括:第一选择器、第二选择器、第三选择器和第三杂凑算法电路;所述第一选择器的第一输入端连接所述密钥读取控制电路,所述第一选择器的第二输入端连接所述第三选择器第一输出端,所述第一选择器的输出端连接所述第三杂凑算法电路的输入端;所述第二选择器的第一输入端连接所述第一输入控制电路,所述第二选择器的第二输入端连接所述随机数发生器,所述第二选择器的输出端连接所述第三杂凑算法电路的输入端;所述第三杂凑算法电路的输出端连接所述第三选择器的输入端;所述第三选择器的第二输出端连接所述比较电路的输入端。

11.可选的,还包括第二缓存寄存器,所述第三杂凑算法电路通过所述第二缓存寄存器与所述第三选择器连接。

12.可选的,还包括被配置为向所述密钥存储器中写入原始密钥的密钥写入控制电路;所述密钥写入控制电路连接所述密钥存储器。

13.可选的,还包括主控状态机;所述主控状态机分别与所述密钥存储器、所述密钥读取控制电路、所述摘要值计算电路、所述第一输入控制电路、所述随机数发生器、所述第二输入控制电路以及所述比较电路控制连接。

14.可选的,所述接口电路为pcie接口电路和/或sata接口电路。

15.可选的,还包括闪存控制器和闪存阵列;所述闪存控制器和所述闪存阵列控制连接。

16.第二方面,基于同一发明构思,本技术通过一实施例提供如下技术方案:

17.一种固态硬盘访问控制系统,包括:主机和前述第一方面中所述的固态硬盘;所述固态硬盘包括接口电路,所述接口电路与所述比较电路连接;所述主机包括被配置为存储序列号和第一摘要值的序列号存储器;以及被配置为基于所述第一摘要值和所述随机数进行哈希计算获得第三摘要值的第四杂凑算法电路和输出接口电路;

18.所述序列号存储器分别与所述第一输入控制电路和所述第四杂凑算法电路连接,所述第四杂凑算法电路与所述输出接口电路连接,所述输出接口电路与所述第二输入控制电路连接。

19.在本实用新型实施例中的一种固态硬盘及固态硬盘访问控制系统,其中增加了随机数发生器,即使攻击者破解了某一次的随机数,也难以在下一次的验证过程中通过验证,因为每次的随机数均是不相同的;另外,本实施例中在进行摘要值计算时是将原始密钥和主机的序列号进行一次摘要值计算,得到第一摘要值;然后,再将第一摘要值和随机数进行一次摘要值计算,用于比对验证的第二摘要值;这样可将主机的特征涵盖到第二摘要值中。即使攻击者破解了用于验证的某一主机后可伪造该序列号的主机,也可在固态硬盘端配置将该主机的序列号加入黑名单,从而避免风险扩散,提高固态硬盘数据的安全性。

20.上述说明仅是本实用新型技术方案的概述,为了能够更清楚了解本实用新型的技术手段,而可依照说明书的内容予以实施,并且为了让本实用新型的上述和其它目的、特征和优点能够更明显易懂,以下特举本实用新型的具体实施方式。

附图说明

21.通过阅读下文优选实施方式的详细描述,各种其他的优点和益处对于本领域普通技术人员将变得清楚明了。附图仅用于示出优选实施方式的目的,而并不认为是对本实用新型的限制。而且在整个附图中,用相同的参考符号表示相同的部件。在附图中:

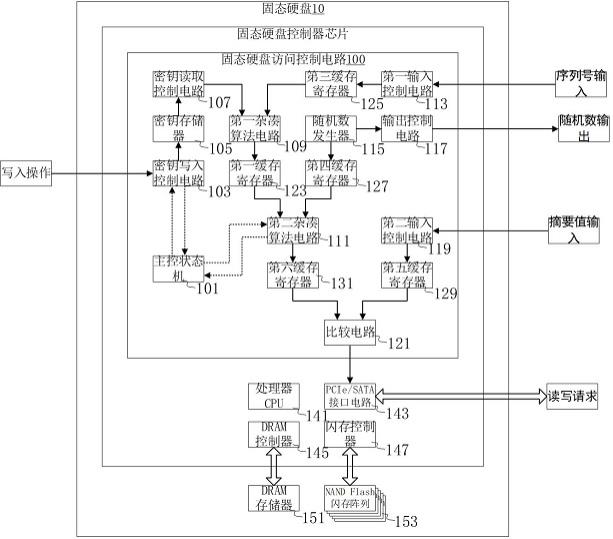

22.图1为本实用新型实施例中的一固态硬盘访问控制电路的结构示意图;

23.图2为本实用新型实施例中的又一固态硬盘访问控制电路的结构示意图;

24.图3为本实用新型实施例中的固态硬盘的结构示意图;

25.图4为本实用新型实施例中的固态硬盘访问控制系统的结构示意图;

26.图5为本实用新型实施例中的固态硬盘访问控制系统的认证交互原理示意图。

27.附图标记:

28.10-固态硬盘;100-固态硬盘访问控制电路;300-固态硬盘访问控制系统;20-主机;101-主控状态机;103-密钥写入控制电路;105-密钥存储器;107-密钥读取控制电路;109-第一杂凑算法电路;111-第二杂凑算法电路;113-第一输入控制电路;115-随机数发生器;117-输出控制电路;119-第二输入控制电路;121-比较电路;123-第一缓存寄存器;125-第三缓存寄存器;127-第四缓存寄存器;129-第五缓存寄存器;131-第六缓存寄存器;112-第一选择器;114-第二选择器;116-第三选择器;118-第三杂凑算法电路;120-第二缓存寄存器;141-处理器;143-接口电路;145-dram控制器;147-闪存控制器;151-dram存储器;153-闪存阵列;201-序列号存储器;203-第四杂凑算法电路;205-输出接口电路;207-第七缓存寄存器。

具体实施方式

29.下面将参照附图更详细地描述本公开的示例性实施例。虽然附图中显示了本公开的示例性实施例,然而应当理解,可以以各种形式实现本公开而不应被这里阐述的实施例所限制。相反,提供这些实施例是为了能够更透彻地理解本公开,并且能够将本公开的范围完整的传达给本领域的技术人员。

30.请参阅图1,本实用新型实施例中提供了一种固态硬盘访问控制电路100,包括:密钥存储器105、密钥读取控制电路107、摘要值计算电路、第一输入控制电路113、随机数发生器115、第二输入控制电路119以及比较电路121;密钥存储器105与密钥读取控制电路107连接;密钥读取控制电路107、第一输入控制电路113以及随机数发生器115均与摘要值计算电路连接;摘要值计算电路和第二输入控制电路119均与比较电路121连接。

31.密钥存储器105,被配置为存储原始密钥;第一输入控制电路113,被配置为接收访问硬盘的主机的序列号;随机数发生器115,被配置为产生随机数;摘要值计算电路,被配置为基于原始密钥和序列号进行哈希计算,获得第一摘要值;还被配置为基于第一摘要值和随机数进行哈希计算,获得第二摘要值;第二输入控制电路119,被配置为接收访问硬盘得主机输入的第三摘要值;第三摘要值为基于第一摘要值和随机数进行哈希计算获得的;比较电路121,被配置为比较第二摘要值和第三摘要值是否相同;还被被配置为,若第二摘要值和第三摘要值相同,则输出认证通过的信号,以使硬盘响应主机的读写请求;若第二摘要值和第三摘要值不同,则输出认定失败的信号以使硬盘不响应主机的读写请求。

32.可以理解的是,在本实施例中增加了随机数发生器115,即使攻击者破解了某一次

的随机数,也难以在下一次的验证过程中通过验证,因为每次的随机数均是不相同的;另外,本实施例中在进行摘要值计算时是将原始密钥和主机的序列号进行一次摘要值计算,得到第一摘要值;然后,再将第一摘要值和随机数进行一次摘要值计算,用于比对验证的第二摘要值;这样可将主机的特征涵盖到第二摘要值中。即使攻击者破解了用于验证的某一主机后可伪造该序列号的主机,也可在硬盘端配置将该主机的序列号加入黑名单,从而避免风险扩散,提高硬盘数据的安全性。

33.在一些可选的实现方式中摘要值计算电路包括:第一杂凑算法电路109和第二杂凑算法电路111;第一杂凑算法电路109的输入端连接密钥读取控制电路107和第一输入控制电路113;第一杂凑算法电路109的输出端连接第二杂凑算法电路111的输入端,第二杂凑算法电路111的输入端还连接随机数发生器115;第二杂凑算法电路111的输出端连接比较电路121的输入端;第一杂凑算法电路109,被配置为基于原始密钥和序列号进行哈希计算,获得第一摘要值;第二杂凑算法电路111,被配置为基于第一摘要值和随机数进行哈希计算,获得第二摘要值。

34.在该实现方式中,还可设置第一缓存寄存器123来临时存储第一杂凑算法电路109的计算得到的第一摘要值。也就是说,第一杂凑算法电路109通过第一缓存寄存器123与第二杂凑算法电路111连接。

35.可以理解的,本实施例中的摘要值即为hash(哈希)值;杂凑算法也称之为“摘要算法”、“哈希算法”,其计算结果为一个hash值,即“摘要值”,常见的杂凑算法有:sha1、sha3、sha256、sm3、md5、等等。主机可以是个人计算机(pc),序列号可以是主机的唯一识别号,例如主板的序列号,网卡的物理地址,pc的出厂序列号,操作系统的授权号,等等。

36.进一步的,当在摘要值计算电路中采用两个杂凑算法电路实现时,虽然能够生成第二摘要值,但是会导致占用大量的电路面积,不利用更小尺寸的硬盘设计,因此,本实施例中还提供了一个杂凑算法电路的电路设计;具体的:

37.请参阅图2,该摘要值计算电路可包括:第一选择器112、第二选择器114、第三选择器116和第三杂凑算法电路118;第一选择器112的第一输入端连接密钥读取控制电路107,第一选择器112的第二输入端连接第三选择器116第一输出端,第一选择器112的输出端连接第三杂凑算法电路118的输入端;第二选择器114的第一输入端连接第一输入控制电路113,第二选择器114的第二输入端连接随机数发生器115,第二选择器114的输出端连接第三杂凑算法电路118的输入端;第三杂凑算法电路118的输出端连接第三选择器116的输入端;第三选择器116的第二输出端连接比较电路121的输入端。第一选择器112,被配置为在第一时段选择原始密钥输出至第三杂凑算法电路118;第二选择器114,被配置为在第一时段选择序列号输出至第三杂凑算法电路118;第三杂凑算法电路118,被配置为基于原始密钥和随机数进行哈希计算,获得第一摘要值;第三选择器116,被配置为将第一摘要值输出给第一选择器112;第一选择器112,还被配置为在第二时段选择第一摘要值输出至第三杂凑算法电路118;第二选择器114,还被配置为在第二时段选择随机数输出至第三杂凑算法电路118;第三杂凑算法电路118,还被配置为基于第一摘要值和随机数进行哈希计算,获得第二摘要值;第三选择器116,还被配置为将第二摘要值输出给比较电路121。本实施例中的选择器电路可采用现有的逻辑电路实现,不做限制。

38.可以理解的,通过时序控制信号分别控制第一选择器112、第二选择器114和第三

选择器116。在第一时段向第三杂凑算法电路118输入原始密钥和序列号即可计算获得第一摘要值;然后,在第二时段向第三杂凑算法电路118输入随机数和第一摘要值,即可计算获得第二摘要值。该设计仅仅增加时序控制,有效的减少了电路硬件,缩减了整体电路面积,降低了成本。

39.进一步的,该固态硬盘访问控制电路100还可包括第二缓存寄存器120,第三杂凑算法电路118通过第二缓存寄存器120与第三选择器116连接。第二缓存寄存器120可临时存储第三杂凑算法电路118计算得到的第二摘要值。

40.在本实施例中的固态硬盘访问控制电路100,还可包括密钥写入控制电路103;密钥写入控制电路103连接密钥存储器105;密钥写入控制电路103被配置为向密钥存储器105中写入原始密钥。在一些情况下,还可由管理员通过密钥写入控制电路103向密钥存储器105中写入新的原始密钥以更换原来的原始密钥,防范原始密钥泄露风险。本实施例中的密钥存储器105可为eeprom(electrically erasable programmable read only memory,带电可擦可编程只读存储器)。

41.另外,在该固态硬盘访问控制电路100还可包括第三缓存寄存器125和第四缓存寄存器127;第一输入控制电路113通过第三缓存寄存器125与摘要值计算电路连接;该第三缓存寄存器125可被配置为临时存储第一输入控制电路113传入的序列号,在摘要值计算电路需要使用时传入摘要值计算电路,或由摘要值计算电路调用。随机数发生器115通过第四缓存寄存器127与摘要值计算电路连接;该第四缓存寄存器127被配置为临时存储随机数发生器115产生的随机数,以便在摘要值计算电路需要使用时传入摘要值计算电路,或由摘要值计算电路调用。

42.进一步,该固态硬盘访问控制电路100还可包括第五缓存寄存器129和第六缓存寄存器131,第二输入控制电路119通过第五缓存寄存器129与比较电路121连接;第五缓存寄存器129被配置为临时存储主机一侧传入的第三摘要值,摘要值计算电路可通过第六缓存寄存器131与比较电路121连接,可被配置未缓存摘要值计算电路的处理得到的第二摘要值,以便于比较电路121实现对第二摘要值和第三摘要值的比较。

43.该固态硬盘访问控制电路100还可包括主控状态机101,主控状态机101分别与密钥存储器105、密钥读取控制电路107、摘要值计算电路、第一输入控制电路113、随机数发生器115、第二输入控制电路119、比较电路121控制连接、密钥写入控制电路103以及各个缓存寄存器中的任一个或多个控制连接;在附图中仅示出主控状态机101与密钥写入控制电路103及第二杂凑算法电路111之间的控制连接关系,其他部分未示出。以实现对整个电路的完整工作流程进行控制。例如,随机数发生器115可在主控状态机101的控制下生成随机数。

44.可以理解的,比较电路121所输出的信号可传送至硬盘的接口电路143以使接口电路143响应或不响应主机的读写请求。另外,比较电路121还可所输出的信号还可传送给主控状态机101,由主控状态机101控制接口电路143是否响应主机。

45.该固态硬盘访问控制电路100还可包括输出控制电路117,该输出控制电路117的输入端与随机数发生器115连接,输出控制电路117的输出端被配置为将随机数发生器115产生的随机数输出给对应的主机一侧。

46.请参阅图3,基于同一发明构思,在本实用新型的又一实施例中还提供了一种固态硬盘10,该固态硬盘10包括:前述实施例中任一的固态硬盘访问控制电路100。

47.该固态硬盘10还可包括处理器141、接口电路143、dram控制器145、闪存控制器147以及闪存阵列153;其中,接口电路143可以是pcie接口、sata接口、pci接口等,不做限制;dram控制器145可与dram存储器151控制连接,闪存控制器147可与闪存阵列153控制连接;闪存阵列153可为nand flash闪存阵列。可以理解的,该接口电路143可属于固态硬盘10的控制器芯片部分,固态硬盘10的控制器芯片部分可包括处理器(cpu)141、dram(dynamic random access memory,动态随机存取存储器)控制器、闪存控制器147;另外,固态硬盘10的存储部分可包括dram存储器151和闪存阵列(如nand flash闪存阵列),不做限制。上述未作详细说明的结构均为本领域技术人员所了解的现有技术。例如,处理器141、闪存控制器147以及dram控制器145等可参见机械工业出版社《深入浅出ssd》一书中进行具体实现,本实施例中不再赘述。

48.需要说明的是,本实施例中的固态硬盘10其采用了前述实施例中的固态硬盘访问控制电路100,其所具备的有益效果可参照前述实施例中关于固态硬盘访问控制电路100的阐述,本实施例中不再赘述。

49.请参阅图4,基于同一发明构思,本实用新型实施例中提供的一种固态硬盘访问控制系统300,包括:主机20和前述实施例中的固态硬盘10;固态硬盘10包括接口电路143,接口电路143与比较电路121连接;主机20包括序列号存储器201、第四杂凑算法电路203和输出接口电路205;序列号存储器201分别与第一输入控制电路113和第四杂凑算法电路203连接,第四杂凑算法电路203与输出接口电路205连接,输出接口电路205与第二输入控制电路119连接;序列号存储器201,被配置为存储序列号和第一摘要值;第四杂凑算法电路203,被配置为基于第一摘要值和随机数进行哈希计算,获得第三摘要值。进一步的,第四杂凑算法电路203可通过第七缓存寄存器207与输出接口电路205连接。

50.若攻击者窃取了第一摘要值后也无法获取随机数,并且即使窃取了主机20一侧的第一摘要值,由于第一摘要值是通过原始密钥和序列号哈希计算获得的,管理员也可通过调整固态硬盘10一侧的原始密钥来使被窃取的第一摘要值无效,从而保证固态硬盘10的安全性。

51.在主机20一侧,为保证计算结果一致性,第四杂凑算法电路203应当与第二杂凑算法电路111及第三杂凑算法电路118相同。

52.请参阅图5,下面以一具体示例方式对本实用新型的固态硬盘访问控制电路100、系统300及固态硬盘10的原理进行说明:

53.对固态硬盘10进行应用部署之前,先进行初始化操作;首先,构造1个原始密钥(root key),将之写入固态硬盘10的密钥存储器105(eeprom存储器)。接着,用户为每台主机20(计算机)指定1个序列号(serial number),不同主机20的序列号各不相同。再接着,用户将序列号写入主机20内的序列号存储器201中(eeprom存储器)。

54.对于每个序列号(serial number),都将其与原始密钥(root key)结合,使用摘要算法进行运算,其结果即为多元密钥(diversified key),若主机20与固态硬盘10匹配的情况下,该多元密钥为第一摘要值;由于每台计算机的序列号(serial number)都不同,所以各台计算机的多元密钥(diversified key)也不同。将各多元密钥(diversified key)写入相应每台主机20的序列号存储器201中。

55.进一步的,将固态硬盘10部署至主机20中,需要对其进行认证授权;若是“非法”主

机20,则无法完成认证流程,固态硬盘10不会响应pc的数据读写访问;若是“合法”主机20,则能够通过认证流程,主机20可以正常读写固态硬盘10。认证授权的流程如下:

56.认证开始,固态硬盘10内部的主控状态机101控制密钥读取控制电路107读取密钥存储器105中的原始密钥(root key);接着,从计算机端读取到密钥存储器105中保存的序列号(serial number);并控制摘要值计算电路对原始密钥(root key)和序列号(serial number)做杂凑运算,计算结果即为第一摘要值;如果是“合法”主机20,则此第一摘要值与计算机中序列号存储器201中的多元密钥(diversified key)数值完全相同。

57.接着,固态硬盘10内部的随机数生成器生成1个随机数a,将之作为challenge,送给pc端;固态硬盘10基于随机数a和第一摘要值启动杂凑算法电路,算出第二摘要值c。

58.主机20一侧收到随机数a后,结合其内部序列号存储器201中的多元密钥(diversified key)调用杂凑算法,算出第三摘要值d。主机20将第三摘要值d输出给固态硬盘10一侧;固态硬盘10收到第三摘要值d后,将第三摘要值d与第二摘要值c进行比较。如果第二摘要值和第三摘要值相同,说明主机20是“合法”的,则开启通信接口(如:pcie、sata或pci),并允许主机20对固态硬盘10中的数据进行访问;反之,说明主机20为非法主机,则将通信接口停用,不响应主机20的固态硬盘10读写访问请求。

59.通过上述例子可以看出,要认证成功必须保证在主机20端存储有与固态硬盘10计算得到的相同的第一摘要值;但第一摘要值的计算仅仅只在固态硬盘10中存在,主机20一侧的第一摘要值是预设存入的,因此,仅仅从主机20一侧难以实现破解;进一步提高了安全性。其次,要实现破解还必须每次都能够确定随机数发生器115产生的随机数;但是随机数每次认证过程都是不同的,而且是由固态硬盘10发出,即使拦截到任一次认证过程的随机数,都是无法实现破解的;即使,得到相同的随机数生成器,在固态硬盘10还可通过黑名单的方式来添加恶意主机。黑名单可通过密钥写入控制电路103写入到密钥存储器105中,黑名单识别的实现可通过第一输入控制电路113和主控状态机101来识别,例如主控状态机101判断第一输入控制电路113接收到的序列号存在于黑名单上,则控制第一输入控制电路113不再写入第三缓存寄存器125中,从而防止攻击,进一步提高固态硬盘10的安全性。因此,本实施例中的固态硬盘访问控制电路100、系统300及固态硬盘10能够有效的抵抗“重放”攻击,保障固态硬盘10的数据安全性。

60.在此处所提供的说明书中,说明了大量具体细节。然而,能够理解,本实用新型的实施例可以在没有这些具体细节的情况下实践。在一些实例中,并未详细示出公知的方法、结构和技术,以便不模糊对本说明书的理解。

61.类似地,应当理解,为了精简本公开并帮助理解各个实用新型方面中的一个或多个,在上面对本实用新型的示例性实施例的描述中,本实用新型的各个特征有时被一起分组到单个实施例、图、或者对其的描述中。然而,并不应将该公开的方法解释成反映如下意图:即所要求保护的本实用新型要求比在每个权利要求中所明确记载的特征更多的特征。更确切地说,如下面的权利要求书所反映的那样,实用新型方面在于少于前面公开的单个实施例的所有特征。因此,遵循具体实施方式的权利要求书由此明确地并入该具体实施方式,其中每个权利要求本身都作为本实用新型的单独实施例。

62.本领域那些技术人员可以理解,可以对实施例中的装置中的模块进行自适应性地改变并且把它们设置在与该实施例不同的一个或多个装置中。可以把实施例中的模块或单

元或组件组合成一个模块或单元或组件,以及此外可以把它们分成多个子模块或子单元或子组件。除了这样的特征和/或过程或者单元中的至少一些是相互排斥之外,可以采用任何组合对本说明书(包括伴随的权利要求、摘要和附图)中公开的所有特征以及如此公开的任何方法或者设备的所有过程或单元进行组合。除非另外明确陈述,本说明书(包括伴随的权利要求、摘要和附图)中公开的每个特征可以由提供相同、等同或相似目的的替代特征来代替。

63.此外,本领域的技术人员能够理解,尽管在此的一些实施例包括其它实施例中所包括的某些特征而不是其它特征,但是不同实施例的特征的组合意味着处于本实用新型的范围之内并且形成不同的实施例。例如,在下面的权利要求书中,所要求保护的实施例的任意之一都可以以任意的组合方式来使用。

64.应该注意的是上述实施例对本实用新型进行说明而不是对本实用新型进行限制,并且本领域技术人员在不脱离所附权利要求的范围的情况下可设计出替换实施例。在权利要求中,不应将位于括号之间的任何参考符号构造成对权利要求的限制。单词“包含”不排除存在未列在权利要求中的部件或步骤。位于部件之前的单词“一”或“一个”不排除存在多个这样的部件。本实用新型可以借助于包括有若干不同部件的硬件以及借助于适当编程的计算机来实现。在列举了若干装置的单元权利要求中,这些装置中的若干个可以是通过同一个硬件项来具体体现。单词第一、第二、以及第三等的使用不表示任何顺序。可将这些单词解释为名称。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1