一种高集成处理系统的制作方法

1.本技术涉及嵌入式硬件技术,尤其涉及一种高集成处理系统。

背景技术:

2.在嵌入式硬件设计领域,常常需要对处理器芯片进行资源开发。目前的处理系统,一方面存在接口及功能单一的问题,另一方面未能更大程度的提高集成度,对处理器芯片的引脚复用资源不能实时进行开发,若要完全开发处理器芯片的功能,会增加板卡搭建的复杂度和成本,不利于芯片量产后的自动化测试,同时也不利于小体积的集成化趋势。

技术实现要素:

3.为了解决上述现有技术的不足,本技术提供一种高集成处理系统,在板卡上集成处理器芯片及多种接口,并搭建芯片引脚分时复用的硬件结构,提高处理系统的集成度,更加利于开发者进行芯片资源的开发应用。

4.为了实现上述目的,本实用新型采用以下技术:

5.一种高集成处理系统,包括设于板卡上的:

6.处理器芯片;

7.供电电路,与处理器芯片连接,用于将外部输入的直流电压转为处理器芯片工作电压;

8.nand flash,连接第一模拟开关,第一模拟开关连接处理器芯片,用于扩展处理器芯片的储存器接口功能;

9.以太网接口,连接phy芯片,phy芯片连接第一模拟开关,第一模拟开关的控制由处理器芯片的gipo口控制,用于实现nand flash和以太网接口的切换;

10.第一晶振和第二晶振,均连接第二模拟开关,第一晶振用于给以太网mii接口提供时钟,第二晶振用于给以太网rmii接口提供时钟,第二模拟开关连接处理器芯片,第二模拟开关的控制由处理器芯片的gipo口控制,用于实现以太网mii和rmii时钟的切换,从而实现mii接口和rmii接口功能的分时复用;

11.运放,与处理器芯片连接,并连接有sma接口,用于将处理器芯片的dac信号放大后输出;

12.电流采集芯片,与处理器芯片连接,用于进行adc采样,采集处理器芯片的io电和内核电,以获得处理器芯片的实时功耗。

13.处理器芯片为m2018芯片。

14.供电电路包括dcdc降压芯片,用于将外部输入的5v~12v转换为3.3v和1.2v提供给处理器芯片。

15.处理器芯片连接有复位芯片,复位芯片连接复位按键电路。复位芯片采用max706。

16.本实用新型有益效果在于:

17.1、在板卡上集成处理器芯片及多种接口,并搭建芯片引脚分时复用的硬件结构,

提高处理系统的集成度,更加利于开发者进行芯片资源的开发应用;

18.2、通过m2018芯片的gpio实现对第一模拟开关和第二模块开关的切换控制,对以太网和nand flash接口的复用,以及以太网mii和rmii接口功能的分时复用;

19.3、为m2018芯片搭建了dac信号输出和adc采样电路,可实现对m2018 io和内核电流采样和对dac信号的输出,提高了系统的功能性;其中,通过运放及sma实现dac信号输出,便于确保输出信号的有效性和稳定性,同时利用负压供电方式提供给运放,利于实现0v-3.3v的模拟量输出。

附图说明

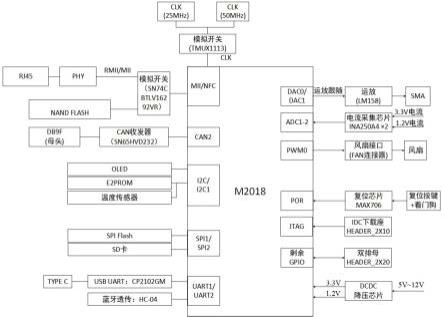

20.图1是本技术实施例的处理系统一种示例的硬件电路结构图。

21.图2是本技术实施例的处理系统dac信号输出电路结构示例。

22.图3是本技术实施例的处理系统dac信号输出电路的负压供电电路结构示例。

具体实施方式

23.为使本实用新型实施例的目的、技术方案和优点更加清楚,下面结合附图对本实用新型的实施方式进行详细说明,但本实用新型所描述的实施例是本实用新型一部分实施例,而不是全部的实施例。

24.m2018芯片是一种基于cortex-m4f内核的多用途mcu处理器芯片。cortex-m4是一款高性能的处理器核,拥有三级流水线设计的哈佛总线架构,尤其适合用来处理要求高的嵌入式应用程序。本技术实施例针对m2018芯片提供一种高集成处理系统。

25.本示例的处理系统包括设于板卡的m2018芯片,并以m2018芯片为核心搭建供电、电流采集、时钟、复位、jtag、以太网接口、nand flash接口、can接口、spi接口、usb接口、iic接口、gpio接口、蓝牙、sd卡等。

26.具体的,如图1所示,供电电路采用dcdc降压芯片tps563201,其与m2018芯片连接,用于进行电压转换,将输入的5v~12v供电转化为3.3v和1.2v提供给m2018芯片。

27.电流采集采用两个电流采集芯片ina250a4芯片和两个sma接口搭建,两个ina250a4芯片连接处理器芯片,并分别连接一个sma接口,用于进行adc采样。一路用于采集1.2v电流,一路用于采集3.3v电流。

28.m2018芯片的dac0/dac1端口连接运放lm158,运放lm158连接有sma接口。dac信号通过运放lm158和sma接口引出。如图2所示为一种dac信号输出的电路结构示例,其中,运放lm158的同相输入通过电阻r35连接m2018芯片,反相输入端通过电阻r37连接到运放lm158的输出端,电阻r37两端并联有电容c46。运放lm158的输出端连接电阻r36,电阻r36连接电容c44和sma接口,电容c44连接agnd。运放lm158的v+连接+12va和电容c40,电容c40连接agnd,运放lm158的v-连接-12va和电容c43,电容c43连接agnd。考虑到运放不是轨到轨的运放,设计负压供电,以便实现0v-3.3v的模拟量输出,可采用如图3所示的负压供电电路,采用lt1931es5搭建。

29.复位采用复位芯片/看门狗芯片max706搭建,max706连接m2018芯片并连接复位按键。max706对m2018芯片的状态进行检测,当max706没有定期被喂狗时,复位m2018。另外,m2018的gpio可以通过max706对m2018进行软复位。

30.时钟电路采用第一晶振(25mhz)和第二晶振(50mhz),通过第二模拟开关连接到m2018芯片。可选的,第二模拟开关可以采用tmux1113,带宽为400mhz,由m2018芯片的gipo口控制,用于实现25mhz和50mhz时钟的切换,从而实现mii接口和rmii接口功能的分时复用。

31.m2018芯片连接第一模拟开关,第一模拟开关连接nand flash和phy芯片,phy芯片连接以太网接口(rj45)。第一模拟开关的控制由处理器芯片的gipo口控制,用于实现nand flash和以太网接口的切换。可选的,第一模拟开关采用sn74cbtlv16292vr,带宽为200mhz,满足以太网接口信号对带宽的要求。

32.本实例中,m2018芯片的jtag接口连接idc下载座,其中idc下载座可以采用20 pin的牛角座。

33.本实例中,m2018芯片的can接口连接can收发器,can收发器连接db9f母头。其中,可选的,can收发器可采用sn65hvd232qd。

34.本实例中,m2018芯片通过spi接口连接有sd卡和spi flash。m2018芯片通过spi接口与sd卡和/或spi flash进行数据交换。

35.本实例中,m2018芯片的usb接口采用usb转uart的方式进行uart通信,具体的,m2018芯片通过第一路uart接口连接电平转换芯片cp2102,电平转换芯片cp2102连接usb接口,usb接口可以采用type-c。

36.m2018芯片连接有蓝牙透传模块hc-04。本实例中,通过第二路uart接口连接,进行串口通信。

37.本实例中,m2018芯片通过pwm端口连接风扇接口/fan连接器,风扇接口用于连接风扇。风扇的控制采用pwm控制,转速信号返回m2018芯片的gpio口进行检测。

38.m2018芯片通过一路i2c接口连接有温度传感器,实现温度信号的传输与处理。

39.m2018芯片还通过另一路i2c接口连接有oled屏模块和e2prom。一方面可以通过i2c存储数据到e2prom,另一方面可以外部与m2018的通信结果在oled屏上显示。

40.m2018芯片的剩余gipo口通过双排母连出。

41.以上所述仅为本技术的优选实施例,并不用于限制本技术,显然,本领域的技术人员可以对本技术进行各种改动和变型而不脱离本技术的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1