高深宽比结构的分割或横截面的制作方法

本发明关于一种通过集成电路横截面成像的三维电路图案检查和测量技术。更具体地,本发明关于获得集成半导体样本之内通道或高深宽比(har)结构的3d体积图像的方法、以及关于对应计算机程序产品和对应半导体检查装置。该方法、计算机程序产品和装置可用于通过使用扫描带电粒子显微镜,对集成半导体样本内通道或har结构的形状或横截面、倾斜或轨迹,进行定量计量、缺陷检测、缺陷审查和检查。

背景技术:

1、半导体结构是最精细的人造结构之一,仅存在极少数的不完美。这些罕见的不完美是缺陷检测、缺陷审查或定量计量装置正在寻找的特征。

2、制造的半导体结构基于先前知识。例如,在逻辑类型样本中,金属线平行于金属层或高深宽比(har)结构,或金属通孔垂直于金属层。不同层中金属线之间的角度为0°或90°。另一方面,对于vnand类型的结构,已知其横截面平均为球形。

3、集成半导体通过平面集成技术处理硅基板上一系列层来制造,每层首先平面化,然后通过投射曝光装置在光刻制程内由图案结构化。光刻图案通过多种技术转移到硅层中,包括蚀刻、沉积、掺杂或植入。图1中显示横截面垂直于一组层。集成半导体50包含一组层54.1、54.2、……54.22,其通过平行于在x-y方向延伸的顶面52的平面集成技术来制造。在最下层54.22之外是半导体基板或晶片的硅块材基板51,其并未显示出其整个深度。最下层54.22是在硅基板中通过例如植入形成掺杂结构58的层。在此层的顶部上,由诸如金属层54.1、54.3、…54.17…的金属导体构成的一系列所谓金属层与诸如隔离层54.2、54.4…的一系列隔离层交替。隔离层包含互接,以接触两相邻金属层,诸如金属层54.1中的金属结构56与金属层54.3中的金属结构之间的通孔55。最下金属层包含在相邻隔离层中具有触点59的一系列栅极57。

4、随着z方向深度增加,所述层中的最小特征尺寸变得更小。最下、最关键层的当前最小特征尺寸或关键尺寸实际上低于10nm,例如7nm或5nm,并在不久的将来接近3nm以下。随着最小特征尺寸的小幅扩展,所述层在x和y方向的横向放置要求变得越来越苛刻。两层的横向叠加精度通常为两层中最小特征尺寸的1/3的数量级。因此,最下层的横向排列必须在数纳米大小内,并在不久的将来甚至低于1nm。

5、图2显示贯穿半导体装置(诸如nand存储器装置)的横截面的另一范例。在此范例中,数个柱(诸如由参考编号60指出的三个柱)延伸穿过一大组金属和隔离层54.1、…54.k、…54.z,并建立垂直于所述层的导电连接。柱60也称为har(高深宽比)结构,或有时称为接触通道。虽然金属层内平行于表面52的金属结构利用高精度平面制造技术一次性制造,但柱60在每个后续层中由彼此堆叠于顶部的大系列或小金属结构形成。因此,柱可能遭受若干损坏,因此变成各个平面层制程中的错误以及后续平面层之间的重叠错误。然而,柱内的错误或缺陷限制了半导体装置的性能,或可能导致此装置故障。一种柱为3d存储器芯片中的所谓存储器通道。

6、用于分析集成半导体装置的现有技术目前正使用2d成像方式。例如,例如通过离子束磨削由半导体装置形成薄片或薄膜,并且通过探针提取薄样本。薄膜可为所谓的“平面视图”或“横截面视图”样本,其可为平行或垂直的集成半导体装置。薄膜由例如扫描电子显微镜(sem或stem)或透射式电子显微镜(tem)进一步分析。此方法需要去除通道或柱前后的材料,这可能导致测量不精确。柱、孔或通道的部分可已从薄片移除,并且从成像薄膜中遗失。

7、另一方法是生成平行或垂直于集成半导体装置的单一相交平面的2d图像,其通过使用相交光束或双光束装置进行磨削和成像来生成。然而,如前述,将har柱或孔或通道制造成具有不始终可预测或已知的形状。其可扭曲和弯曲并延伸到平面2d相交点之外。2d技术无法捕捉这些结构的真实路径或轨迹,以及这些结构的形状特性,因为har柱或孔或通道可不限于平面相交平面。接下来,用于2d成像的横截面表面可通过称为垂幕(curtaining)的效果退化,使得横截面表面显示一些波纹,并且2d图像可能仅包含半导体结构的一部分。2d成像方法仅捕获其形状的一部分,其中该部分与成像表面或薄片体相交。

8、最近,引入了3d体积图像生成。3d体积图像经由横截面成像技术生成,其利用带电粒子束系统对集成半导体进行切片和成像,以确定集成半导体内预定体积的3d体积图像。此横截面成像技术包括大量2d横截面图像的生成和储存,以及2d横截面图像在体积内的配准,以生成高精度的3d体积图像。带电粒子系统可包含用于成像的电子显微镜(sem)和用于切片的聚焦离子束系统(fib)、或用于切片和成像的离子束系统。

9、因此,确定柱或孔的错误或缺陷或结构的偏差(包括柱的内部结构)是一问题。尤其是,存储器通道和类似的柱可具有内部子结构,例如在横截面中呈现出数个同心环。采用允许确定错误或缺陷的方式以自动识别此类子结构是一项挑战。

技术实现思路

1、本发明的一目的为提供一种识别har结构柱横截面中的子结构的改良方法,例如在获得柱或har结构的3d体积图像的背景下。在一些具体实施例中,该方法允许通过一系列横截面图像对柱或har结构进行准确的3d重建。

2、具体实施例使用一训练过的机器学习逻辑以识别柱横截面中的子结构,尤其是环。第一方面关于训练此机器学习逻辑。

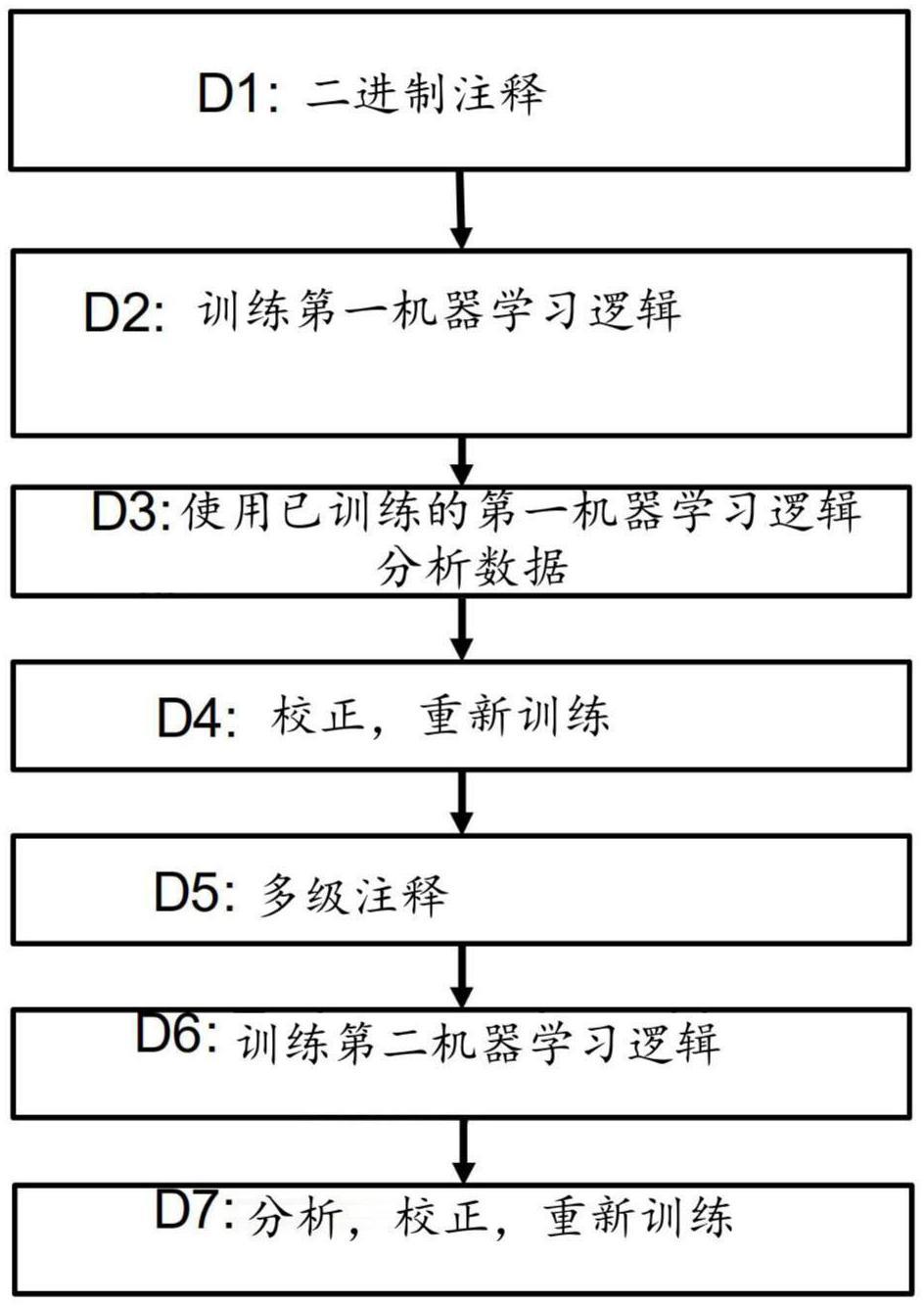

3、根据一具体实施例,提供一种训练机器学习逻辑以分割高深宽比har结构的柱横截面环的方法,该方法包含:

4、提供多个柱的横截面图像;

5、以两个交替标签对横截面图像中的环进行二进制注释;

6、基于所述二进制注释的环训练第一机器学习逻辑;

7、使用训练过的第一机器学习逻辑分割横截面图像或进一步横截面图像,以提供二进制分割图像;

8、多级注释二进制分割图像中的分割环,以提供多级注释图像;以及

9、基于所述多级注释图像,训练第二机器学习逻辑作为用于分割环的机器学习逻辑。

10、通过使用具有第一机器学习逻辑和第二机器学习逻辑的此两步骤训练处理,可改进或促进训练。如本文所用,机器学习逻辑是指对物体进行分类和执行分割的实体,在此情况下,基于机器学习技术(有时也称为人工智能(ai))识别环的各个部分。机器学习逻辑有时也称为模型。分割通常是指识别物件的单独部分(在此情况例如环),使得所述部分可用于进一步分析或其他处理。机器学习逻辑的范例可例如包括决策树、向量机器或各种类型的神经网路,像是深度神经网路、对抗网路等。

11、在一些具体实施例中,第一机器学习逻辑可为比第二机器学习逻辑更不复杂的模型。例如,第一机器学习逻辑包括随机森林模型,和/或第二机器学习逻辑可包括神经网路。

12、在一具体实施例中,该方法可更包含基于校正的二进制分割图像,重新训练第一机器学习逻辑,以改进训练。

13、在一具体实施例中,训练第二机器学习逻辑可基于多级注释图像的第一部分,并且其中该方法更包含基于与该第一部分不同的多级注释图像的第二部分,测试训练过的第二机器学习逻辑。

14、根据第二方面,提供一种分析高深宽比har结构中柱横截面环的方法,该方法包含:

15、提供柱的横截面图像;

16、使用训练过的机器学习逻辑在该横截面中分割环;以及

17、基于已分割环来确定所述环的参数。

18、如此,可分析柱的内部结构,例如存储器通道。

19、该机器学习逻辑为使用第一方面方法训练的第二机器学习逻辑。

20、在一具体实施例中,该方法可更包含基于已分割的环来识别环的轮廓,其中基于已识别的轮廓来确定参数。

21、在一具体实施例中,所述参数可包括选自由环半径和环直径所构成的群组的参数。

22、在一具体实施例中,该方法可更包含识别参数与额定值或预期值的偏差。

23、本文讨论的技术可具体实施或用于通过集成电路横截面法的针对har结构的3d体积图像或3d形状进行高精度3d重建的方法,更具体的是,用于获得har结构的3d体积图像的方法、计算机程序产品和装置。

24、例如,在一具体实施例中,该方法可更包含:

25、获得半导体样本的3d断层扫描图像;

26、从该3d断层扫描图像中选择包括该柱的横截面图像的2d横截面图像区段的子集,每一区段包含一组har结构的横截面图像;

27、识别2d横截面图像子集中的该组har结构内的每一har结构的轮廓;

28、从该组har结构的har结构轮廓中提取偏差参数;

29、分析所述偏差参数,

30、其中所述偏差参数包含下列中的一个或多个:

31、与理想位置的位移;

32、半径或直径的偏差;

33、与横截面面积的偏差;

34、与横截面形状的偏差。

35、在一具体实施例中分析偏差参数的步骤可包含对一组har结构的至少一个har结构的至少一个偏差参数进行统计分析。

36、该方法允许对har结构的横截面的直径和形状进行定量测量,以及确定集成电路内的har结构的轨迹。此外,本发明提供一种方法、计算机程序产品和装置,用于确定通过集成半导体装置的通道轨迹,以及确定通道轨迹与理想通道轨迹的偏差,其精度在数纳米以下。

37、在本发明的一具体实施例中,集成半导体样本内的这种柱的3d形状经由横截面法技术测量,其利用带电粒子束系统对集成半导体进行切片和成像,以确定集成半导体内预定体积的3d体积图像。此横截面成像技术包括一组横截面图像的生成和储存。带电粒子系统可包括用于成像的电子显微镜(sem)和用于切片的聚焦离子束系统(fib)、或用于切片和成像的离子束系统。

38、3d存储器芯片(vnand或3d ram)由许多相互平行运行的柱状结构构成,且有时称为存储器通道或“柱”。根据一具体实施例或本发明,可通过利用fib-sem显微镜的横截面成像技术,来研究含有此3d存储器装置的样本。聚焦离子束(fib)用于逐片从探针去除一薄材料层。在一范例中,fib配置成使得切片定向为垂直于柱/通道轴,每个新暴露表面将包含通常具有圆形并形成六边形网格的柱的覆盖区。每个新暴露表面或切片通过sem(扫描电子显微镜)或另一带电粒子成像显微镜逐一成像,因为fib正在从探针去除材料。柱的3d形状是使用2d切片图像堆叠所重建。一个切片中柱的典型覆盖区数量可达到数百个。典型的图像切片堆叠可包含数百张图像。在大多数应用中,在3d中重建柱时的高度自动化是必然的。在一具体实施例中,描述用于此重建的自动化工作流程。

39、在本发明的一具体实施例中,通过集成电路的3d体积图像相交平面内的图像处理和/或图案辨识,确定和提取至少一个har结构的横截面图像。从而在预定体积内以高精度确定至少一个har结构的横截面图像的准确位置。通过在集成电路的3d体积图像的后续相交平面内重复确定和提取至少一个har结构的后续横截面图像,生成集成半导体之内预定体积内的har结构的隔离3d体积图像。

40、在本发明的一具体实施例中,通过图像处理自动评估至少一个har结构的横截面图像以提取形状特性,诸如横截面的横向尺寸。在一范例中,椭圆近似于至少一个har结构的横截面。在另一范例中,形状属性包含横截面图像的面积。在一范例中,har结构的形状属性用于缺陷检测或缺陷审查。

41、在一具体实施例中,评估更包括以高精度,提取3d体积图像内的至少一个har结构的横截面图像的中心。中心的提取可通过计算至少一个har结构的横截面图像的重心来完成。

42、通过在集成电路的3d体积图像的后续相交平面内重复评估至少一个har结构的后续横截面图像,生成3d通道轨迹或3d轨迹。在一个范例中,3d放置偏差轨迹源自3d轨迹与理想或设计轨迹的偏差。由于可将坐标系统配置成使得设计轨迹在z方向上延伸,垂直于集成半导体的顶面,所以3d放置偏差轨迹沿着通道的3d轨迹或在z方向上进行评估。从3d放置偏差轨迹,导出最大放置偏差。在一个范例中,导出3d轨迹相对于z方向的最大倾斜角。在一个范例中,导出3d轨迹相对于z方向的摆动或扭曲形状。

43、在一具体实施例中,以类似方式重复生成沿集成半导体内预定体积之内har结构的3d轨迹的形状特性。由于可将坐标系统配置成使得设计轨迹在z方向上延伸,垂直于集成半导体的顶面,所以形状特性沿着通道的3d轨迹或在z方向上进行评估。

44、在一具体实施例中,通道的导电率由通道中最小的横截面积所确定。在另一具体实施例中,提取通道边界表面内的峰值、缺陷或中断或夹杂。

45、在一具体实施例中,至少针对两个har结构确定和评估har结构的3d轨迹和形状特性。除了单独har结构的3d轨迹和形状特性之外,还评估至少两个har结构的相对特性。相对属性包括通道接近度,诸如3d轨迹的距离以及至少两个har通道的外边界的最小距离。

46、在一具体实施例中,本发明的方法包含分析集成半导体装置内的一组har结构,包含获得半导体样本的3d断层扫描图像,从该3d断层扫描图像中选择2d横截面图像区段的子集,其各包含一组har结构的横截面图像,识别2d横截面图像子集中的该组har结构内的每一har结构的轮廓,从该组har结构的har结构轮廓中提取偏差参数,分析偏差参数,其中所述偏差参数包含与理想位置的位移、半径或直径的偏差、与横截面面积的偏差、与横截面形状的偏差中的一个或多个。

47、在一具体实施例中,该方法更包含对该组har结构中的至少一个har结构的至少一个偏差参数执行统计分析。在一范例中,与理想位置的位移的偏差参数包含har结构的倾斜或摆动。

48、在一具体实施例中,该方法更包含获得3d断层扫描图像的步骤,包含通过具有至少一个带电粒子光学柱的带电粒子显微镜来获得3d断层扫描图像。

49、在一具体实施例中,该方法另利用包含具有聚焦离子束系统(fib)的带电粒子显微镜、以及相对于彼此以45°和90°之间角度配置的扫描电子显微镜(sem)。在一范例中,相对角度为90°,使得fib平行于半导体样本的表面定向,并且sem垂直于半导体样本的表面定向。

50、在一具体实施例中,该方法更包含在识别每个har结构的至少一个轮廓的步骤中的图像处理、边缘检测或图案辨识。

51、在一具体实施例中,该方法更包含计算该组har结构中的至少一个har结构的至少一个偏差参数的最小值或最大值。

52、在一具体实施例中,该方法更包含至少计算两个相邻har结构之间的距离、以及计算两个相邻har结构之间的最小距离。

53、在一具体实施例中,该方法更包含检测和定位该组har结构中的至少一个har结构内的至少一个局部缺陷或夹杂物。

54、在一具体实施例中,该方法更包含使用高分辨率扫描电子显微镜进行图像获取、以及对至少一个har结构的内部结构进行识别和定位,该har结构包含核心与环绕该核心的至少一层。

55、在一具体实施例中,该方法更包含从至少一个har结构的内部结构轮廓中提取至少一个偏差参数,并分析该偏差参数。

56、在一具体实施例中,该方法更包含制程特征化、制程最佳化和/或制程监控的步骤。

57、根据本发明的一具体实施例的装置为半导体检查装置,其包含:聚焦离子束装置(fib),其适配于研磨集成半导体样本的一系列横截面;扫描电子束显微镜(sem),其适配于对集成半导体样本的一系列横截面进行成像;以及控制器,其用于操作一组指令,可执行根据前述方法的至少一个具体实施例的步骤,其中聚焦离子束(fib)和电子束显微镜(sem)彼此形成约90°角度。

58、在一具体实施例中,晶片检查方法包括以下步骤:获得晶片内部检查体积的3d体积图像,并选择代表该检查体积中相关半导体特征的横截面的一组范本。所述相关半导体特征可包括以下之一者:金属线、通孔、触点、鳍状物、har结构、har通道或栅极结构。该方法更包含确定该检查体积内相关半导体特征的横截面的中心位置,例如通过将范本与3d体积图像的一组2d横截面图像相关联。该方法更包含确定3d体积图像内的相关半导体特征的轮廓的步骤,以及确定至少一个代表性图元(primitive)的参数的步骤,该图元匹配该相关半导体特征的轮廓。该方法更包含分析参数的步骤。在一范例中,该方法更包含将该相关半导体特征的多个横截面的子集分配给特定相关半导体特征的步骤。该方法可更包含通过使用双光束系统的切片和成像方法,从样本片生成3d体积图像的步骤。双光束系统可包含用于切片的fib光束、以及用于成像的带电粒子成像显微镜,例如sem或氦离子显微镜(him)。该方法可更包含从晶片中取出样本片并固定该样本片的步骤。该取出步骤可包括将样本片附接到探针、移动样本片以及将样本片附接到固定器的步骤。在一范例中,从晶片中取出样本片的步骤在双光束装置中执行。双光束装置可更包含激光光束装置,其构造成从晶片切割半导体样本,并且该方法可包括在该晶片中执行激光切割。分析参数的步骤可包含统计平均值和统计偏差的计算、与参考图元的比较或与晶片坐标的关联性中的至少一个。因此,获得一组偏差参数。根据一具体实施例,该方法包含将偏差参数分类为某种类型的缺陷。此类缺陷的范例为“对齐错误”、“变形形状”、“距离太小”、“直径太小”等。

59、根据本发明的一方面,本发明有关一种计算机程序产品,其具有适配于执行前述任何方法的程序代码。程序代码可用任何可能的编程语言编写,并且可在计算机控制系统上执行。这样的计算机控制系统可包含一个或多个计算机或处理系统。计算机程序可在有形存储介质上提供。

60、根据本发明的一方面,本发明有关一种半导体检查装置,其适配于执行根据如前述多个具体实施例之任一者所述的方法中的任一者;以及计算机程序和存储介质。

- 还没有人留言评论。精彩留言会获得点赞!