神经网络装置、方法和包括所述装置的系统与流程

背景技术:

1、本公开涉及一种神经网络装置。

2、本公开还涉及一种包括神经网络装置的神经网络系统。

3、本公开还涉及一种神经网络方法。

4、背景技术

5、神经网络装置被设计成以与生物神经网络(例如存在于大脑中)的操作可比较的方式来执行计算。神经网络装置将神经元模拟为通过消息传输网络互连的神经网络装置元件。已达到激发状态的神经网络装置元件将输出消息传输到与其连接的神经网络装置元件,其方式类似于其中生物神经元经由其轴突将峰值传输到接收生物神经元的突触的方式。在实践中,相应的神经网络装置元件集合共享相应的计算和控制模块,所述计算和控制模块负责执行将要由神经网络装置元件执行的计算和逻辑步骤。例如,神经网络装置被提供为多个处理器内核,每个处理器内核具有相应的存储器单元,所述存储器单元具有相应的存储位置以用于存储相应的神经网络装置元件的状态。神经网络装置通常被组织为多个神经网络装置层,其中每个神经网络装置层包括多个神经网络装置元件。神经网络装置层的多个神经网络装置元件的相应状态共同定义了特征图。

6、神经网络装置的处理器内核需要存储空间以用于相互不同的目的。示例是用于将要在神经网络装置元件之间交换的事件消息进行排队的事件队列、用于存储神经网络装置元件的相应状态的状态存储器、用于存储指示由装置元件分配至从另一个装置元件或从其自身接收的事件消息的权重的权重值的权重(突触)存储器、以及用于指定神经网络装置元件之间的连接的连接性存储器。此外,可能需要存储空间来存储指示用于传输事件消息的预定延迟的延迟值。

7、通过在相应的物理存储器中提供这些存储空间,可以最小化存储器访问时间,以便可以独立地进行用于相互不同目的的存储器访问。由此,应当考虑到相互不同的处理应用程序可能涉及显著不同的存储器要求。例如,一个应用程序可能需要较大的物理存储器来存储事件队列,而另一个应用程序可能需要较大的物理存储器来存储连接性数据。

8、更具体地,在大型神经网络装置中,一些处理器内核支持单个网络层的(小)部分,而其他处理器内核可以支持多个(小)层。此外,在较低索引层(在图的前端)中,可能需要大量存储空间来存储神经元状态。在一些较高索引层中,需要大量存储空间来存储用于指定连接性的网络参数,并且网络参数例如为连接权重。作为另一示例,一些处理器内核可能需要大量存储空间来将传入事件进行排队并避免溢出。因此,所需的存储空间量取决于网络的结构和应用程序的性质。

9、为了使数据处理器装置适用于任意应用程序,大量的存储空间需要能够用于每种用途。这进而需要集成电路中的大表面积。此外,通常具有不同的大小的各种物理存储器会导致vlsi布局不规则并且因此效率低下。所得的布局可能包含大量所谓的空白空间。也可以替代地通过在共享的多端口存储器中提供各种存储空间来调整访问时间。然而,多端口sram的每个位的面积成本远高于单端口sram的每个位的面积成本。

技术实现思路

1、本公开的一个目的是提供一种神经网络装置,所述神经网络装置适用于任意应用程序,同时具有适度的存储器要求。

2、本公开的另一个目的是提供一种神经网络方法,所述神经网络方法适用于任意应用程序,同时具有适度的存储器要求。

3、根据本公开,本文要求保护一种神经网络装置,所述神经网络装置包括物理存储器、数据处理器内核、可配置存储器映射单元、配置模块和存储器接口模块。

4、物理存储器包括多个可独立访问的存储器组。数据处理器内核被配置为执行指令集的指令。这些指令中的一个或多个涉及多个存储器访问操作,所述多个存储器访问操作指定物理存储器内的相应逻辑存储器中的相应的存储器地址。指令可以例如指定响应于事件消息而更新神经网络元件的状态值的操作。所述操作需要访问:第一存储位置,在第一存储位置中存储将要用来对事件消息进行加权的权重;以及第二存储位置,从所述第二存储位置读取当前状态并将更新的状态写入所述第二存储位置。第一存储位置是存储权重数据的第一逻辑存储器的一部分,并且第二存储位置是存储状态数据的第二逻辑存储器的一部分。

5、所要求保护的神经网络装置还包括可配置存储器映射单元,所述可配置存储器映射单元用于将逻辑存储器地址映射到物理地址。物理地址包括多个存储器组中的存储器组的指示和所指示的存储器组内的行地址。

6、所要求保护的神经网络装置还包括配置模块,所述配置模块用于对特定应用程序配置可配置存储器映射单元。在配置中,相应的逻辑存储器被分配物理存储器的相应区段。在运行期间(即在应用程序的执行期间)维持可配置存储器映射单元的配置。在一个示例中,物理存储器区段的分配完全由操作者控制。在另一个示例中,分配基于要执行的应用程序的描述自动地进行。在又一个示例中,分配半自动地进行。

7、作为一个示例,在其中处理器内核用于实现(a)较低索引层(在神经网络的输入侧处)的应用程序中,可用物理存储空间的很大一部分可以被配置成用于存储神经元状态。通常,(a)较高索引层(在神经网络的输出侧处)的神经元状态所需的存储器容量更加适度。通常,对于较高索引层,可以针对连接性数据(即指定哪些处理器装置元件相互连接的数据)配置相对大量的可用存储空间。在另一个示例中,配置模块配置可配置存储器映射单元,以将物理存储器的相对较大的区段配置为用于将传入事件进行排队的逻辑存储器。

8、所要求保护的神经网络装置还包括存储器接口模块,以促使对物理存储器中配置的相互不同的逻辑存储器的存储器访问操作。存储器接口模块将用于向相应区段写入数据和/或从相应区段读取数据的存储器访问请求接收到相应的逻辑存储器,并且协调对物理存储器中的相应分配的区段的访问。

9、对于其中可配置存储器映射单元能够将物理存储器的相应区段分配至相应的逻辑存储器的方式,可以有各种选项。根据一个选项,可配置存储器映射单元能够将物理存储器的相应的组集合分配至相应的逻辑存储器。在配置阶段,配置模块通过对每个相应的逻辑存储器分配适当数量的组来为特定应用程序配置可配置存储器映射单元。在应用程序执行期间,即在运行期间,存储器接口模块根据在配置阶段分配的相应的组集合来促使用于相应的逻辑存储器的存储器访问操作。由于不同的逻辑存储器被分配了不同组集合的事实,因此完全避免了与相互不同的逻辑存储器相关联的存储器访问操作之间可能发生的冲突。然而,同一逻辑存储器“端口”可以根据应用程序访问相互不同的物理存储器组集合。在执行期间,存储器接口模块提供存储器访问操作到在配置阶段中分配的物理存储器组的适当路由。

10、根据另一种选择,可配置存储器映射单元能够将组内的相应地址范围分配至相应的逻辑存储器。在配置阶段,配置模块通过对每个逻辑存储器分配相应的地址范围来为特定应用程序配置可配置存储器映射单元。在应用程序执行期间,即在运行期间,存储器接口模块根据在配置阶段分配的相应地址范围来促使对于相应逻辑存储器的存储器访问操作。如果存储器访问操作请求访问共享相同组的相互不同的逻辑存储器,则可能会发生潜在的访问冲突。为了解决这种情况,存储器接口模块包括仲裁模块,以用于将此类并发的组(加载/存储)访问请求序列化。在一个实施例中,针对每个存储器组提供相应的缓冲器,以临时缓冲待处理的存储器访问请求。在一个示例中,仲裁模块被配置成在此类请求同时发生的情况下,使加载(存储器读取)请求优先,并对存储(写入)请求进行缓冲。这使得数据处理器内核可以直接接收由加载请求指示的数据,并且还可以直接写入存储请求中包含的数据。需要注意的是,相互不同的逻辑存储器可以共享组集合。尽管仍然可能由于并发的存储器访问请求而发生访问冲突,但只要组的数量显著大于逻辑存储器的数量,就可以大大降低发生这种情况的概率。

11、根据另一个选项,提供了混合物理存储器分区,其中相互不同的逻辑存储器集合共享相互不同的组集合。例如,第一逻辑存储器和第二逻辑存储器共享一个或多个组中的第一集合,并且第三逻辑存储器和第四逻辑存储器共享一个或多个组中的第二集合。

12、在一些实施例中,物理存储器的存储器组是单端口存储器单元。尽管多端口存储器单元也将适用,但使用单端口存储器单元可以实现减小的硅占用空间。

13、在一些实施例中,存储器组是相互相同的存储器单元。这有助于简化存储器控制结构。

14、在一个实施例中,实现了物理存储器的甚至更高效的使用,其中数据处理器内核被配置成执行一系列连续指令,在所述一系列连续指令中,访问连续位于逻辑存储器中的数据字。在其中数据处理器内核被配置成执行使用单个逻辑存储器地址并行加载或存储多个数据字的指令的实施例中,实现了进一步的改进。

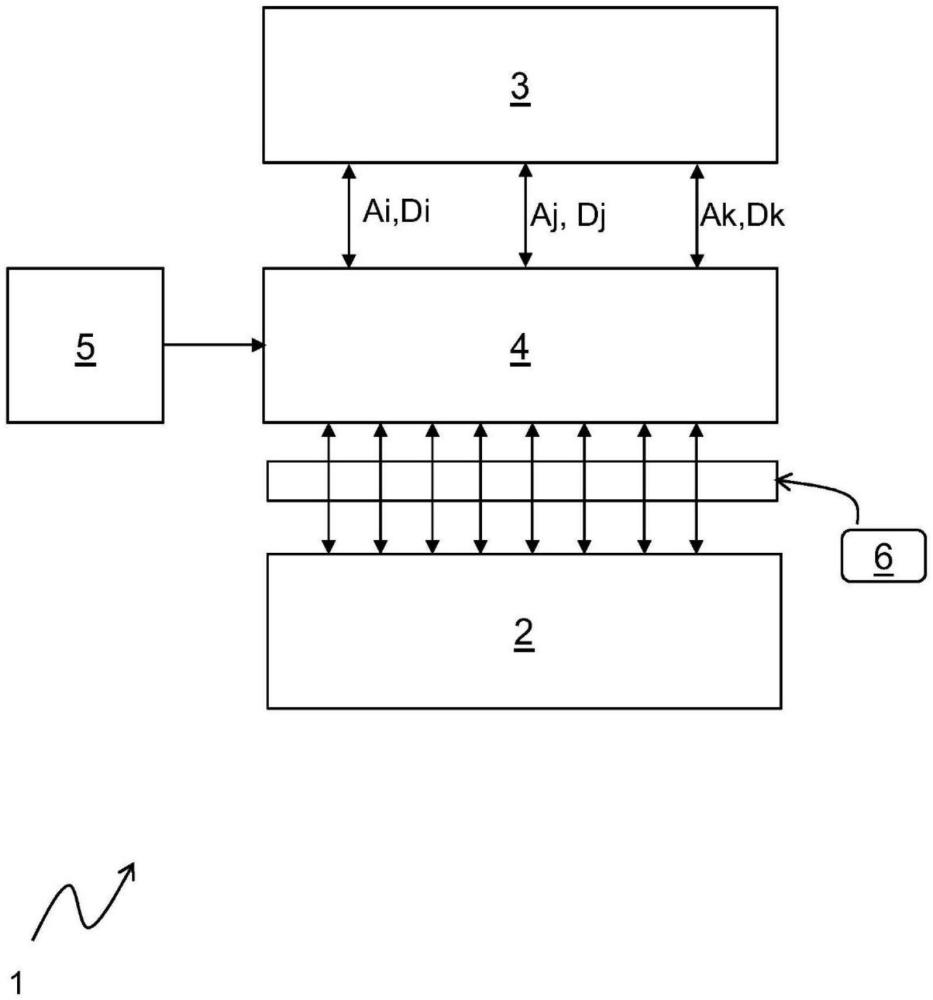

15、本公开还提供了一种改进的神经网络系统,所述神经网络系统包括如上所述的多个神经网络装置,并且还包括具有用于每个神经网络装置的相应网络节点和联接网络节点的网络链路的消息交换网络。消息交换网络使得神经网络装置能够交换消息。以这种方式,通过将神经网络的相应区段映射到相应的神经网络装置,可以以任意规模实现神经网络。由此,可以针对神经网络的映射到其上的区段来适当地配置每个神经网络装置。

16、本公开还提供了一种改进的神经网络处理方法,所述方法包括配置阶段和执行阶段。

17、在配置阶段,通过将物理存储器的相应区段分配至相应的逻辑存储器来配置神经网络处理装置的物理存储器。该操作包括配置存储器映射单元以根据所述配置将相应的逻辑存储器地址映射到具有多个可独立访问的存储器组的共享物理存储器中的相应的物理地址。

18、在执行阶段,神经网络处理装置的数据处理器内核执行至少一个指令,所述至少一个指令涉及指定相应逻辑存储器中的相应存储器地址的多个存储器访问操作。然后,经配置的存储器映射单元将相应逻辑存储器中的相应存储器地址映射到对应的物理存储器地址。对应的物理存储器地址包括物理存储器中的存储器组的名称和存储器组中的地址。如上所述,被分配的区段可以是一个或多个组集合、组内的地址范围或两者的组合。

19、有利的是,数据在逻辑存储器中的布局使得通常(但不一定总是)p个连续指令的加载和存储操作涉及连续位于相应逻辑存储器中的数据字。数据处理器内核被配置成执行指令,在所述指令中,在单个存储器周期中访问连续位于逻辑存储器中的数据字。需要注意的是,“在单个存储器周期中访问”这一措辞应理解为是指在吞吐量意义上的,而不是在延迟意义上的。即,数据处理器内核在单个周期内访问连续的逻辑存储器地址中的每一者,但可以是在启动读取访问和读取数据可用于进一步处理之间涉及额外周期的情况。

20、在一个实施例中,存储器映射单元可被配置成允许使用单个地址并行加载和存储p个字。这使得处理器内核可以执行指定单个逻辑存储器地址的指令。在执行指令时,存储器映射单元将逻辑地址转换为p个组的范围的名称,并且存储器接口模块并行访问该范围内的组,以从这些组中的每一者中加载p个字中的相应一个。同样,它可以并行访问这些组,以将p个字中的相应一个存储在这些组中的每一者中。

- 还没有人留言评论。精彩留言会获得点赞!