电路时序优化方法、装置、电子设备及存储介质与流程

1.本技术的实施方式涉及集成电路技术领域,更具体地,涉及一种电路时序优化方法、电路时序优化装置、电子设备及计算机可读存储介质。

背景技术:

2.时序分析是大规模集成电路设计中的重要环节之一,可用来评定集成电路设计在特定工作频率下的正常工作的能力。时序分析报告可提供不满足时序要求的时序路径信息,通过对这些时序路径进行时序优化能够改善电路的整体时序性能。

3.在一些相关技术中,设计人员需要阅读时序分析报告,并选取不满足时序要求的时序路径(即违例路径),然后对该违例路径进行人为修正,接着对修正后的电路进行功能验证和时序分析,以判断修正后的电路是否同时满足功能和时序的设计需求,若“否”,则设计人员需要调整对该违例路径的修正方案,并再次对修正后的电路进行功能验证和时序分析,直到修正后的电路同时满足功能和时序的设计需求。

4.然而,这种电路时序优化方法通常需要经过多次人为修正、功能验证以及时序分析的迭代才能最终确定出目标优化电路,因此需要消耗较多的人力资源并且效率较低,影响集成电路的设计周期。同时受限于设计人员的知识背景,人为修正容易遗漏修正方案,从而难以确定出目标优化电路。

技术实现要素:

5.本技术提供了一种可至少部分解决现有技术中存在的上述问题或本领域其它问题的一种电路时序优化方法、装置、电子设备及存储介质。

6.第一方面,本技术的一些实施方式提供了一种电路时序优化方法。该电路时序优化方法包括:获取第一电路的违例路径;生成与第一电路的违例路径对应的多个第二电路;将多个第二电路与第一电路进行形式验证;以及将通过了形式验证且不存在违例路径的第二电路确定为目标优化电路。

7.在一些实施方式中,违例路径包括组合逻辑,每个第二电路可包括在组合逻辑中插入至少一级寄存器后得到的电路。

8.在一些实施方式中,该电路时序优化方法还可包括:根据组合逻辑的逻辑级数,确定至少一级寄存器将要在组合逻辑中的插入位置;以及根据确定的插入位置在组合逻辑中插入至少一级寄存器。

9.在一些实施方式中,获取第一电路的违例路径的步骤可包括:获取第一电路的候选违例路径,其中,候选违例路径包括组合逻辑;以及将候选违例路径中组合逻辑的逻辑级数大于级数阈值的路径,确定为违例路径。

10.在一些实施方式中,第一电路包括多层级的模块,其中,生成与第一电路的违例路径对应的多个第二电路的步骤可包括:将在最低层级上与违例路径所在模块连接的时序路径确定为相关路径;以及生成与违例路径及其相关路径对应的多个第二电路。

11.在一些实施方式中,将通过了形式验证且不存在违例路径的第二电路确定为目标优化电路的步骤可包括:根据第二电路的占用面积和/或时间余量信息,将通过了形式验证且不存在违例路径的第二电路确定为目标优化电路。

12.在一些实施方式中,时间余量信息包括在第二电路中与违例路径对应的时序路径的时间余量,其中,可将第二电路的占用面积小于面积阈值和/或时间余量大于余量阈值确定为目标优化电路。

13.在一些实施方式中,获取第一电路的违例路径的步骤可包括:根据第一电路对应的第一rtl代码和时序约束条件进行第一次逻辑综合;以及根据第一次逻辑综合后得到的第一时序分析结果获取违例路径。

14.在一些实施方式中,多个第二电路对应于多个第二rtl代码,将多个第二电路与第一电路进行形式验证的步骤可包括:根据各个第二rtl代码与第一rtl代码的比对结果,确定出通过了形式验证的第二电路。

15.在一些实施方式中,将通过了形式验证且不存在违例路径的第二电路确定为目标优化电路的步骤可包括:根据通过了形式验证的第二电路对应的第二rtl代码和时序约束条件,进行第二次逻辑综合;以及根据第二次逻辑综合后得到的第二时序分析结果,将不存在违例路径的第二电路确定为目标优化电路。

16.第二方面,本技术的一些实施方式提供了一种电路时序优化装置。该电路时序优化装置包括:获取模块,被配置为获取第一电路的违例路径;生成模块,被配置为生成与第一电路的违例路径对应的多个第二电路;验证模块,被配置为将多个第二电路与第一电路进行形式验证;以及确定模块,被配置为将通过了形式验证且不存在违例路径的第二电路确定为目标优化电路。

17.第三方面,本技术的一些实施方式提供了一种电子设备,该电子设备包括:至少一个处理器;以及,与至少一个处理器通信连接的存储器,其中,存储器存储有可被至少一个处理器执行的指令,指令被至少一个处理器执行,以使至少一个处理器能够执行如上述实施方式提及的电路时序优化方法。

18.第四方面,本技术的一些实施方式提供了一种计算机可读存储介质,计算机可读存储介质存储有计算机程序,其中,计算机程序被处理器执行时,实现如上述实施方式提及的电路时序优化方法。

19.根据本技术实施方式提供的一种电路时序优化方法、装置、电子设备及存储介质,在获取第一电路的违例路径之后,通过对违例路径修正以生成多个第二电路;接着将多个第二电路与第一电路进行形式验证,即将多个第二电路满足功能要求的电路筛选出来;然后将通过了形式验证且不存在违例路径的第二电路确定为目标优化电路,即将上述满足功能要求的第二电路根据时序要求进一步筛选,从而确定出满足功能和时序要求的目标优化电路,能够应对在现有技术的修正过程中的反复迭代操作导致的效率较低、人力开销较大的问题,同时可降低时序优化的出错概率,提升时序优化的效率。

附图说明

20.通过阅读参照以下附图所作的对非限制性实施方式所作的详细描述,本技术的其它特征、目的和优点将会变得更明显:

图1是根据本技术示例性实施方式的电路时序优化方法的流程图;图2是根据本技术示例性实施方式的第一电路的时序路径的示意图;图3是根据本技术示例性实施方式的第一电路的违例路径的示意图;图4是根据本技术示例性实施方式的违例路径对应的多个修正路径的示意图;图5是根据本技术另一示例性实施方式的电路时序优化方法的流程图;图6是根据本技术实施方式的多层级的第一电路的架构图;图7是根据本技术示例性实施方式的电路时序优化装置的框图;以及图8是根据本技术示例性实施方式的电子设备的框图。

具体实施方式

21.为了更好地理解本技术,将参考附图对本技术的各个方面做出更详细的说明。应理解,这些详细说明只是对本技术的示例性实施方式的描述,而非以任何方式限制本技术的范围。

22.本文使用的术语是为了描述特定示例性实施方式的目的,并且不意在进行限制。当在本说明书中使用时,术语“包含”、“包含有”、“包括”和/或“包括有”表示存在所述特征、整体、元件、部件和/或它们的组合,但是并不排除一个或多个其它特征、整体、元件、部件和/或它们的组合的存在性。

23.除非另有限定,否则本文使用的所有术语(包括技术术语和科学术语)具有与本公开所属技术领域的普通技术人员的通常理解相同的含义。诸如常用词典中定义的术语应被解释为具有与其在相关领域的语境下的含义一致的含义,并且将不以理想化或过度正式的意义来解释,除非本文明确地如此定义。

24.需要说明的是,在不冲突的情况下,本技术中的实施方式及实施方式中的特征可以相互组合。另外,除非明确限定或与上下文相矛盾,否则本技术所记载的方法中包含的具体步骤不必限于所记载的顺序,而可以任意顺序执行或并行地执行。

25.下面将参考附图对本技术的实施方式进行详细地描述。

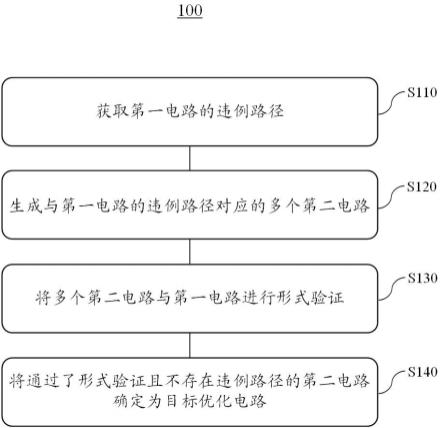

26.本技术的实施方式提供了一种电路时序优化方法。图1是根据本技术示例性实施方式的电路时序优化方法100的流程图。如图1所示,电路时序优化方法100包括以下步骤。

27.s110,获取第一电路的违例路径。

28.s120,生成与第一电路的违例路径对应的多个第二电路。

29.s130,将多个第二电路与第一电路进行形式验证。

30.s140,将通过了形式验证且不存在违例路径的第二电路确定为目标优化电路。

31.根据本技术实施方式提供的电路时序优化方法,在获取第一电路的违例路径之后,通过对违例路径修正以生成多个第二电路;接着将多个第二电路与第一电路进行形式验证,即将多个第二电路满足功能要求的电路筛选出来;然后将通过了形式验证且不存在违例路径的第二电路确定为目标优化电路,即将上述满足功能要求的第二电路根据时序要求进一步筛选,从而确定出满足功能和时序要求的目标优化电路,能够应对在人为修正过程中的反复迭代操作导致的效率较低、人力开销较大的问题,同时可降低时序优化的出错概率,提升时序优化的效率。

32.下面对该实施方式的各个步骤s110至s140进一步描述。

33.s110,获取第一电路的违例路径。

34.在一些实施方式中,第一电路可为用于实现逻辑操作的逻辑电路。逻辑电路可包括组合逻辑子电路和时序逻辑子电路。组合逻辑子电路(以下简称为组合逻辑)可为对输入信号进行操作并在输出端实时反映输入信号的变化的电路。例如,组合逻辑可包括与门、与非门、或门、或非门等组合逻辑单元(以下称为逻辑门)。时序逻辑子电路可为接收时钟信号以及数据信号,由时钟信号控制数据信号的加载及输出的电路。例如,时序逻辑子电路可包括寄存器,触发器等时序逻辑单元。

35.在一些实施方式中,第一电路可为门级电路,并且可通过时序分析(例如,静态时序分析)得到第一电路的违例路径。具体而言,首先可采用穷尽分析方法提取出第一电路存在的所有时序路径;然后计算信号在各个时序路径上的传播延时;接着检查信号的延时是否满足时序要求,若不满足时序要求,则将该时序路径判定为违例路径。

36.图2是根据本技术示例性实施方式的第一电路200的时序路径的示意图,用以示例性说明本技术所述的时序路径。例如,图2示出的第一电路200可为本技术所述的第一电路的一部分。

37.如图2所示,第一电路200可包括组合逻辑211至214以及时序逻辑单元221和222。第一电路200中的每个组合逻辑211至214可包括零到多个逻辑门,例如包括多个串联、并联或串并连的逻辑门。每个组合逻辑211至214可包括相同或不同数量的逻辑门,并且每个组合逻辑211至214中逻辑门可具有相同或不同的连接方式。时序逻辑单元221和222可为d触发器。在一些示例中,时序逻辑单元221和222也可为其它类型的时序逻辑单元(例如,寄存器)。第一电路200还包括数据输入端230、数据输出端235以及时钟输入端240。数据输入端230可用于提供数据输入信号in至组合逻辑211。数据输出端235可用于输出来自组合逻辑213的数据输出信号out。时钟输入端240可用于提供时钟信号clk至时序逻辑单元221和222的时钟输入端ck。在一些示例中,时序逻辑单元221和222的时钟输入端ck接收同一时钟信号clk。在另一些示例中,第一电路200可包括时钟输入端240和时钟输入端250(未示出),以使时序逻辑单元221和222的时钟输入端ck可接收不同的时钟信号。

38.继续参考图2,第一电路200可包括时序路径path1至path4。时序路径path1从数据输入端230开始,经由组合逻辑211至时序逻辑单元221的数据输入端d。时序路径path2从时序逻辑单元221的时钟输入端ck开始,经由时序逻辑单元221、组合逻辑212到达时序逻辑单元222的数据输入端d。时序路径path3从时序逻辑单元222的时钟输入端ck开始,经由时序逻辑单元222和组合逻辑213到达数据输出端235。时序路径path4从数据输入端230开始,依序经由组合逻辑211、214以及213到达数据输出端235。例如,时序路径path2经由的组合逻辑212内具有10个逻辑门,并且5个逻辑门为串联连接,则时序路径path2的逻辑级数(logic levels)为5。

39.根据本技术实施方式,时序路径path1至path4分别示例了四种类型的时序路径,即电路的数据输入端到时序逻辑单元的数据输入端、时序逻辑单元的时钟输入端到另一时序逻辑单元的数据输入端、时序逻辑单元的时钟输入端到电路的数据输出端、电路的数据输入端到电路的数据输出端。应当注意,本技术所述的时序路径可看做是完整的时序路径的片段,该片段可不包括任何时序逻辑单元。此外,组合逻辑211至214可不包括任何时序逻辑单元,换言之,本技术所述的时序路径在起点和终点之间可不包括任何时序逻辑单元。

40.在一些实施方式中,第一电路可为其对应的第一rtl代码经过第一次逻辑综合而得到的门级电路。rtl(register transfer level, 寄存器传输级)代码是指采用诸如vhdl、verilog等硬件描述语言对电路功能和行为进行描述的代码。逻辑综合(logic synthesis)是指在诸如时序、负载、面积、功耗等约束条件下将rtl代码转换为基于目标工艺库的门级电路(或称为门级网表)的过程。例如,逻辑综合可借助于电子设计自动化(electronic design automation, eda)工具来实现。进一步地,在第一次逻辑综合之后,除了第一电路的门级网表文件,还可生成例如时序、面积、功耗分析报告。例如,时序分析报告可包括对第一电路的时序分析结果。在一些示例中,若第一电路存在不满足时序约束条件的时序路径,即第一电路在该时序约束条件下不收敛,则时序分析结果可包括不满足时序约束条件的时序路径(即违例路径)信息,例如违例路径的起点和终点。在另一些示例中,若第一电路不存在违例路径,即第一电路在该时序约束条件下收敛,则时序分析结果可包括各个时序路径的延时情况,例如各个时序路径相对于时序约束条件的时间余量信息。

41.在一些实施方式中,违例路径的数量可大于或者等于1。换言之,若第一电路在时序约束条件下不收敛,则时序分析结果可提供至少一条违例路径。通常而言,随着电路的复杂程度和操作速度的增加,违例路径的数量会增加。

42.应当指出,上文描述的进行第一逻辑综合,以及从时序分析报告中获取违例路径的过程,可例如通过编写相应的脚本/程序来实现。

43.在一些实施方式中,获取第一电路的违例路径的步骤可包括:获取第一电路的候选违例路径,并将候选违例路径中组合逻辑的逻辑级数大于第一级数阈值的路径,确定为违例路径。例如,在根据时序分析报告获取候选违例路径的情况下,候选违例路径可为时序分析报告中所提供的全部的违例路径。需要说明的是,如上文所述,在时序路径中,逻辑级数表示在该时序路径中所通过的串联逻辑门的数量。相似地,候选违例路径的逻辑级数表示在该候选违例路径中所通过的串联逻辑门的数量。通过获取组合逻辑的逻辑级数较高的违例路径,有利于提高通过对违例路径修正来生成多个第二电路的效率。

44.应当指出,上文描述的获取候选违例路径,以及确定违例路径的过程,可例如通过编写相应的脚本/程序来实现。

45.s120,生成与第一电路的违例路径对应的多个第二电路。

46.在第一电路不满足时序要求情况下,可对违例路径中的电路设计(例如,门级网表)进行修正以生成修正后的多个第二电路。在一些示例中,在违例路径的数量为1的情况下,针对违例路径进行修正可得到多个修正路径,每个第二电路可包括各个修正路径与第一电路中除了该违例路径之外的其它电路。在另一些示例中,在违例路径的数量大于1的情况下,相似地,针对每条违例路径进行修正可得到多个修正路径,遍历每条违例路径及其对应的多个修正路径,得到上述多个修正路径各种组合后的多个修正电路,每个第二电路可包括各个修正电路与第一电路中除了违例路径之外的其它电路。在一些实施方式中,对每条违例路径可采用诸如插入寄存器、改变组合逻辑中逻辑门的位置和驱动能力、调整时钟树等修正方法,本技术对此不做限制。此外,对违例路径进行修正并生成多个第二电路的过程,可例如通过编写相应的脚本/程序来实现。

47.图3是根据本技术实施方式的第一电路的违例路径310的示意图。图4是根据本技术示例性实施方式的违例路径对应的多个修正路径410a至410d的示意图。图3和图4用以示

例性说明插入寄存器的修正方法。例如,违例路径310可为在步骤s110中确定出的违例路径中的一条。

48.如图3所示,在违例路径310中,组合逻辑320可位于违例路径310的起点331与终点332之间。组合逻辑320可包括多个串联、并联或串并连的逻辑门(未示出)。其中,组合逻辑320的逻辑级数可为在该违例路径310中所通过的串联逻辑门的数量。

49.如图4所示,修正路径410a至410d包括对图3中示出的违例路径310修正后得到的电路。其中,修正路径的起点431可与图3中示出的违例路径310的起点331相同,修正路径的终点432可为图3中示出的违例路径310的终点332相同。在修正路径410a中,寄存器441a将图3中示出的组合逻辑320划分为子组合逻辑421a和422a,即,寄存器441a插入在子组合逻辑421a和422a之间。在修正路径410b中,寄存器441b和442b将图3中示出的组合逻辑320划分为子组合逻辑421b和422b,即,寄存器441b插入在子组合逻辑421b和422b之间,寄存器442b插入在子组合逻辑422b和终点432之间。在修正路径410c中,寄存器441c和442c将图3中示出的组合逻辑320划分为子组合逻辑421c和422c,即,寄存器441c插入在起点431与子组合逻辑421c之间,寄存器442c插入在子组合逻辑421c和422c之间。在修正路径410d中,寄存器441d、442d、443d将图3中示出的组合逻辑320划分为子组合逻辑421d和422d,即,寄存器441d插入在起点431与子组合逻辑421d之间,寄存器442d插入在子组合逻辑421d和422d之间,寄存器443d插入在子组合逻辑422d与终点432之间。

50.根据本技术实施方式,图4示出了四个修正路径410a至410d。具体而言,相对于图3中示出的违例路径310,图4中示出的修正路径410a包括插入一级寄存器441a得到的电路,修正路径410b和410c包括插入两级寄存器441b/441c和442b/442c得到的电路,修正路径410d包括插入三级寄存器441d、442d、443d得到的电路。需要说明的是,违例路径320对应的修正路径的数量不限于此。例如,还可通过插入其它数量的寄存器,或者在插入相同数量的寄存器的前提下,在违例路径的组合逻辑的不同位置插入寄存器,来得到违例路径对应的更多数量的修正路径。

51.在一些实施方式中,在违例路径的组合逻辑中插入至少一级寄存器的步骤可包括:根据违例路径中组合逻辑的逻辑级数来确定寄存器的插入位置。在一些示例中,参考图3,当组合逻辑320的逻辑级数为s,第二级数阈值为m时,其中,s和m均为正整数且m<s,则可在起点331之后的第k级逻辑门之后插入一级寄存器,并在起点331之后的第(k+m

×

n)级逻辑门之后再次插入n级寄存器,其中,k满足0≤k≤m且为整数,n为正整数,直到起点331与第(n+1)级寄存器之间的逻辑门的逻辑级数大于组合逻辑320的逻辑级数为s。例如,在组合逻辑的逻辑级数s为50,第二级数阈值m为20的情况下,可在起点331之后(即第0级逻辑门)插入一级寄存器,在起点331之后的第20级逻辑门、第40级逻辑门之后分别插入两级寄存器。又例如,可在起点331之后的第5级逻辑门之后插入一级寄存器,在起点331之后的第25级逻辑门、第45级逻辑门之后分别插入两级寄存器。再例如,可在起点331之后的第20级逻辑门之后插入一级寄存器,在起点331之后的第40级逻辑门之后插入另一级寄存器。在一些示例中,可将逻辑门的数据输出端与寄存器的数据输入端连接。应当指出,第二级数阈值可根据电路复杂程度和/或时钟频率进行预先设置。

52.应当指出,上文描述的确定寄存器的插入位置的过程,可例如通过编写相应的脚本/程序来实现。

53.根据本技术实施方式,通过在违例路径中插入寄存器能够改善违例路径的延时性能,从而解决第一电路的时序收敛问题。另一方面,在根据组合逻辑的逻辑级数确定寄存器的插入位置的情况下,能够确定出寄存器的数量,例如将第二级数阈值设置在合理的范围内,可控制寄存器的数量以及修正后的第二电路的数量,有利于提高在多个第二电路中确定出目标优化电路的效率。

54.s130,将多个第二电路与第一电路进行形式验证。

55.形式验证用于验证多个第二电路与修正前的第一电路之间的逻辑功能等价性。换言之,可将多个第二电路中通过与第一电路的形式验证的第二电路筛选出来,使得筛选出来的第二电路能够满足逻辑功能要求。应当指出,上文描述的进行形式验证的过程,可例如通过编写相应的脚本/程序来实现。

56.在一些实施方式中,形式验证可适用于在rtl级对修正后的第二电路和修正前的第一电路之间进行。如上文所述,多个第二电路为对违例路径中的电路设计(例如,门级网表)进行修正生成的电路,在生成多个第二电路的过程中,可生成多个第二电路对应的多个第二rtl代码。在一次形式验证中,首先可找到第二rtl代码与第一rtl代码相对应的比较点,然后比较每个比较点在输入激励相同的情况下所得到的值是否相同。若所有的比较点对应的值均相同,则表明该第二rtl代码与第一rtl代码相匹配。换言之,该第二rtl代码对应的第二电路通过了与第一电路的形式验证。应当指出,形式验证可借助于eda工具来实现,并且可例如通过编写相应的脚本/程序来实现。

57.s140,将通过了形式验证且不存在违例路径的第二电路确定为目标优化电路。

58.不存在违例路径的第二电路表明该第二电路时序收敛,满足时序要求。换言之,可将通过了形式验证的第二电路中不存在违例路径的第二电路进一步地筛选出来,使得再次筛选出来的第二电路既满足逻辑功能要求,又满足时序要求,并将再次筛选出来的第二电路确定为目标优化电路。应当指出,上文描述的确定目标优化电路的过程,可例如通过编写相应的脚本/程序来实现。

59.在一些实施方式中,可根据通过了形式验证的第二电路对应的第二rtl代码,进行第二次逻辑综合。例如,输入通过了形式验证的第二电路对应的第二rtl代码以及诸如时序、负载、面积、功耗等约束条件,将第二rtl代码转换为基于目标工艺库的门级网表,同时生成诸如时序、面积、功耗分析报告。其中,在第一次逻辑综合与第二次逻辑综合过程中,诸如时序、负载、面积、功耗等约束条件可保持相同。在对多个第二rtl代码分别进行第二次逻辑综合之后,可生成多个时序分析报告。若时序分析报告中的时序分析结果为不存在违例路径,则表明该第二rtl代码对应的第二电路时序收敛,满足时序约束条件。

60.应当指出,执行第二次逻辑综合的过程,可例如通过编写相应的脚本/程序来实现。此外,从多个第二电路中,可确定出至少一个目标优化电路,换言之,多个第二电路中至少一个目标优化电路能够满足逻辑功能和时序要求。

61.在一些实施方式中,确定目标优化电路的步骤还可包括:根据第二电路的占用面积和/或时间余量信息确定目标优化电路。例如,第二电路的占用面积可来自于第二逻辑综合所生成的面积分析报告,时间余量信息可来自于第二逻辑综合所生成的时序分析报告。在一些示例中,从多个第二电路确定出满足逻辑功能和时序要求的第二电路之后,还可对上述第二电路的占用面积小于面积阈值的第二电路进一步筛选。根据本技术实施方式,例

如以插入寄存器的修正方法生成的第二电路相对于修正前的第一电路占用面积会增加,通过设置面积阈值,能够使得确定出的目标优化电路具有较小的占用面积。在另一些示例中,从多个第二电路中确定出满足逻辑功能和时序要求的第二电路之后,还可对上述第二电路中与违例路径对应的时序路径的时间余量大于余量阈值的第二电路进一步筛选。时间余量是指针对一条时序路径而言,在满足时序约束条件下所剩余的时间长度。通常而言,保证足够的时间余量,有利于保证电路的时序性能。根据本技术实施方式,通过设置余量阈值,能够使得确定出的目标优化电路时序性能更佳。需要说明的是,在一些示例中,可根据占用面积和时间余量其中之一来确定目标优化电路。在另一示例中,在占用面积和时间余量均被考虑的情况下,可对占用面积和时间余量分配权重,来确定目标优化电路。

62.应当指出,上文描述的根据占用面积和/或时间余量信息确定目标优化电路的过程,可例如通过编写相应的脚本/程序来实现。

63.根据本技术实施方式提供的电路时序优化方法,例如通过编写相应的脚本/程序的方式使电路时序优化方法借助于eda工具标准化地执行,能够应对在人为修正过程中的反复迭代操作导致的效率较低、人力开销较大的问题,同时可降低时序优化的出错概率,提升时序优化的效率。

64.图5是根据本技术另一示例性实施方式的电路时序优化方法500的流程图。如图5所示,电路时序优化方法500可包括以下步骤。

65.s510,获取第一电路的违例路径。

66.s521,将在最低层级上与违例路径所在模块连接的时序路径,确定为相关路径。

67.s522,生成与违例路径及其相关路径对应的多个第二电路。

68.s530,将多个第二电路与第一电路进行形式验证。

69.s540,将通过了形式验证且不存在违例路径的第二电路确定为目标优化电路。

70.下面对该实施方式的各个步骤s510至s540进行进一步描述。出于简要的目的,该实施方式中步骤s510、s530至s540已在上文中详细地描述,本技术在此不再赘述。

71.s521,将在最低层级上与违例路径所在模块连接的时序路径,确定为相关路径。

72.在一些实施方式中,第一电路可为层次化设计的电路,其可包括多层级的模块。层次化电路设计可用于对复杂电路进行自上而下的设计。例如,将复杂的电路中功能相近的部分划分为多个第一层级的模块,而每个第一层级的模块进一步地划分为多个第二层级的模块,并依次划分至最低层级。其中,最低层级的每个模块内为逻辑门构成的电路。

73.图6是根据本技术实施方式的多层级的第一电路600的架构图,用以示例性说明第一电路600所包括的多层级的模块。例如,图6示出的第一电路600可为本技术所述的第一电路的一部分。

74.如图6所示,第一电路600可包括处于第一层级的模块611,处于第二层级的模块621、622、623,处于第三层级的模块631和632。其中,第一层级高于第二层级,第二层级高于第三层级。不同层级的模块彼此之间具有隶属关系,例如,上一层级的模块可包括下一层级的模块。在该实施方式中,第三层级可为最低层级,处于第三层级的模块631和632内的电路不再划分模块,而是通过诸如与门、与非门、或门、或非门等逻辑门组成电路。需要说明的是,图6示出的具有多层级的模块的第一电路600仅仅是一个示例,根据具体的应用场景和需求,第一电路600可包括更多的层级,并且在同一层级中可包括更多的模块。

75.在一些实施方式中,在获取到第一电路的违例路径之后,可将在最低层级上与违例路径所在模块连接的时序路径,确定为相关路径。由于处于最低层级,且与违例路径所在模块具有连接关系的模块通常与违例路径所在模块在逻辑功能上关联性较强,因此可将这些时序路径确定为违例路径的相关路径,并在后续步骤中针对相关路径进行修正。

76.应当指出,上文描述确定相关路径的过程,可例如通过编写相应的脚本/程序来实现。

77.s522,生成与违例路径及其相关路径对应的多个第二电路。

78.在第一电路不满足时序要求情况下,可对违例路径及其相关路径中的电路设计(例如,门级网表)进行修正以生成修正后的多个第二电路。换言之,多个第二电路中的每一个是根据违例路径及其相关路径得到的电路。例如,针对每条违例路径进行修正可得到多个修正路径,针对每条相关路径进行修正可得到多个相关修正路径,遍历每条违例路径及其对应的多个修正路径以及每条相关路径及其对应的多个相关修正路径,得到上述多个修正路径和多个相关修正路径各种组合后的多个修正电路,每个第二电路可包括各个修正电路与第一电路中除了违例路径和相关路径之外的其它电路。其中,可按照上文详细描述的确定修正路径的方法来确定相关路径对应的相关修正路径。

79.根据本技术实施方式提供的电路时序优化方法,例如通过编写相应的脚本/程序的方式使电路时序优化方法借助于eda工具标准化地执行,能够应对在人为修正过程中的反复迭代操作导致的效率较低、人力开销较大的问题,同时可降低时序优化的出错概率,提升时序优化的效率。另外,由于相关路径和违例路径在逻辑功能上关联性较强,通过在获取违例路径之后确定出相关路径,并在针对违例路径及其相关路径修正生成第二电路,有利于提高第二电路通过形成验证的概率,并且有利于获得更多可选的目标优化电路。

80.本技术的实施方式还提供了一种电路时序优化装置。图7是根据本技术示例性实施方式的电路时序优化装置700的框图。例如,电路时序优化装置700可部署在客户端或者服务器上。

81.如图7所示,时序优化装置700包括获取模块710、生成模块720、验证模块730、确定模块740。具体而言,获取模块710被配置为获取第一电路的违例路径。生成模块720被配置为生成与第一电路的违例路径对应的多个第二电路。验证模块730被配置为将多个第二电路与所述第一电路进行形式验证。确定模块740被配置为将通过了形式验证且不存在违例路径的第二电路确定为目标优化电路。应当指出,电路时序优化装置700可以以软件、硬件或软硬件相结合的方式实现。多个不同模块可在同一软件或硬件结构中实现,或者一个模块可以由多个不同的软件或硬件结构实现。上文中参照图1至6描述的处理内容同样适合于上述对应的各个模块,出于简要的目的,不再赘述。

82.本技术的实施方式还提供一种电子设备。图8是根据本技术的示例性实施方式的电子设备800的框图。电子设备800可被实现为个人计算机、台式计算机、多屏幕计算机、膝上型计算机、上网本等计算机类设备。电子设备800可用于实现执行例如图1中所描述的电路时序优化方法100中的各个步骤。如图8所示,电子设备800包括处理器811,其可以根据存储在只读存储器(rom) 812中的计算机程序指令或者从存储器818加载到随机存取存储器(ram) 813中的计算机程序指令,来执行各种适当的步骤和处理。在ram 813中,还可存储电子设备800操作所需的各种程序和数据。处理器811、rom 812以及ram 813通过总线814彼此

相连。输入/输出(i/o)接口815也连接至总线814。

83.电子设备800中的多个部件连接至i/o接口815,包括:输入单元816,例如键盘、鼠标、触控板等;输出单元817,例如各种类型的显示器、扬声器等;存储器818,例如磁盘、光盘等;以及通信单元819,例如网卡、调制解调器、无线通信收发机等。通信单元819允许电子设备800通过诸如因特网的计算机网络和/或各种电信网络与其它设备交换信息/数据。

84.处理器811可以是各种具有处理和计算能力的通用和/或专用处理部件。处理器811的一些示例包括但不限于中央处理单元(cpu)、图形处理单元(gpu)、各种专用的人工智能(ai)计算芯片、各种运行机器学习模型算法的处理器、数字信号处理器(dsp)、以及任何适当的处理器、控制器、微控制器等。处理器811可以执行上文所描述的各个方法和处理,例如电路时序优化方法100。在一些实施方式中,电路时序优化方法100可被实现为计算机软件程序,其被存储于机器可读介质,例如存储器818。

85.在一些实施方式中,计算机程序的部分或者全部可以经由rom 812和/或通信单元819而被载入和/或安装到电子设备800上。当计算机程序加载到ram 813并由处理器811执行时,可以执行上文描述的电路时序优化方法100中的一个或多个步骤。可选地,在其它实施方式中,处理器811可以通过其它任何适当的方式(例如,借助于固件)而被配置为执行方法800中的一个或多个步骤。

86.本技术的实施方式还提供一种计算机可读存储介质,存储有计算机程序。计算机程序被处理器执行时实现上述实施方式提及的电路时序优化方法。即,本领域技术人员可以理解,实现上述方法实施方式中的全部或部分步骤是可以通过程序来指令相关的硬件来完成,该程序存储在一个存储介质中,包括若干指令用以使得一个设备(可以是单片机,芯片等)或处理器执行本技术各个实施例所述方法的全部或部分步骤。而前述的存储介质包括:u盘、移动硬盘、只读存储器、随机存取存储器、磁碟或者光盘等各种可以存储程序代码的介质。

87.以上描述仅为本技术的较佳实施方式以及对所运用技术原理的说明。本领域技术人员应当理解,本技术中所涉及的发明范围,并不限于上述技术特征的特定组合而成的技术方案,同时也应涵盖在不脱离所述发明构思的情况下,由上述技术特征或其等同特征进行任意组合而形成的其它技术方案。例如上述特征与本技术中公开的(但不限于)具有类似功能的技术特征进行互相替换而形成的技术方案。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1