一种裸片和时钟同步方法与流程

本技术实施例涉及芯片,尤其涉及一种裸片和时钟同步方法。

背景技术:

1、随着半导体器件尺寸微缩的物理极限的到来,芯粒/三维(chiplet/3d)架构作为延续摩尔定律的主要方案快速推进,在科研界和产业界的研究越来越多。在产业界,chiplet/3d产品的需求,促进了半导体工艺、封装工艺以及设计等领域的商业化进程。

2、其中,异质集成技术灵活且成本最优。在异质集成场景中,多颗裸片的工艺跨度较大,要求即插即用,且需保障产品所需的系统延迟、接口速率、带宽和功耗等,同时需兼顾芯片系统难度。如何兼顾异质集成场景下性能和芯片系统难度的问题,仍亟待解决。

技术实现思路

1、本技术实施例提供一种裸片和时钟同步方法,第一裸片和一个第二裸片通过信号通路耦合以形成环路,可以实现芯片系统的时钟全同步。其中控制电路和时钟信号调节电路均设置于第一裸片中,可以减少第二裸片的复杂度,解决了第二裸片适配的问题。

2、为达到上述目的,本技术实施例采用如下技术方案。

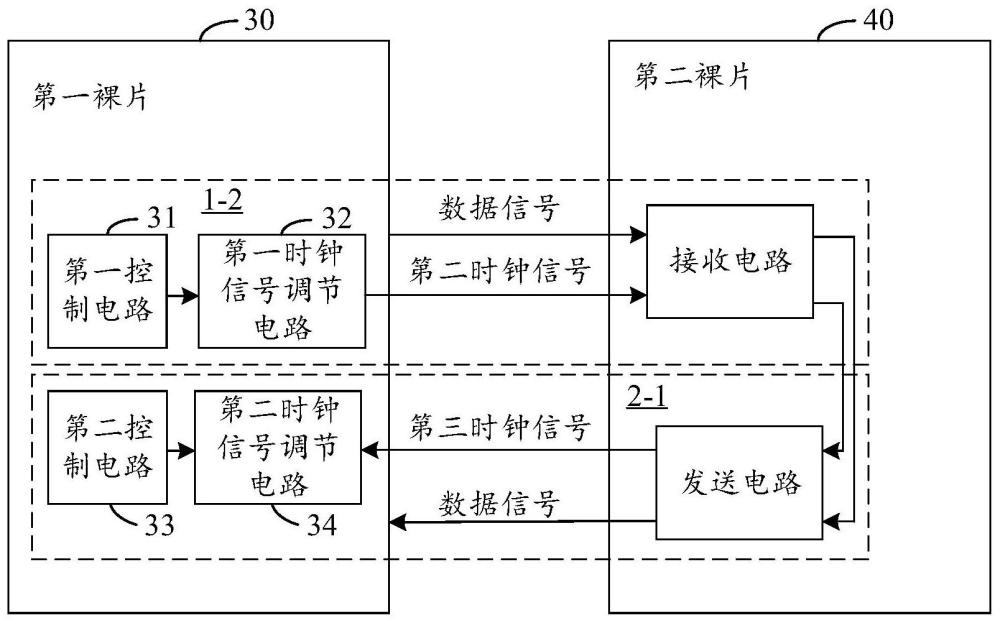

3、第一方面,本技术实施例提供一种第一裸片,第一裸片包括至少一个信号通路,每个信号通路用于和一个第二裸片耦合以形成环路,每个信号通路包括信号发送通路和信号接收通路,信号发送通路包括第一控制电路和第一时钟信号调节电路,信号接收通路包括第二控制电路和第二时钟信号调节电路;第一控制电路,用于在向第二裸片发送数据信号时,控制第一时钟信号调节电路调节第一裸片的第一时钟信号的相位,得到第二时钟信号,以向第二裸片发送第二时钟信号;第二控制电路,用于控制第二时钟信号调节电路调节接收的第三时钟信号的相位以得到第四时钟信号,以基于第四时钟信号从第二裸片接收数据信号,其中,第二裸片中的第二时钟信号和第三时钟信号未经过相位调节和频率调节。其中,第一裸片为主裸片,第二裸片为从裸片。

4、由此,第一裸片和每个第二裸片通过信号通路耦合以形成环路,第一裸片中的第二时钟信号可跟随数据信号发送至第二裸片中,第二裸片基于第二时钟信号采样该数据信号。另外,第一裸片可以接收第二裸片的第三时钟信号,第二裸片中的第二时钟信号和第三时钟信号未经过相位调节和频率调节,即第二裸片仅作为时钟信号的通路,而不对时钟信号进行相位调节和频率调节。由此,可以实现芯片系统的时钟全同步。另外,第一控制电路、第二控制电路、第一时钟信号调节电路和第二时钟信号调节电路均位于第一裸片中,第二裸片中仅涉及数据信号的通路和时钟信号的通路,从而可以降低第二裸片的电路设计难度。当芯片系统中第二裸片的工艺类型较多时,只需要第二裸片的接口能兼容第一裸片的接口即可。由于时钟信号的调节均在第一裸片中完成,从而使第二裸片的适配更为简单便捷,可以实现即插即用的效果。由此,可以解决兼顾性能和芯片系统难度的问题。

5、在一种可能的设计中,第一裸片和多个第二裸片设置于同一封装内。

6、这种设计中,第一裸片和多个第二裸片设置于同一封装内,形成3d堆叠架构,其中,第一裸片可以包括3d堆叠结构中的控制电路和时钟信号调节电路,第二裸片仅涉及数据信号的通路和时钟信号的通路,从而降低第二裸片的电路设计难度,另外,第一裸片也可以兼容不同工艺的第二裸片。

7、在一种可能的设计中,至少一个信号通路包括第一信号通路,第一信号通路用于通过至少一个裸片中的通孔和第二裸片耦合以形成环路。

8、这种设计中,芯片系统中第一裸片通过至少一个裸片中的通孔和第二裸片耦合,即通过直通的互联方式形成环路,可以减少第二裸片的设计复杂度,芯片系统集成和调节的难度也大幅降低,兼容度大大提升。

9、在一种可能的设计中,信号发送通路包括数据发送通路和时钟发送通路,时钟发送通路包括第一控制电路和第一时钟信号调节电路,数据发送通路用于向第二裸片发送数据信号,时钟发送通路中的第一控制电路用于控制第一时钟信号调节电路调节第一裸片的第一时钟信号的相位,得到第二时钟信号,以向第二裸片发送第二时钟信号;信号接收通路包括数据接收通路和时钟接收通路,时钟接收通路包括第二控制电路和第二时钟信号调节电路,数据接收通路用于接收第二裸片发送的数据信号,时钟接收通路中的第二控制电路用于控制第二时钟信号调节电路调节接收的第三时钟信号的相位以得到第四时钟信号,以基于第四时钟信号从第二裸片接收数据信号,其中,第二裸片中的第二时钟信号和第三时钟信号未经过相位调节和频率调节。

10、这种设计中,第一裸片和每个第二裸片之间耦合形成环路,构建了芯片系统的全同步时钟网络,极大地提升了芯片系统的延迟,提高了芯片系统的带宽以及降低了芯片系统的功耗。

11、在一种可能的设计中,数据发送通路包括第一寄存器、第二寄存器和第一缓存器;第一寄存器的输出端和第二寄存器的输入端耦合,第二寄存器的输出端和第一缓存器的输入端耦合,第一缓存器的输出端和第二裸片耦合。

12、这种设计中,数据发送通路包括寄存器和缓存器,其中,第一寄存器和第二寄存器可以是数据寄存器,用于暂时存放数据信号和传递数据信号。第一缓存器可以是输出缓存器,第一缓存器可以用于暂时存放第一裸片发送至第二裸片的数据信号。

13、在一种可能的设计中,第一裸片还包括时钟电路;时钟发送通路还包括第二缓存器,第一时钟信号调节电路的输入端和时钟电路的输出端耦合,第一时钟信号调节电路的输出端和第二缓存器的输入端耦合,第二缓存器的输出端和第二裸片耦合。

14、这种设计中,时钟发送通路中也包括缓存器。第二缓存器可以是输出缓存器,第二缓存器可以用于暂时存放第一裸片发送至第二裸片的第二时钟信号。若第一裸片为高速工作的裸片,第二裸片为低速工作的裸片,通过设置第一缓存器和第二缓存器可以实现第一裸片和第二裸片间的数据信号和时钟信号的协调和缓冲,实现数据信号和时钟信号传输的同步。

15、在一种可能的设计中,数据接收通路包括第三缓存器、第三寄存器和第四寄存器;第三缓存器的输入端和第二裸片耦合,第三缓存器的输出端和第三寄存器的输入端耦合,第三寄存器的输出端和第四寄存器的输入端耦合。

16、这种设计中,第三寄存器和第四寄存器可以是数据寄存器,用于暂时存放数据信号和传递数据信号。第三缓存器可以是输入缓存器,第三缓存器可以用于暂时存放第二裸片发送至第一裸片的数据信号。

17、在一种可能的设计中,第一裸片还包括时钟电路;时钟接收通路包括第四缓存器;第四缓存器的输入端和第二裸片耦合,第四缓存器的输出端和第二时钟信号调节电路的输入端耦合,第二时钟信号调节电路的输出端和第三寄存器的控制端耦合。

18、这种设计中,第四缓存可以是输入缓存器,第四缓存器可以用于暂时存放第二裸片发送至第一裸片的第二时钟信号。若第一裸片为高速工作的裸片,第二裸片为低速工作的裸片,通过设置第三缓存器和第四缓存器可以实现第二裸片和第一裸片间的数据信号和时钟信号的协调和缓冲,实现数据信号和时钟信号传输的同步。

19、这种设计中,控制器也集成于第一裸片中,可以降低第二裸片的设计复杂度。以及第一时钟信号调节电路和第二时钟信号调节电路也集成于第一裸片中,第一时钟信号调节电路和第二时钟信号调节电路可以在芯片系统集成完成后调节时钟信号的相位,可以减少设计余量,提高接口频率,从而提高了带宽。

20、在一种可能的设计中,第一控制电路还用于基于信号发送通路的时序窗口配置第一时钟信号调节电路调节的相位;第二控制电路还用于基于信号接收通路的时序窗口配置第二时钟信号调节电路调节的相位。

21、这种设计中,第一时钟信号调节电路和第二时钟信号调节电路可以在芯片系统集成完成后调节时钟信号的相位,可以减少设计余量,提高接口频率,从而提高带宽。

22、另外,考虑到裸片的工艺偏差等情况,应先配置第一时钟信号调节电路调节的相位,保证第一裸片向第二裸片发送数据信号的时序窗口最大。再配置第二时钟信号调节电路调节的相位,保证第二裸片向第一裸片发送数据信号的时序窗口最大。从而完成第一裸片发送和接收时的时序窗口配置,保证数据信号能够正确传输。

23、第二方面,本技术实施例提供一种时钟同步方法,该方法应用于第一裸片,第一裸片包括至少一个信号通路,每个信号通路用于和一个第二裸片耦合以形成环路,每个信号通路包括信号发送通路和信号接收通路,信号发送通路包括第一控制电路和第一时钟信号调节电路,信号接收通路包括第二控制电路和第二时钟信号调节电路;该方法包括:在向第二裸片发送数据信号时,控制第一控制电路以控制第一时钟信号调节电路调节第一裸片的第一时钟信号的相位,得到第二时钟信号,以向第二裸片发送第二时钟信号;控制第二控制电路以控制第二时钟信号调节电路调节接收的第三时钟信号的相位以得到第四时钟信号,以基于第四时钟信号从第二裸片接收数据信号,其中,第二裸片中的第二时钟信号和第三时钟信号未经过相位调节和频率调节。

24、第二方面的有益效果可参见第一方面的说明。

25、在一种可能的设计中,第一裸片和多个第二裸片设置于同一封装内。

26、在一种可能的设计中,至少一个信号通路包括第一信号通路,第一信号通路通过至少一个裸片中的通孔和第二裸片耦合以形成环路。

27、在一种可能的设计中,信号发送通路包括数据发送通路和时钟发送通路,时钟发送通路包括第一控制电路和第一时钟信号调节电路,在向第二裸片发送数据信号时,控制第一控制电路以控制第一时钟信号调节电路调节第一裸片的第一时钟信号的相位,得到第二时钟信号,以向第二裸片发送第二时钟信号包括:控制数据发送通路向第二裸片发送数据信号,以及控制第一控制电路以控制第一时钟信号调节电路调节第一裸片的第一时钟信号的相位,得到第二时钟信号,以向第二裸片发送第二时钟信号;信号接收通路包括数据接收通路和时钟接收通路,时钟接收通路包括第二控制电路和第二时钟信号调节电路,控制第二控制电路以控制第二时钟信号调节电路调节接收的第三时钟信号的相位以得到第四时钟信号,以基于第四时钟信号从第二裸片接收数据信号包括:控制数据接收通路接收第二裸片发送的数据信号,以及控制第二控制电路以控制第二时钟信号调节电路调节接收的第三时钟信号的相位以得到第四时钟信号,以基于第四时钟信号从第二裸片接收数据信号,其中,第二裸片中的第二时钟信号和第三时钟信号未经过相位调节和频率调节。

28、在一种可能的设计中,数据发送通路包括第一寄存器、第二寄存器和第一缓存器;第一寄存器的输出端和第二寄存器的输入端耦合,第二寄存器的输出端和第一缓存器的输入端耦合,第一缓存器的输出端和第二裸片耦合。

29、在一种可能的设计中,第一裸片还包括时钟电路;时钟发送通路还包括第二缓存器,第一时钟信号调节电路的输入端和时钟电路的输出端耦合,第一时钟信号调节电路的输出端和第二缓存器的输入端耦合,第二缓存器的输出端和第二裸片耦合。

30、在一种可能的设计中,数据接收通路包括第三缓存器、第三寄存器和第四寄存器;第三缓存器的输入端和第二裸片耦合,第三缓存器的输出端和第三寄存器的输入端耦合,第三寄存器的输出端和第四寄存器的输入端耦合。

31、在一种可能的设计中,第一裸片还包括时钟电路;时钟接收通路包括第四缓存器;第四缓存器的输入端和第二裸片耦合,第四缓存器的输出端和第二时钟信号调节电路的输入端耦合,第二时钟信号调节电路的输出端和第三寄存器的控制端耦合。

32、在一种可能的设计中,第一控制电路控制第一时钟信号调节电路调节第一裸片的第一时钟信号的相位包括:第一控制电路基于信号发送通路的时序窗口配置第一时钟信号调节电路调节的相位;第二控制电路控制第二时钟信号调节电路调节接收的第二时钟信号的相位包括:第二控制电路基于信号接收通路的时序窗口配置第二时钟信号调节电路调节的相位。

33、第三方面,本技术实施例提供一种芯片系统,芯片系统包括至少两个裸片,至少两个裸片包括第一裸片和第二裸片,第一裸片包括至少一个信号通路,每个信号通路用于和一个第二裸片耦合以形成环路,每个信号通路包括信号发送通路和信号接收通路;第一裸片,用于在向第二裸片发送数据信号时,控制信号发送通路调节第一裸片的第一时钟信号的相位,得到第二时钟信号,以向第二裸片发送第二时钟信号;第二裸片,用于接收第一裸片发送的数据信号和第二时钟信号;第二裸片,还用于向第一裸片发送数据信号和第三时钟信号;第一裸片,还用于控制信号接收通路调节接收的第三时钟信号的相位以得到第四时钟信号,以基于第四时钟信号从第二裸片接收数据信号,其中,第二裸片中的第二时钟信号和第三时钟信号未经过相位调节和频率调节。

34、第三方面的有益效果可参见第一方面的说明。

35、在一种可能的设计中,第一裸片和多个第二裸片设置于同一封装内。

36、在一种可能的设计中,信号发送通路包括第一控制电路和第一时钟信号调节电路,信号接收通路包括第二控制电路和第二时钟信号调节电路;第一控制电路,用于在向第二裸片发送数据信号时,控制第一时钟信号调节电路调节第一裸片的第一时钟信号的相位,得到第二时钟信号,以向第二裸片发送第二时钟信号;第二控制电路,用于控制第二时钟信号调节电路调节接收的第二时钟信号的相位以得到第四时钟信号,以基于第四时钟信号从第二裸片接收数据信号,其中,第二裸片中的第二时钟信号和第三时钟信号未经过相位调节和频率调节。

37、在一种可能的设计中,第二裸片包括接收电路和发送电路,接收电路用于接收第一裸片发送的数据信号和第二时钟信号,发送电路用于向第一裸片发送数据信号和第三时钟信号。

38、第四方面,本技术实施例提供了一种时钟同步方法,该方法应用于芯片系统,芯片系统包括至少两个裸片,至少两个裸片包括第一裸片和第二裸片,第一裸片包括至少一个信号通路,每个信号通路用于和一个第二裸片耦合以形成环路,每个信号通路包括信号发送通路和信号接收通路,该方法包括:在向第二裸片发送数据信号时,第一裸片控制信号发送通路调节第一裸片的第一时钟信号的相位,得到第二时钟信号,以向第二裸片发送第二时钟信号;第二裸片接收数据信号和第二时钟信号;向第一裸片发送数据信号时,第二裸片发送数据信号和第三时钟信号至第一裸片;第一裸片控制信号接收通路调节接收的第三时钟信号的相位以得到第四时钟信号,以及基于第四时钟信号从第二裸片接收数据信号,其中,第二裸片中的第二时钟信号和第三时钟信号未经过相位调节和频率调节。

39、第四方面的有益效果可参见第一方面的说明。

40、在一种可能的设计中,第一裸片和多个第二裸片设置于同一封装内。

41、在一种可能的设计中,至少一个信号通路包括第一信号通路,第一信号通路,用于通过至少一个裸片中的通孔和第二裸片耦合以形成环路。

42、第五方面,本技术实施例提供了一种电子设备,电子设备包括印制电路板,和第一方面的第一裸片,第一裸片和印制电路板电连接。

43、第六方面,本技术实施例提供了一种计算机可读存储介质,包括计算机指令,当计算机指令在电子设备上运行时,使得电子设备执行上述任一方面及任一项可能的实现方式中的时钟同步方法。

44、第七方面,本技术实施例提供了一种计算机程序产品,当计算机程序产品在计算机或处理器上运行时,使得计算机或处理器执行上述任一方面及任一项可能的实现方式中的时钟同步方法。

45、第八方面,本技术实施例提供了一种系统,该系统可以包括以上任一方面的任一项可能的实现方式中的无线接入设备和至少一个电子设备。该电子设备和无线接入设备可以执行上述任一方面及任一项可能的实现方式中的时钟同步方法。

46、可以理解的是,上述提供的任一种第一裸片、第二裸片、芯片系统、计算机可读存储介质或计算机程序产品等均可以应用于上文所提供的对应的方法,因此,其所能达到的有益效果可参考对应的方法中的有益效果,此处不再赘述。

47、本技术的这些方面或其他方面在以下的描述中会更加简明易懂。

- 还没有人留言评论。精彩留言会获得点赞!