处理系统、相关集成电路、设备和方法与流程

本公开的实施例涉及诸如微控制器等处理系统。

背景技术:

1、图1示出了典型的电子系统,诸如车辆的电子系统,包括多个处理系统(ps)10,诸如嵌入式系统或集成电路(例如现场可编程门阵列(fpga))、数字信号处理器(dsp)或微控制器(例如专用于汽车市场)。

2、例如,在图1中示出了通过合适的通信系统20连接的三个处理系统101、102和103。例如,通信系统可以包括车辆控制总线(诸如控制器区域网络(can)总线和/或以太网)以及经由网关连接至车辆控制总线的可能的多媒体总线(诸如媒体导向系统传输(most)总线)。通常,处理系统10位于车辆的不同位置,并且可以包括例如引擎控制单元、变速器控制单元(tcu)、防抱死制动系统(abs)、车身控制模块(bcm)和/或导航和/或多媒体音频系统。因此,一个或多个处理系统10还可以实现实时控制和调节功能。这些处理系统通常被标识为电子控制单元。

3、图2示出了示例性数字处理系统10(诸如微控制器)的框图,它可以被用作图1的任何处理系统10。

4、在所考虑的示例中,处理系统10包括经由软件指令编程的微处理器(mp)102,通常是中央处理单元(cpu)。通常,由微处理器102执行的软件被存储在非易失性程序存储器(m)104中,诸如闪存或eeprom。因此,存储器104被配置为存储处理单元102的固件,其中固件包括要由微处理器102执行的软件指令。通常,非易失性存储器104还可以被用于存储其他数据,诸如配置数据(例如校准数据)。

5、微处理器102通常还具有关联的易失性存储器(vm)104b,诸如随机存取存储器(ram)。例如,存储器104b可以被用于存储临时数据。

6、如图2所示,与存储器104和/或104b的通信通常经由一个或多个存储器控制器(mc)100执行。(多个)存储器控制器100可以被集成在微处理器102中,或者经由诸如处理系统10的系统总线等通信信道被连接至微处理器102。类似地,存储器104和/或104b可以在单个集成电路中与微处理器102集成,或者存储器104和/或104b可以是单独的集成电路的形式,并且例如经由印刷电路板的迹线被连接至微处理器102。

7、在所考虑的示例中,微处理器102可以具有从以下组中选择的关联的一个或多个(硬件)资源106:用于经由通信系统20交换数据的一个或多个通信接口if,诸如通用异步接收器/发送器(uart)、串行外围接口总线(spi)、集成电路间(i2c)、控制器区域网络(can)总线和/或以太网接口和/或调试接口;和/或一个或多个模数转换器ad和/或数模转换器da;和/或一个或多个专用数字组件dc,诸如硬件定时器和/或计数器或密码协处理器;和/或一个或多个模拟组件ac,诸如比较器、传感器(诸如温度传感器)等;和/或一个或多个混合信号分量msc,诸如pwm(脉宽调制)驱动器。

8、通常,专用数字组件dc也可以对应于集成在处理系统10中的fpga。例如,在这种情况下,存储器104还可以包括用于这种fpga的程序数据。

9、因此,数字处理系统10可以支持不同的功能性。例如,(多个)微处理器102的行为由存储在存储器104中的固件(例如由微控制器10的微处理器102执行的软件指令)确定。因此,通过安装不同的固件,相同的硬件(微控制器)可以被用于不同的应用。

10、在这方面,这种处理系统10的未来一代(例如适用于在汽车应用中使用的微控制器)预计将呈现复杂性的增加,主要是由于所请求的功能性(新协议、新特征等)的数量增加以及执行条件的严格约束(例如更低的功耗、增加的计算能力和速度等)。

11、例如,最近已经提出了更复杂的多核处理系统10。例如,这种多核处理系统可以被用于执行(并行)图1所示的若干处理系统10,诸如车辆的若干处理系统。

12、图3示出了多核处理系统10的示例。具体地,在所考虑的示例中,处理系统10包括连接至(片上)通信系统114的多个n个处理核心(pc)1021、…、102n。例如,在实时控制系统的上下文中,处理核心1021、…、102n可以是arm -r52核心。通常,通信系统114可以包括一个或多个总线系统,例如基于高级可扩展接口(axi)和/或片上网络(noc)。

13、例如,如处理核心1021的示例所示,每个处理核心102可以包括微处理器1020和通信接口1022,该通信接口1022被配置为管理微处理器1020与通信系统114之间的通信。典型地,接口1022是主接口,被配置为将给定(读取或写入)请求从微处理器1020转发到通信系统114,并且将可选响应从通信系统114转发到微处理器1020。然而,每个微处理器1020还可以具有关联的从属接口1024。例如,通过这种方式,第一微处理器1020可以(经由第一微处理器的主接口1022、通信系统114和第二微处理器的从属接口1024)向第二微处理器1020发送请求。

14、通常,每个处理核心1021、…、102n还可以包括其他本地资源,诸如一个或多个本地存储器1026,通常被标识为紧密耦合存储器(tcm)。

15、如前面提及的,典型地,处理核心1021、…、102n被布置为与非易失性存储器104和/或易失性存储器104b交换数据。在多核处理系统10中,这些存储器通常是系统存储器,诸如针对处理核心1021、…、102n共享。然而,如前面提及的,处理核心1021、…、102n中的每个处理核心可以包括一个或多个附加的本地存储器1026。

16、例如,如图3所示,处理系统10可以包括一个或多个存储器控制器100,它被配置为将至少一个非易失性存储器104和至少一个易失性存储器104b连接至通信系统114。如前面提及的,存储器104和/或104b中的一个或多个可以被集成在处理系统10的集成电路中或外部连接至集成电路。

17、如前面提及的,处理系统10可以包括一个或多个资源106,诸如一个或多个通信接口或协处理器(例如密码协处理器)。资源106通常经由相应的从通信接口1064被连接至通信系统114。例如,通过这种方式,处理核心102可以向资源106发送请求,并且资源返回给定数据。例如,为此目的,通信系统114实际上可以包括高级微控制器总线架构(amba)高性能总线(ahb)和用于将资源/外围设备106连接至amba ahb总线的高级外围总线(apb)。

18、通常,资源106中的一个或多个还可以包括相应的主接口1062,它通常也被标识为集成直接存储器访问(dma)控制器。例如,在资源106必须开始通信以便经由(读取和/或写入)请求与连接至通信系统114的另一电路(诸如存储器104/104b、资源106或处理核心102)交换数据的情况下,这种主接口1062可能是有用的。

19、通常,这种处理系统10还包括一个或多个通用直接存储器访问(dma)控制器110。通常,通用dma控制器110可以包括连接至资源106的至少一个功能信道。通常,与给定信道相关联的资源106还可以根据配置数据来选择。具体地,信道是读取或写入信道(也可以是可编程的),并且通常具有关联的配置数据,这些配置数据指示:在读取信道的情况下,dma控制器110应该从中读取数据的存储器地址范围;以及在写入信道的情况下,dma控制器110应该向其写入数据的存储器地址范围。

20、例如,通过这种方式,通信接口if可以经由两个信道被连接至dma控制器110:读取信道,被配置为自主地读取要从存储器104b中的第一存储器范围传输的数据,并且将已经读取的数据提供给通信接口if(通信接口if然后传输相应的数据);以及写入信道,被配置为接收已经从通信接口if接收的数据,并且自主地将这些数据写入存储器104b中的第二存储器范围。

21、因此,dma控制器110通常具有用于向存储器控制器100传输读取或写入请求的关联的主接口1102。通常,为此目的,主接口1102可以经由专用dma信道被直接连接至存储器控制器110,或者主接口1102可以向通信系统114发送请求。例如,在后一种情况下,读取和写入请求可以包括由通信系统114管理的任何地址。

22、类似地,代替经由专用信道直接与资源106接口连接,通用dma控制器110也可以被配置为经由通信系统114与资源106交换数据。例如,在这种情况下,dma控制器110可以被配置为首先经由主接口1102发送包括第一地址的读取请求,然后发送包括第二地址的写入请求。

23、因此,通用dma控制器110通常还包括用于接收用于配置dma控制器110的配置数据的从属接口1104。

24、典型地,从属接口(例如接口1024、1064和/或1104)被配置为接口连接相应的电路的一个或多个寄存器。例如,这些寄存器可以被用于存储相应的电路的配置数据和/或其他资源特定数据,诸如在通信接口的情况下要传输或接收的数据或在adc的情况下采样的数据。

25、具体地,虽然从属接口被示出为集成在相应的电路中的块,但实际上,给定电路也可以仅包括到电路的一个或多个寄存器的寄存器接口,这通常是所谓的ip核心的情况。因此,在这种情况下,从属接口可以被配置为将经由通信系统114交换的请求转换为对这些一个或多个寄存器的读取或写入操作。因此,从属接口确实可以是通信系统114的一部分,或者部分地在通信系统114内并且部分地在相应的电路中实现。

26、例如,通常每个读取或写入请求包括地址,其中通信系统114的单一地址与每个寄存器相关联。典型地,通信系统114的地址范围被标识为处理系统10的物理地址范围。因此,从属接口可以被配置为管理一个或多个寄存器,并且检测包括与由从属接口管理的寄存器相关联的地址的请求。在读取请求的情况下,从属接口因此可以读取与请求中所包括的地址相关联的寄存器的内容,并且将相应的内容(例如经由相应的响应消息)发送给通信系统114。相反,在读取请求的情况下,从属接口可以将写入请求中所包括的数据存储到与请求中所包括的地址相关联的寄存器。例如,为此目的,给定的从属接口可以经由总线114监测通信交换。相反,在系统互连的情况下,诸如网络互连控制器(nic)或noc,从属接口的至少一部分确实可以在系统互连114和相应的电路之间的nic或noc通信接口中实现。

27、本发明人已经观察到,处理系统10的各种电路的寄存器也可以存储数据,从安全角度来看,这些数据可能是相关的。例如,这适用于处理核心102、资源106或dma控制器110的一个或多个寄存器。

28、在这方面,多核处理系统和/或执行不同软件任务甚或虚拟机的处理系统内的访问保护通常通过向每个处理核心102、每个虚拟机和/或每个软件任务指派访问权限来管理。例如,在许多处理系统10中,这个问题通过使用软件和/或硬件地址范围保护来解决。

29、例如,arm aarch64架构可以使用虚拟存储器系统架构(vmsa),其中每个处理核心102的存储器管理单元(mmu)被用于经由所谓的转化表(ttb)将虚拟地址(va)映射到通信系统114的物理地址(pa)。由于通信系统114的物理地址范围与存储器104和/或104b以及资源106中的存储器范围相关联,因此可以将给定应用app或操作系统os的读写访问权限限制到给定的存储器范围和/或资源106。

30、相反,arm aarch32通常使用受保护存储器系统架构(pmsa)而不是vmsa。在这种情况下,处理系统包括存储器保护单元(mpu)。具体地,代替定义虚拟地址到物理地址的映射,mpu允许例如经由表格指定物理地址空间中的一个或多个存储器区域,并且允许指定相应的访问权限和存储器属性。例如,os和应用app的该访问权限表可以在异常级别el1中实现。

31、因此,通过使用mmu或mpu,处理系统10被配置为选择性地禁止从主接口(诸如处理核心102的主接口1022)向通信系统114转发请求。相反,对应于2022年5月4日提交的美国专利申请号17/736,590和公开的欧洲申请ep 4086763(通过引用并入本文)的意大利专利申请号102021000011639公开了一种解决方案,其中一个或多个从属接口实现固件功能,使得从属接口本身被配置为选择性地禁止从通信系统114向相应的电路转发请求。

32、因此,这些解决方案允许定义访问权限,该访问权限可以被用于确定写入请求是否对应于由授权处理核心、虚拟机和/或软件任务生成的授权写入请求。然而,这些解决方案无法验证授权写入请求是否确实是由误差或无意生成的。

33、鉴于上文,本领域需要提供用于管理对包含安全相关数据的寄存器的写入访问的改进的解决方案。

技术实现思路

1、一个或多个实施例涉及一种处理系统。而且,实施例涉及一种相关的集成电路、设备和方法。

2、该处理系统包括具有给定物理地址范围的通信系统和处理核心,该处理核心包括被配置为执行软件指令并且具有关联的主接口电路的微处理器,该主接口电路被配置为从微处理器向通信系统转发写入请求,其中写入请求包括物理地址范围的物理地址和要被写入到物理地址的数据。

3、因此,电路可以具有关联的从属接口电路,被配置为管理地址子范围并且选择性地将寻址到给定地址的写入请求从通信系统转发到电路。例如,电路可以包括一个或多个寄存器以及被配置为与一个或多个寄存器交换数据的一个或多个外围电路。在这种情况下,相应的给定地址可以与一个或多个寄存器中的每个寄存器相关联,并且从属接口电路可以被配置为通过确定与从写入请求中提取的地址相关联的寄存器并且将从写入请求中提取的数据存储到相应的寄存器来选择性地转发写入请求。例如,在各种实施例中,从属接口电路是外围桥接器,其中一个或多个寄存器经由外围总线被连接至从属接口电路。

4、在各种实施例中,从属接口电路具有指示给定地址是受保护还是未受保护的关联配置数据,并且包括(易失性)存储器(诸如用寄存器实现),用于存储指示给定地址被锁定还是被解锁的附加配置数据。例如,配置数据可以针对一个或多个寄存器中的每个寄存器指示相应的地址是受保护的还是未受保护的。

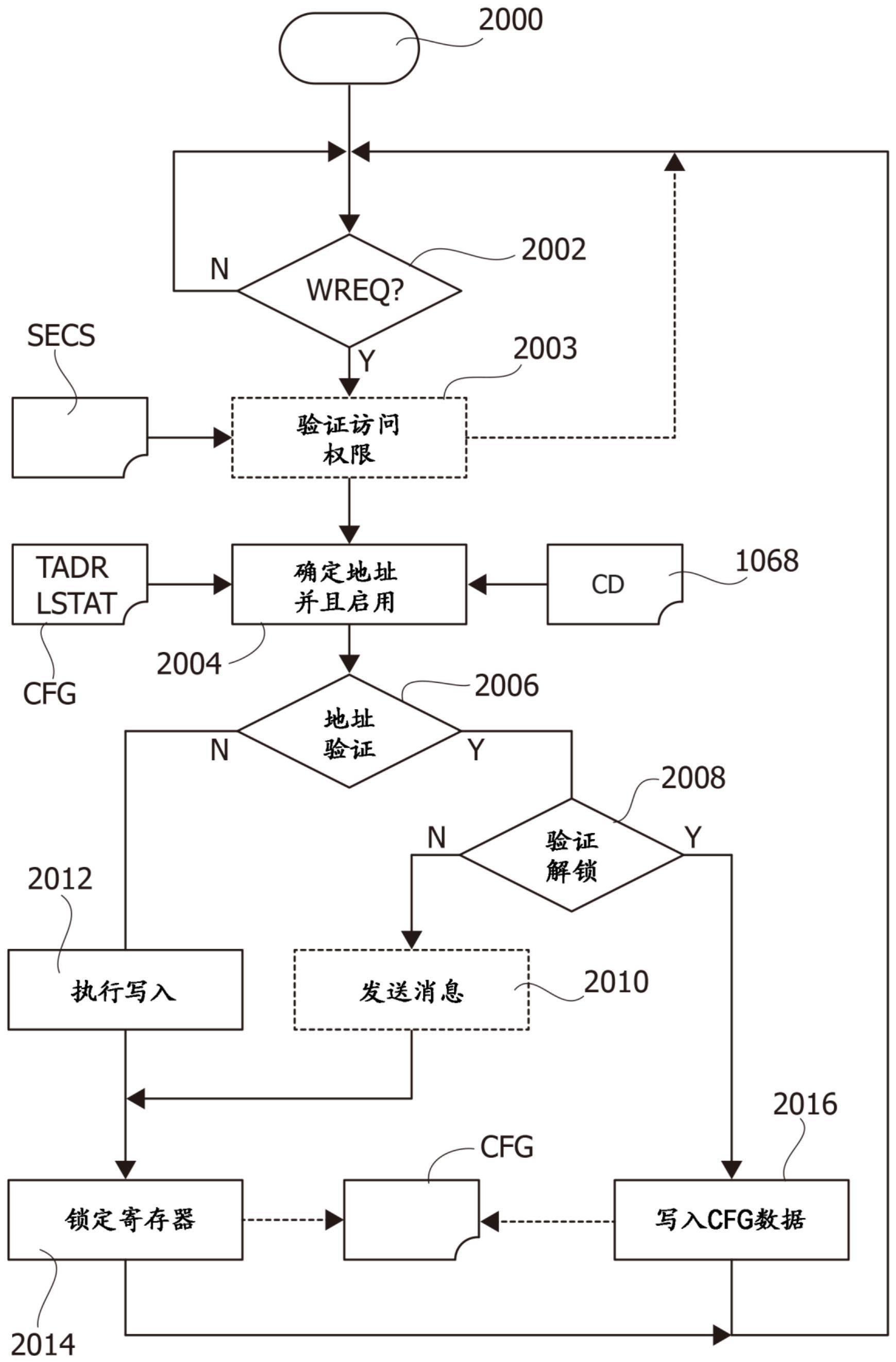

5、具体地,在各种实施例中,从属接口电路被配置为:从通信系统接收寻址到给定地址的写入请求,从接收到的写入请求中提取相应的地址和数据,并且确定配置数据指示所提取的地址是受保护的还是未受保护的以及附加配置数据指示所提取的地址被锁定还是被解锁。

6、具体地,响应于确定提取的地址未受保护或提取的地址被解锁,从属接口电路可以向电路转发写入请求。相反,响应于确定所提取的地址是受保护的并且所提取的地址被锁定,从属接口电路经由组合逻辑操作生成解锁信号。

7、具体地,在各种实施例中,组合逻辑操作被配置为将提取的地址与提取的数据进行比较,从而当提取的数据满足相对于提取的地址的预定规则时断言解锁信号。因此,在各种实施例中,当写入请求中所包括的数据满足相对于写入请求中所包括的相应的地址的给定规则时,保护可以被解锁,从而避免了给定保护被无意解锁的风险。例如,在各种实施例中,从属接口电路被配置为:通过将提取的地址的一个或多个比特与提取的数据的一个或多个比特进行比较来生成解锁信号。更具体地,在各种实施例中,从属接口电路被配置为:当所提取的地址对应于所提取的数据时断言解锁信号。

8、因此,当解锁信号被断言时,从属接口电路可以更新附加配置数据,以便指示所提取的地址被解锁。例如,在各种实施例中,附加配置数据包括临时地址值。在这种情况下,从属接口电路可以通过将提取的地址存储为临时地址值来解锁提取的地址。例如,在这种情况下,从属接口电路可以通过将提取的地址与临时地址信号进行比较来确定提取的地址是被锁定还是被解锁。

9、相反,当解锁信号被解除断言时,从属接口电路可以更新附加配置数据,以便指示所提取的地址被锁定。例如,为了锁定所提取的地址,从属接口电路可以更新附加配置数据,以便指示由从属接口地址管理的所有地址都被锁定。

10、在各种实施例中,响应于确定所提取的地址未受保护或所提取的地址被解锁,这意味着写入请求被转发,从属接口电路还可以更新附加配置数据,以指示所提取的地址被锁定,从而一旦写入请求被执行,就再次锁定地址。

- 还没有人留言评论。精彩留言会获得点赞!