一种数据库排序方法、装置、排序加速板卡及介质与流程

本发明涉及数据处理,特别涉及一种数据库排序方法、装置、排序加速板卡及介质。

背景技术:

1、排序是一种非常重要的计算核心,在数据库、图像处理和基因组分析等许多领域都得到了应用,同时,排序也是许多计算问题的瓶颈,追求快速稳定的大规模排序一直是许多应用的优化目标。随着移动技术的进步,物联网(internet of things,即iot)时代即将到来,未来不仅需要在服务器等高性能系统上,还需要在嵌入式系统等低计算性能机器上都可以使用的排序方法。基于cpu(central processing unit,中央处理器)的软件排序方法往往无法挖掘具有并行特征的计算密集型排序算法的潜力,并且,大数据量排序过程需要占用过多的cpu资源和内存资源,造成cpu和内存资源占用过重,与数据库核心进程进行资源竞争,严重拉低数据库的整体性能表现。

2、综上,如何加快数据库的排序过程,以提高排序效率,以及提高数据库的整体性能是目前有待解决的问题。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种数据库排序方法、装置、排序加速板卡及介质,能够加快数据库的排序过程,以提高排序效率,以及提高数据库的整体性能。其具体方案如下:

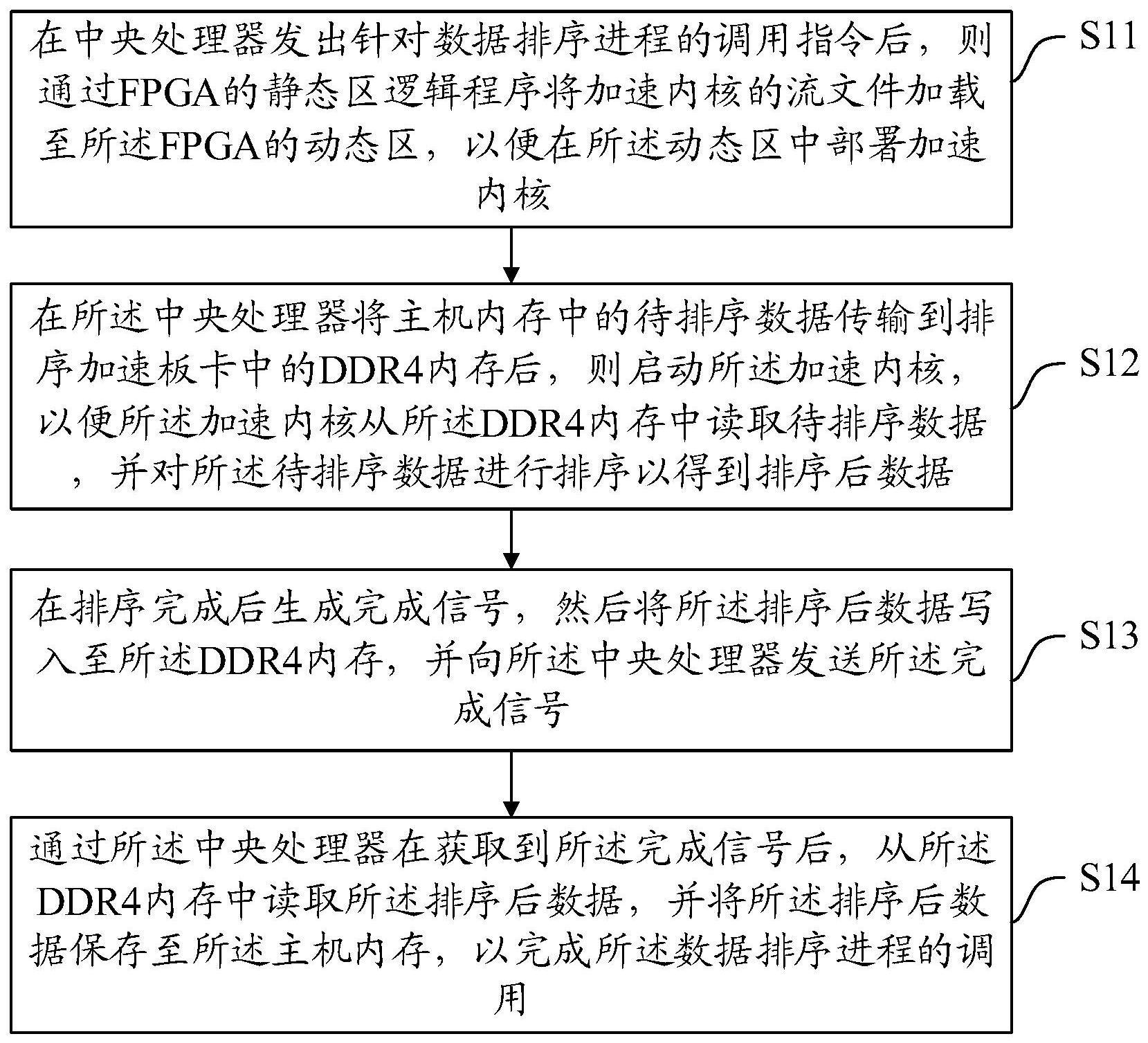

2、第一方面,本技术公开了一种数据库排序方法,包括:

3、在中央处理器发出针对数据排序进程的调用指令后,则通过fpga的静态区逻辑程序将加速内核的流文件加载至所述fpga的动态区,以便在所述动态区中部署加速内核;

4、在所述中央处理器将主机内存中的待排序数据传输到排序加速板卡中的ddr4内存后,则启动所述加速内核,以便所述加速内核从所述ddr4内存中读取待排序数据,并对所述待排序数据进行排序以得到排序后数据;

5、在排序完成后生成完成信号,然后将所述排序后数据写入至所述ddr4内存,并向所述中央处理器发送所述完成信号;

6、通过所述中央处理器在获取到所述完成信号后,从所述ddr4内存中读取所述排序后数据,并将所述排序后数据保存至所述主机内存,以完成所述数据排序进程的调用。

7、可选的,所述在中央处理器发出针对数据排序进程的调用指令的过程中,还包括:

8、获取所述中央处理器发送的控制参量;其中,所述控制参量包括开始信号、ddr4偏移地址和数据量大小。

9、可选的,所述启动所述加速内核,以便所述加速内核从所述ddr4内存中读取待排序数据,包括:

10、启动所述加速内核,并确定所述控制参量中的ddr4偏移地址,以便所述加速内核基于所述ddr4偏移地址,并通过axi总线从所述ddr4内存中读取待排序数据。

11、可选的,所述将所述排序后数据写入至所述ddr4内存,包括:

12、基于所述ddr4偏移地址将所述排序后数据写入至所述ddr4内存。

13、可选的,所述在所述动态区中部署加速内核,包括:

14、在所述动态区中部署与不同排序方法对应的加速内核;所述排序方法包括双调排序、奇偶排序、基数排序和归并排序;

15、相应的,所述对所述待排序数据进行排序以得到排序后数据,包括:

16、按照预先设置的排序方法,并基于所述控制参量对所述待排序数据进行排序以得到排序后数据。

17、可选的,所述对所述待排序数据进行排序以得到排序后数据,包括:

18、确定加速内核预先配置的空间工作模式和时间工作模式;其中,所述空间工作模式包括并行工作模式、串行工作模式和局部并串行工作模式,所述时间工作模式

19、按照所述空间工作模式和所述时间工作模式对所述待排序数据进行排序以得到排序后数据。

20、可选的,所述数据库排序方法,还包括:

21、若所述空间工作模式为并行工作模式,则启动若干个加速内核,并确定所述中央处理器为每一所述加速内核分配的不同的ddr4偏移地址,以便各所述加速内核分别基于对应的ddr4偏移地址从所述ddr4内存中读取待排序数据,以对所述待排序数据进行排序得到排序后数据;

22、若所述空间工作模式为串行工作模式,则确定预先设置的多条件排序语句中的排序条件个数,并启动相应数量个加速内核,以便将各排序条件分配给不同的加速内核,然后根据所述多条件排序语句的顺序依次调用对应的加速内核对从所述ddr4内存中读取到的待排序数据进行排序得到排序后数据;

23、若所述空间工作模式为局部并串行工作模式,则确定所述中央处理器对所述待排序数据进行拆分得到的若干个数据块,并启动相应数量个加速内核,以便各所述加速内核对从所述ddr4内存中读取到的所述数据块进行排序得到排序结果,然后利用归并排序方法对各排序结果进行合并以得到排序后数据。

24、第二方面,本技术公开了一种数据库排序装置,包括:

25、内核部署模块,用于在中央处理器发出针对数据排序进程的调用指令后,则通过fpga的静态区逻辑程序将加速内核的流文件加载至所述fpga的动态区,以便在所述动态区中部署加速内核;

26、数据排序模块,用于在所述中央处理器将主机内存中的待排序数据传输到排序加速板卡中的ddr4内存后,则启动所述加速内核,以便所述加速内核从所述ddr4内存中读取待排序数据,并对所述待排序数据进行排序以得到排序后数据;

27、数据写入模块,用于在排序完成后生成完成信号,然后将所述排序后数据写入所述ddr4内存,并向所述中央处理器发送所述完成信号;

28、数据保存模块,用于通过所述中央处理器在获取到所述完成信号后,从所述ddr4内存中读取所述排序后数据,并将所述排序后数据保存至所述主机内存,以完成所述数据排序进程的调用。

29、第三方面,本技术公开了一种排序加速板卡,包括:

30、存储器,用于保存计算机程序;

31、处理器,用于执行所述计算机程序,以实现前述公开的数据库排序方法的步骤。

32、第四方面,本技术公开了一种计算机可读存储介质,用于存储计算机程序;其中,所述计算机程序被处理器执行时实现前述公开的数据库排序方法的步骤。

33、可见,本技术在中央处理器发出针对数据排序进程的调用指令后,则通过fpga的静态区逻辑程序将加速内核的流文件加载至所述fpga的动态区,以便在所述动态区中部署加速内核;在所述中央处理器将主机内存中的待排序数据传输到排序加速板卡中的ddr4内存后,则启动所述加速内核,以便所述加速内核从所述ddr4内存中读取待排序数据,并对所述待排序数据进行排序以得到排序后数据;在排序完成后生成完成信号,然后将所述排序后数据写入至所述ddr4内存,并向所述中央处理器发送所述完成信号;通过所述中央处理器在获取到所述完成信号后,从所述ddr4内存中读取所述排序后数据,并将所述排序后数据保存至所述主机内存,以完成所述数据排序进程的调用。由此可见,本技术当中央处理器调用数据排序进程时,fpga的静态区逻辑程序则将加速内核的流文件加载到fpga的动态区,以完成加速内核在动态区中的部署。中央处理器将主机内存中的待排序数据传输到排序加速板卡中的ddr4内存后,则启动加速内核,加速内核从ddr4内存中读取待排序数据并开始排序,加速内核完成排序后生成完成信号,并发送完成信号至中央处理器,以及将排序后数据写入ddr4内存。中央处理器收到完成信号后,将排序后数据从ddr4内存中读回主机内存,结束进程调用。上述方案通过使用fpga对数据库的排序过程进行加速,提高了排序效率,解放了数据库的排序进程,提高了数据库的整体性能。此外,由于排序过程并非是在中央处理器中进行的,减少了对中央处理器资源和内存资源的占用。

- 还没有人留言评论。精彩留言会获得点赞!