一种AMP模式下基于两次信息交互的多核处理器容错方法与流程

本发明涉及嵌入式多核处理器的冗余容错方法,尤其是涉及基于两次信息交换的嵌入式多核处理器在非对称多核(asymmetric multiprocessing,amp)模式下的冗余容错方法。

背景技术:

1、amp模式是指处理器中的每一个处理器核都拥有自己的操作系统或应用程序,拥有各自独立的内存空间。处理器核之间只有少量信息交互。在amp模式下,处理器各核运行的操作系统或应用程序可能是相同的,也可能是不同的,即各核的功能可能是相同的,也可能是不同的。

2、一般多核处理器包括双核、4核及更多的核。对于双核,通常确保可靠性和安全性的做法是采用双核锁步工作方式。两个核在一定同步策略约束下,分别运行同样的程序。对两个核的处理结果进行对比,只有两个核处理结果一致才会对外输出,否则就不会输出,以确保系统安全。其它多核处理器,超过4个核的一般会对处理器核进行分组,通常每组4核。对于4核处理器,一般采用三模冗余(triple module redundancy,tmr)技术或2x2锁步技术。tmr利用三取二进行表决,得到正确输出结果。也可以进一步采用如(tmr+1)的方式,即利用多出来的核作为替补,用来动态替换故障核。2x2锁步将处理器分为两组处理器核对,每一组处理器核均采用双核锁步工作方式。若其中一组输出不一致,则切到另外一组。

3、但是,基于双核锁步机制的容错方法不能区分是哪个核故障,一旦对比结果不同,这一组就得抛弃,处理器核的资源利用率低。虽然处理器不会输出错误结果而导致安全问题,但在组与组切换,或者系统回卷或复位恢复时,处理器的任务会被打断。tmr机制可以定位故障并以多出来的健康核代替故障核。但由于故障核出现的位置不可预知,tmr中处理器核动态替换的设计会使得系统变得比较复杂。核越多,系统复杂度越高,有可能引入其它可靠性问题。此外,tmr进行三取二表决的表决器是一个单点,一旦表决器出现问题,即使多核功能都正确,处理器也无法正常工作。

技术实现思路

1、本发明的技术解决问题是:克服现有技术的不足,提供了一种amp模式下基于两次信息交互的多核处理器容错方法,消除单点隐患,降低系统设计复杂度,提高容错效率。

2、本发明的技术解决方案是:

3、一种amp模式下基于两次信息交互的多核处理器容错方法,包括:

4、(1)进入表决前完成处理,处理结果写入共享存储区域;

5、在处理阶段,核i完成处理任务,将其处理结果result[i]写入共享存储区域核i所属区域,其中,i=0,1,...,n-1。

6、(2)进入表决,t1阶段获取其它核的处理结果;

7、核i从共享存储区域读取其它核存放的处理结果result[0],result[1],...,result[i-1],result[i+1],...,result[n-1],结合自身的处理结果result[i],构成所有处理器核的处理结果集d[i]:

8、d[i]={result[0],result[1],...,result[i],...,result[n-1]}。

9、(3)t2阶段,进行第一次表决,对获取的处理结果信息进行表决,以确定正确的输出结果和对故障核的初步判断;

10、核i对其得到的处理结果集d[i]内的数据进行n取m表决;其中,m为最少非故障核的数量,故障核数量即只要出故障的处理器核数量不超过表决就能得到正确的处理结果final_data[i],并且可以保证表决结果的一致性,即最终正确结果:

11、final_data=final_data[0]=final_data[1]=...=final_data[n-1];

12、在得到正确处理结果final_data的同时,由于取回来的数据与各处理器核对应,因此核i所进行的表决还可以识别出是哪一个或哪几个核发生了故障,从而得到核i对所有核健康状态的判断:health[i]={0,0,...,0};其中,health[i]共有n个元素,分别代表n个核的健康状态,健康状态标志:0表示正常,1表示故障;

13、核i将自己的判断health[i]写入对应的共享存储区域。

14、(4)t3阶段,获取核健康状态信息;

15、核i从共享存储区域读取其它核存放的判断结果

16、health[0],health[1],...,health[i-1],health[i+1],...,health[n-1],结合其自身的判断health[i],得到所有处理器核的判断集:

17、h[i]={health[0],health[1],...,health[i],...,health[n-1]}。

18、(5)t4阶段,进行第二次表决,对各核的判断进行表决,以在多核间达成共识,确定故障核以及当班处理器核;

19、核i对其得到的判断集h[i]内的数据进行n取m表决,其中,m为最少非故障核的数量,故障核数量即只要出故障的处理器核数量不超过表决就能得到正确的判断结果,即对所有处理器核健康状态的正确认识final_health[i]={0,0,...,0},并且可以保证各核表决结果的一致性,即:

20、final_health=final_health[0]=final_health[1]=...=

21、final_health[n-1];

22、核i根据final_health和优先级确定应该输出正确处理结果的当班核的编号k,k=0,1,...,n-1,并且可以保证各核确定结果的一致性;

23、(6)在表决完成后,由表决结果确定的处理器核负责对外通信,即核k输出正确处理结果,随后进入下一次循环。

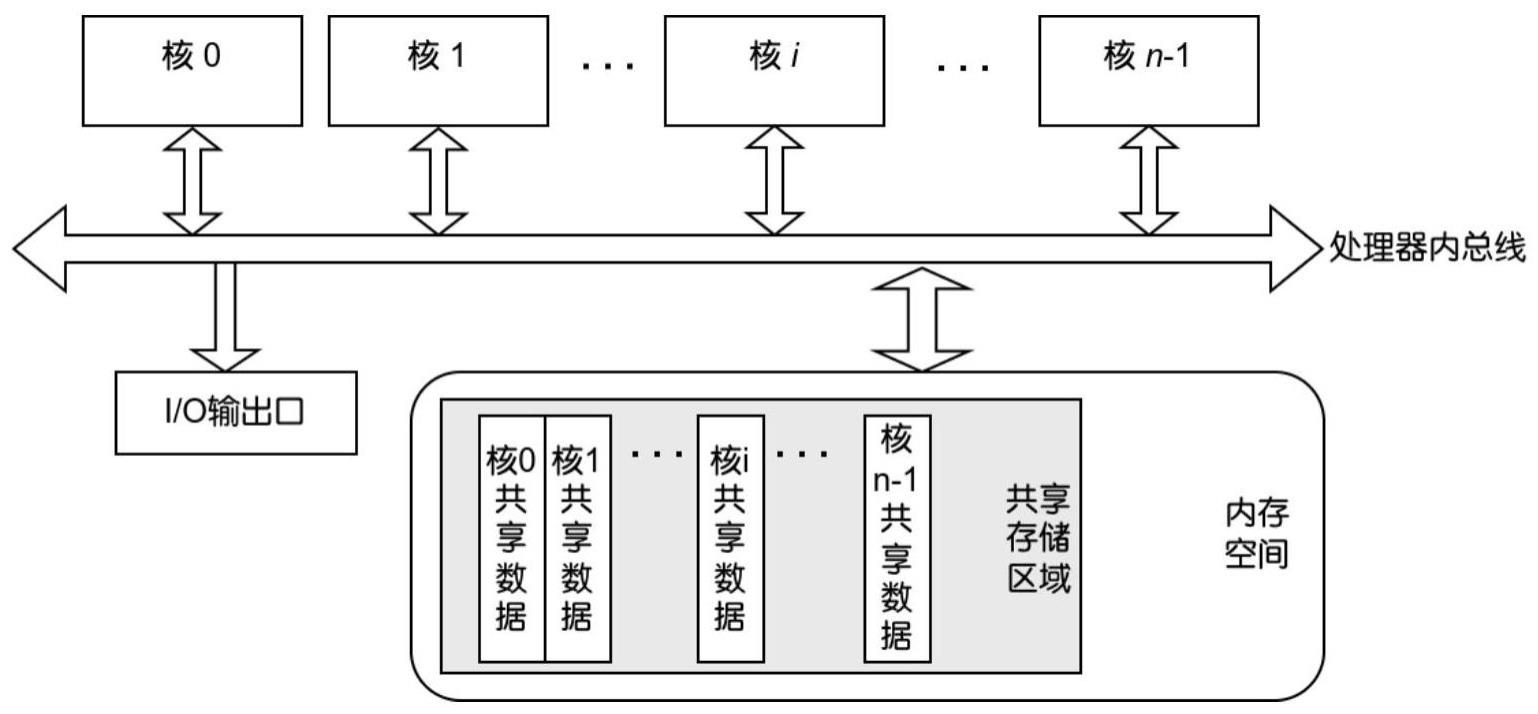

24、进一步的,处理器共有n>2个核,各核编号分别为0,1,2,...,n-1,编号为i的处理器核称为核i;各核通过处理器内部总线互联,同时内部总线也挂载着存储器及处理器与外部通信的i/o接口;处理器核通过内部总线对存储器与i/o接口进行读写访问。

25、进一步的,在存储器内存空间里开辟一块共享存储区域,每一个核都在其中拥有一块自己的区间,用以存储各自的处理输出和判断信息,且可以读取整个共享存储空间的数据;所有的处理器核都可通过对共享存储区域的访问来实现相互间的信息交换。

26、进一步的,amp模式下,各核执行相同的任务。每个核上的任务均划分为处理、表决、输出三个阶段,各处理器核在同步机制约束下,同时进入处理、表决、输出阶段;处理阶段同样的输入,执行同样的任务,理论上得到同样的处理结果。表决划分为四个子阶段:t1、t2、t3、t4,分别进行处理数据交换、处理数据表决、判断信息交换、判断表决。

27、进一步的,按照各核编号从小到大的顺序设置优先级,编号越小,优先级越高;即核0优先级最高,核n-1优先级最低,只要核0健康,对外输出都由核0进行。

28、本发明与现有技术相比的有益效果是:

29、(1)本发明在amp模式下程序编写时设计有表决阶段,并预设处理器核的输出优先级顺序。

30、(2)本发明进入表决阶段后通过两次表决和信息交换,增加故障核判据,更加准确地识别故障核位置。

31、(3)本发明每一个核都可获得其它处理器核的处理结果,每一个核各自独立进行表决。第一次交换处理信息并表决,以确定正确的输出结果和对故障核的初步判断。第二次交换判断信息并表决,以在多核间达成共识:哪个核故障,应该由哪个处理器核当班。

32、(4)在表决完成后,由表决结果确定的处理器核负责对外通信,输出处理结果。通过上述过程,消除单点隐患,降低系统设计复杂度,提高容错效率。

33、(5)本发明容错方法消除了表决单点隐患。本发明没有单独的表决器,表决在每个处理器核内部进行,消除了表决器单点故障造成表决失效的隐患,提高了系统可靠性。

34、(6)本发明容错方法提高了故障处理器核定位准确度。通过两次信息交换,增加了故障核的判据,可以更为准确地确定故障核位置。

35、(7)本发明容错方法提高了处理器系统容错效率。通过共享存储空间交换信息,系统设计复杂度低,信息交互速度快,资源利用率高。

- 还没有人留言评论。精彩留言会获得点赞!