一种降低芯片设计中静态功耗的方法与流程

本发明涉及集成电路,具体涉及一种降低芯片设计中静态功耗的方法。

背景技术:

1、随着集成电路设计规模越来越大,功耗已经成为设计芯片中考虑的一大重点,根据芯片设计,功耗分为如图1所示的动态功耗(dynamic power)和静态功耗(即漏电功耗,leakage power),其中动态功耗包括短路功耗(internalpower)以及开关功耗(switchingpower)。短路功耗表示电路从0-1之间信号跳变,nmos(n沟道场效应管)和pmos(p沟道场效应管)同时导通瞬间所产生的电流从而产生的功耗。开关功耗表示mos管(场效应管)对寄生负载进行充放电所产生的功耗。漏电功耗包括电路没有工作时由于晶体管扩散区和衬底之间存在反偏pn节电流产生的功耗,其大小主要取决于晶体管的状态和电源电压。漏电功耗还包括晶体管源极和漏极之间的亚阈值电流(晶体管在关断时实际并没有完全关闭,仍有电流)产生的功耗,其大小取决于晶体管的阈值电压和温度,工艺尺寸越小,阈值电压越小,漏电流越大;温度越高,漏电流越大。漏电功耗在整个芯片中漏电功耗的占比越来越大,所以在芯片设计中改善漏电功耗成为一个设计重点。

2、在整个芯片上,数字处理模块中晶体管的占比相比其他模块更大,因此改善漏电功耗需要减少数字模块内部的晶体管数量,然而数字模块内部大部分标准单元(standardcell,sc)为了实现功能是难以削减的,所以在设计版图时如何减少修正单元的插入是需要重点关注的。修正单元包括反相器(inverter)、缓冲器(buffer)和延时器(delay)。

3、数字处理模块版图设计过程中,需要验证触发器(flipflop)之间的建立时间(setuptime)和保持时间(holdtime)是否满足,然而如果存在保持时间违例(即hold违例),就需要插入延时器、缓冲器或者是偶数个反相器增加延时,以修正hold违例。违例量越多,插入的单元就越多,插入的越多对于漏电功耗的恶化就更加严重。

技术实现思路

1、本技术的目的在于提供一种降低芯片设计中静态功耗的方法,解决了现有技术因为消除hold违例,大量插入反相器、缓冲器以及延时器,导致漏电功耗增加较多的问题。

2、本发明通过下述技术方案实现:

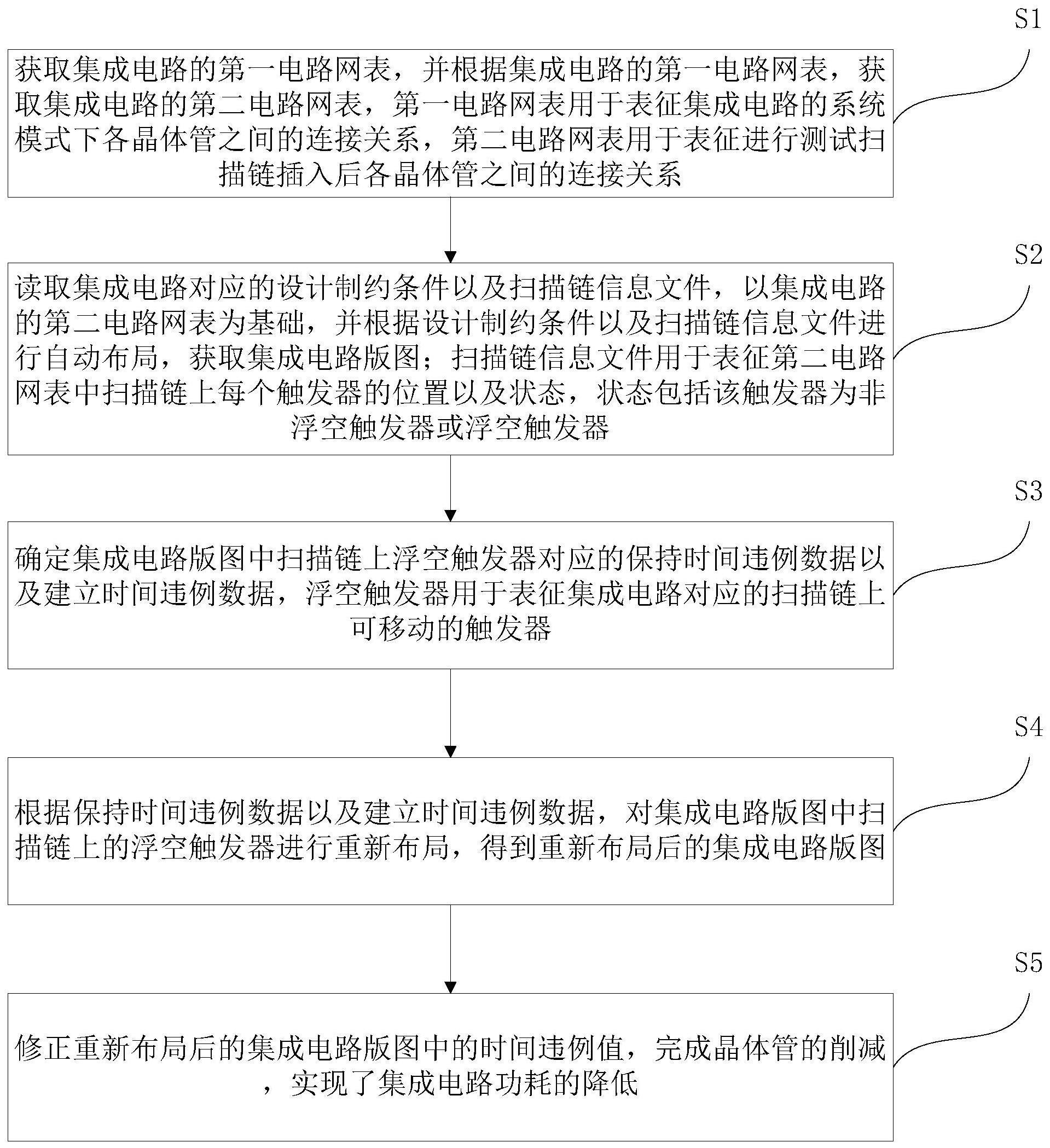

3、一种降低芯片设计中静态功耗的方法,包括:

4、获取集成电路的第一电路网表,并根据集成电路的第一电路网表,获取集成电路的第二电路网表,所述第一电路网表用于表征集成电路的系统模式下各晶体管之间的连接关系,所述第二电路网表用于表征进行测试扫描链插入后各晶体管之间的连接关系;

5、读取集成电路对应的设计制约条件以及扫描链信息文件,以集成电路的第二电路网表为基础,并根据设计制约条件以及扫描链信息文件进行自动布局,获取集成电路版图;所述扫描链信息文件用于表征第二电路网表中扫描链上每个触发器的位置以及状态,所述状态包括该触发器为非浮空触发器或浮空触发器;

6、确定集成电路版图中扫描链上浮空触发器对应的保持时间违例数据以及建立时间违例数据,所述浮空触发器用于表征集成电路对应的扫描链上可移动的触发器;

7、根据所述保持时间违例数据以及建立时间违例数据,对集成电路版图中扫描链上的浮空触发器进行重新布局,得到重新布局后的集成电路版图;

8、修正重新布局后的集成电路版图中的时间违例值,完成晶体管的削减,实现了集成电路静态功耗的降低。

9、在一种可能的实施方式中,根据集成电路的第一电路网表,获取集成电路的第二电路网表,包括:对集成电路的第一电路网表进行扫描链的插入,得到集成电路的第二电路网表。

10、在一种可能的实施方式中,读取集成电路对应的设计制约条件以及扫描链信息文件,以集成电路的第二电路网表为基础,并根据设计制约条件以及扫描链信息文件进行自动布局,获取集成电路版图,包括:

11、读取集成电路对应的设计制约条件以及扫描链信息文件;

12、以集成电路的第二电路网表为基础,从元件库中拉取第二电路网表中的标准单元,所述标准单元用于表征第二电路网表的晶体管;

13、根据第二电路网表、第二电路网表对应的标准单元、设计制约条件以及扫描链信息文件,采用eda进行自动布局,得到集成电路版图。

14、在一种可能的实施方式中,确定集成电路版图中扫描链上浮空触发器对应的保持时间违例数据以及建立时间违例数据之前,还包括:针对集成电路版图,进行时钟树综合。

15、在一种可能的实施方式中,确定集成电路版图中扫描链上浮空触发器对应的保持时间违例数据以及建立时间违例数据,包括:

16、以时钟树综合后的集成电路版图为基础,建立system模式对应的第一仿真场景以及scan模式对应的第二仿真场景,所述第一仿真场景以及第二仿真场景的可调参数设置为电压以及温度;

17、读取第一仿真场景对应的第一时序制约,并以第一时序制约约束后的第一仿真场景为基础,采用器件最大延迟条件验证建立时间约束以及采用器件延迟最小条件验证保持时间约束,得到system模式对应的建立时间验证结果以及保持时间验证结果;所述最大延迟条件用于表征调整第一仿真场景的电压以及温度,使集成电路的延迟到达最大值;所述器件延迟最小条件用于表征调整第一仿真场景的电压以及温度,使集成电路的延迟到达最小值;

18、读取第二仿真场景对应的第二时序制约,并以第二时序制约约束后的第二仿真场景为基础,采用器件最大延迟条件验证建立时间约束以及采用器件延迟最小条件验证保持时间约束,得到scan模式对应的建立时间验证结果以及保持时间验证结果;

19、根据所述system模式对应的建立时间验证结果、system模式对应的保持时间验证结果、scan模式对应的建立时间验证结果以及scan模式对应的保持时间验证结果,确定浮空触发器对应的保持时间违例数据以及建立时间违例数据。

20、在一种可能的实施方式中,根据所述system模式对应的建立时间验证结果、system模式对应的保持时间验证结果、scan模式对应的建立时间验证结果以及scan模式对应的保持时间验证结果,确定浮空触发器对应的保持时间违例数据以及建立时间违例数据,包括:

21、根据system模式对应的保持时间验证结果,确定block_x中保持时间违例的第一时序路径以及第一时序路径对应的第一保持时间违例值;所述block_x用于表征集成电路中将控制模块中触发器的信号转发给子模块中触发器的中间单元;

22、针对每条保持时间违例的第一时序路径,确定该第一时序路径起始点对应的浮空触发器,得到第一目标浮空触发器,并确定每个第一目标浮空触发器对应的第一时钟控制单元,所述时钟控制单元对应至少一个目标浮空触发器;

23、根据system模式对应的保持时间验证结果、第一目标浮空触发器以及第一目标浮空触发器对应的第一时钟控制单元,获取system模式三元信息组,每个第一时钟控制单元对应一个system模式三元信息组,且所述system模式三元信息组包括第一时钟控制单元、第一时钟控制单元下第一目标浮空触发器以及第一目标浮空触发器对应第一时序路径所对应的第一保持时间违例值;

24、根据system模式三元信息组,确定每个第一时钟控制单元对应的保持时间违例最大值、保持时间违例总量以及保持时间违例条数,得到第一目标数组;

25、根据scan模式对应的保持时间验证结果,确定block_x中保持时间违例的第二时序路径以及第二时序路径对应的第二保持时间违例值;

26、针对每条保持时间违例的第二时序路径,确定该第二时序路径起始点对应的浮空触发器,得到第二目标浮空触发器,并确定每个第二目标浮空触发器对应的第二时钟控制单元,所述时钟控制单元对应至少二个目标浮空触发器;

27、根据scan模式对应的保持时间验证结果、第二目标浮空触发器以及第二目标浮空触发器对应的第二时钟控制单元,获取scan模式三元信息组,每个第二时钟控制单元对应一个scan模式三元信息组,且所述scan模式三元信息组包括第二时钟控制单元、第二时钟控制单元下第二目标浮空触发器以及第二目标浮空触发器对应第二时序路径所对应的第二保持时间违例值;

28、根据scan模式三元信息组,确定每个第二时钟控制单元对应的保持时间违例最大值、保持时间违例总量以及保持时间违例条数,得到第二目标数组;

29、根据system模式对应的建立时间验证结果,确定block_x中保持时间违例的第一时序路径以及第一时序路径对应的第一最小建立时间余量;

30、根据scan模式对应的建立时间验证结果,确定block_x中保持时间违例的第二时序路径以及第二时序路径对应的第二最小建立时间余量;

31、将第一目标数组以及第二目标数组的数据共同作为保持时间违例数据,将第一最小建立时间余量以及第二最小建立时间余量共同作为建立时间违例数据。

32、在一种可能的实施方式中,根据所述保持时间违例数据以及建立时间违例数据,对集成电路版图中扫描链上的浮空触发器进行重新布局,得到重新布局后的集成电路版图,包括:

33、根据所述保持时间违例数据以及建立时间违例数据,确定每个时钟控制单元的改善状态,所述改善状态包括允许改善或者不允许改善;

34、根据每个时钟控制单元的改善状态,确定时钟控制单元下待优化的浮空触发器;

35、以待优化的浮空触发器为基础,进行重新布局,得到重新布局后的集成电路版图。

36、在一种可能的实施方式中,根据所述保持时间违例数据以及建立时间违例数据,确定每个时钟控制单元的改善状态,包括:

37、根据保持时间违例数据,确定时钟控制单元在system模式以及scan模式下的保持时间违例总量是否大于第一预设阈值,若是,则对建立时间余量进行验证,否则将该时钟控制单元的改善状态确定为不允许改善;

38、判断system模式下时钟控制单元的第一最小建立时间余量与保持时间违例最大值之间的关系以及scan模式下时钟控制单元的第二最小建立时间余量与保持时间违例最大值之间的关系是否均满足预设条件,若是,则将该时钟控制单元的改善状态确定为允许改善,否则将该时钟控制单元的改善状态确定为不允许改善。

39、在一种可能的实施方式中,以待优化的浮空触发器为基础,进行重新布局,得到重新布局后的集成电路版图,包括:

40、针对每个待优化的浮空触发器,在集成电路版图中对应的浮空触发器的时钟引脚上设置虚拟延迟;

41、基于设置过虚拟延迟后的浮空触发器,对集成电路版图进行时钟树综合,得到时钟树综合后的集成电路版图;

42、根据时钟树综合后的集成电路版图,识别扫描链上存在虚拟延迟的浮动触发器,并针对存在虚拟延迟的浮动触发器,将位于同一扫描链且位于同一时钟控制单元下的浮动触发器聚集在一起,以对扫描链进行优化,获取重新布局后的集成电路版图。

43、在一种可能的实施方式中,修正重新布局后的集成电路版图中的时间违例值,包括:

44、验证重新布局后集成电路版图中扫描链的保持时间约束,确定保持时间违例值;

45、根据所述保持时间违例值,确定修复时序路径的保持时间违例值所需的修正单元;

46、根据修复时序路径的保持时间违例值所需的修正单元,在时序路径上插入对应的修正单元,完成晶体管的削减,实现了集成电路静态功耗的降低。

47、本技术提供的一种降低芯片设计中静态功耗的方法,针对现有集成电路版图设计中插入大量修正单元导致漏电功耗增加的问题,利用修改scanchain(把多个触发器串联起来形成扫描链)中触发器的位置,改善时钟线上的共同路径,从而改善hold违例,削减了修正单元的插入量,达到改善漏电功耗的效果。

- 还没有人留言评论。精彩留言会获得点赞!