慢时钟域到快时钟域数据同步方法及数据同步系统与流程

本发明涉及跨时钟域数据处理领域,特别是涉及一种慢时钟域到快时钟域数据同步方法及数据同步系统。

背景技术:

1、随着芯片行业的迅猛发展,同一颗芯片中不同时钟域的模块越来越多,而不同时钟域之间的数据在进行交互时,如果不进行同步处理,数据将出现亚稳态,并在芯片内部传播,对芯片整体架构造成不可预期的危害。

2、为了解决不同时钟域数据同步的问题,常用数据缓存器10(first input firstoutput,fifo)对跨时钟域的数据进行读取和存储。数据缓存器10的工作方式如图1所示,第一模块11输出写入指令w_req到数据缓冲器10并输出在第一时钟clk_a下的第一数据信号data_a,数据缓存器10接收到写入指令w_req写入第一数据信号data_a;第二模块12输出读取指令r_req,数据缓存器10接收到第二模块12的读取指令,将存储在内部的第一数据信号data_a作为第二数据信号data_b输出到第二模块12。以上过程执行完毕,就实现了第一模块11的数据传输到第二模块12,且不会因为直接交换出现跨时钟的亚稳态问题。

3、但是当慢时钟域和快时钟域之间相差较大,如10倍以上,使用数据缓存器10对不同模块进行数据同步时会有很大的延迟,使得数据同步效率变低。除此之外,数据缓存器10的占用资源也较多,不利于功耗、资源进一步的减少。

4、基于以上原因,本发明提供了一种慢时钟域到快时钟域数据同步方法,用以解决慢时钟域到快时钟域使用数据缓存器延迟大、同步效率低等问题。

5、应该注意,上面对技术背景的介绍只是为了方便对本技术的技术方案进行清楚、完整的说明,并方便本领域技术人员的理解而阐述的。不能仅仅因为这些方案在本技术的背景技术部分进行了阐述而认为上述技术方案为本领域技术人员所公知。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种慢时钟域到快时钟域数据同步方法及数据同步系统,用于解决现有技术中慢时钟域到快时钟域使用数据缓存器延迟大、同步效率低等问题。

2、为实现上述目的及其他相关目的,本发明提供一种慢时钟域到快时钟域数据同步方法,包括:

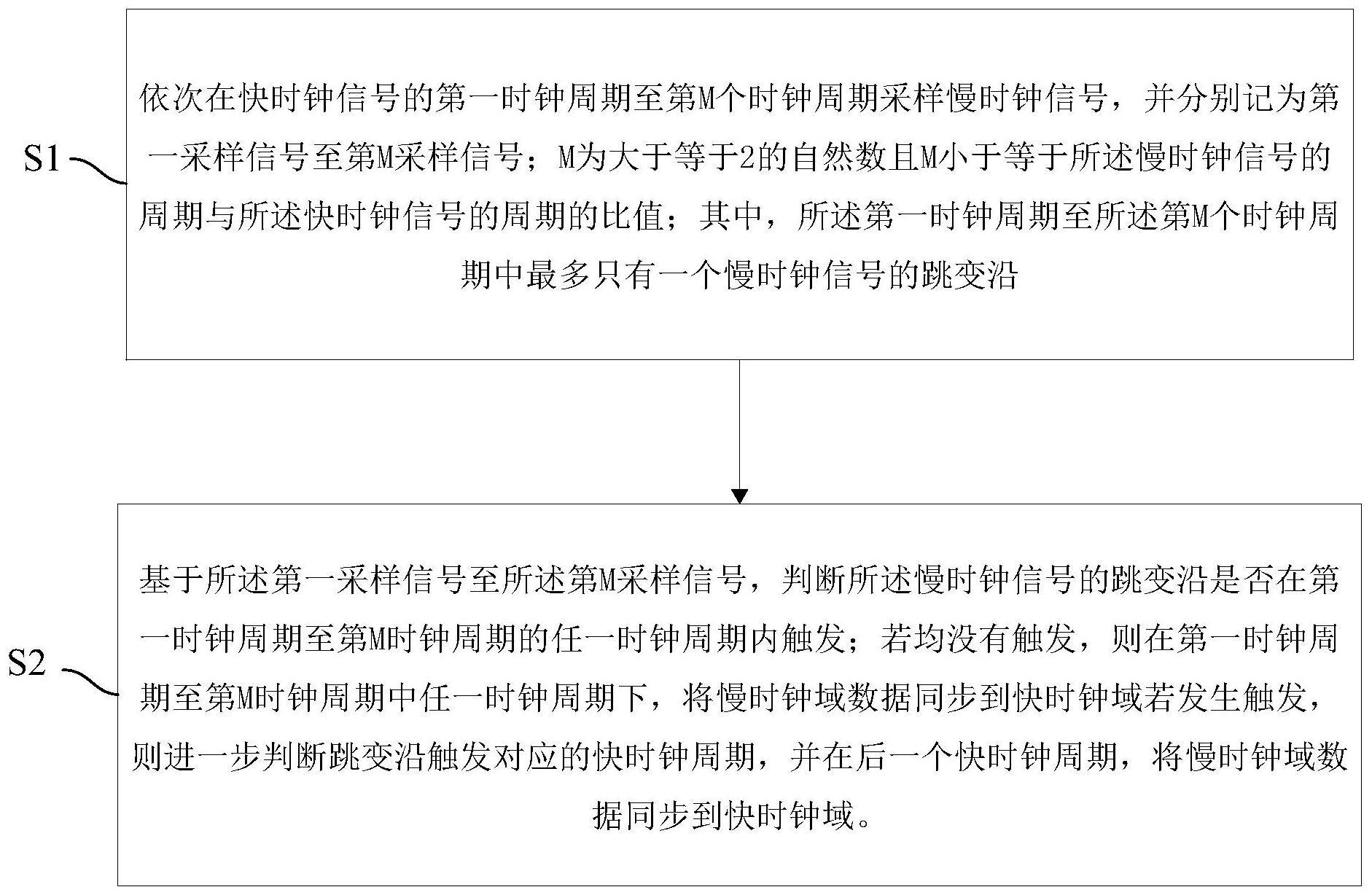

3、s1、依次在快时钟信号的第一时钟周期至第m个时钟周期采样慢时钟信号,并分别记为第一采样信号至第m采样信号;m为大于等于2的自然数且m小于等于所述慢时钟信号的周期与所述快时钟信号的周期的比值;其中,所述第一时钟周期至所述第m个时钟周期中最多只有一个慢时钟信号的跳变沿;

4、s2、基于所述第一采样信号至所述第m采样信号,判断所述慢时钟信号的跳变沿是否在第一时钟周期至第m时钟周期的任一时钟周期内触发;若均没有触发,则在第一时钟周期至第m时钟周期中任一时钟周期下,将慢时钟域数据同步到快时钟域若发生触发,则进一步判断跳变沿触发对应的快时钟周期,并在后一个快时钟周期,将慢时钟域数据同步到快时钟域。

5、可选地,所述快时钟信号为上升沿触发或下降沿触发。

6、可选地,在步骤s2前还设置有预同步步骤,包括:当m=2时,在第一时钟周期下,将慢时钟域数据同步到快时钟域作为快时钟域数据;当m=3时,在第二时钟周期下,将慢时钟域数据同步到快时钟域作为快时钟域数据。

7、可选地,当m=2且所述慢时钟信号为上升沿触发时,若在快时钟信号的第一时钟周期和第二时钟周期采集到慢时钟信号的下降沿,则将第二时钟周期下的慢时钟域数据同步到快时钟域;若在快时钟信号的第一时钟周期和第二时钟周期采集到慢时钟信号的上升沿,则将第三时钟周期下的慢时钟域数据同步到快时钟域;若在快时钟信号的第一时钟周期和第二时钟周期采集到慢时钟信号持续高电平状态,则将第二时钟周期下的慢时钟域数据同步到快时钟域;若在快时钟信号的第一时钟周期和第二时钟周期采集到慢时钟信号持续低电平状态,保留预同步步骤中的所述快时钟域数据。

8、可选地,s20a、在第一时钟周期,将慢时钟域数据同步到快时钟域;s21a、在第二时钟周期,判断采样得到的所述第一采样信号的电平;当所述第一采样信号为高电平时,则将第二时钟周期的慢时钟域数据同步到快时钟域;当所述第一采样信号为低电平时,则保留步骤s20a的快时钟域数据;s22a、在第三时钟周期,判断采样得到的所述第一采样信号及所述第二采样信号的电平;若采样得到的所述第一采样信号为低电平且所述第二采样信号为高电平,则将慢时钟域数据同步到快时钟域;若采样得到的所述第一采样信号为低电平且所述第二采样信号为低电平,则保留步骤s20a的快时钟域数据。

9、可选地,当m等于2且所述慢时钟信号为下降沿触发时,若在快时钟信号的第一时钟周期和第二时钟周期采集到慢时钟信号的上升沿,则将第二时钟周期下的慢时钟域数据同步到快时钟域;若在快时钟信号的第一时钟周期和第二时钟周期采集到慢时钟信号的下降沿,则将第三时钟周期下的慢时钟域数据同步到快时钟域;若在快时钟信号的第一时钟周期和第二时钟周期采集到慢时钟信号持续低电平状态,则将第二时钟周期下的慢时钟域数据同步到快时钟域;若在快时钟信号的第一时钟周期和第二时钟周期采集到慢时钟信号持续高电平状态,保留预同步步骤中的快时钟域数据。

10、可选地,s20b、在第一时钟周期,将慢时钟域数据同步到快时钟域;s21b、在第二时钟周期,判断采样得到的所述第一采样信号的电平;当所述第一采样信号为低电平时,则将第二时钟周期的慢时钟域数据同步到快时钟域;当所述第一采样信号为高电平时,则保留步骤s20b的快时钟域数据;s22b、在第三时钟周期,判断是否采样得到的所述第一采样信号及所述第二采样信号的电平;若采样得到的所述第一采样信号为高电平且所述第二采样信号为低电平,则将慢时钟域数据同步到快时钟域;若采样得到的所述第一采样信号为高电平且所述第二采样信号为高电平,则保留步骤s20b的快时钟域数据。

11、可选地,s20c,在第一时钟周期,采样慢时钟信号作为第一采样信号;s21c、在第二时钟周期,采样慢时钟信号作为第二采样信号;将慢时钟域数据同步到快时钟域;s22c、在第三时钟周期,判断采样得到的所述第一采样信号及所述第二采样信号的电平;若所述第一采样信号的电平和所述第二采样信号的电平不相等,则将第三时钟周期下的慢时钟域数据同步到快时钟域;若所述第一采样信号的电平和所述第二采样信号的电平相等,则保留步骤s21c中的快时钟域数据;s23c、在第四时钟周期,判断采样得到的所述第一采样信号、所述第二采样信号及所述第三采样信号的电平;若所述第一采样信号的电平和所述第二采样信号的电平相等且所述第二采样信号的电平和所述第三采样信号的电平不相等,则将第四时钟周期下的慢时钟域数据同步到快时钟域;若所述第一采样信号的电平、所述第二采样信号的电平以及所述第三采样信号的电平均相等,则保留步骤s21c中的快时钟域数据。

12、可选地,所述慢时钟信号的周期大于等于10倍的所述快时钟信号的周期。

13、为实现上述目的及其他相关目的,本发明提供一种慢时钟域到快时钟域数据同步系统,用于实现所述的慢时钟域到快时钟域数据同步方法包括:快时钟域模块、慢时钟域模块、时钟信号采样模块以及数据同步模块;

14、快时钟域模块、慢时钟域模块、时钟信号采样模块以及数据同步模块;

15、所述时钟信号采样模块接收所述快时钟域模块的快时钟信号及所述慢时钟域模块的慢时钟信号,基于所述快时钟信号的第一时钟周期至第m时钟周期依次采样慢时钟信号;

16、所述数据同步模块的输入端连接所述时钟信号采样模块的输出信号,用于判断所述慢时钟信号的跳变沿是否在第一时钟周期至第m时钟周期的任一时钟周期内触发并基于判断结果控制所述慢时钟域模块的数据同步到所述快时钟域模块。

17、可选地,所述时钟信号采样模块包括计数器和采样单元;所述计数器接收所述快时钟域模块的快时钟信号,输出端连接所述采样单元的控制端,用于控制所述采样单元的采样次数;其中所述计数器的计数周期大小等于所述快时钟域模块的时钟信号的周期大小;所述采样单元的输入端连接所述慢时钟域模块的时钟信号输出端,基于所述计数器的输出信号对所述慢时钟域模块的时钟信号依次采样并将结果输出到所述判定单元的输入端。

18、可选地,所述时钟信号采样模块还包括计数触发器;所述计数触发器的输入端连接所述快时钟域模块,输出端连接所述计数器的控制端,用于为所述计数器提供计数的触发信号。

19、可选地,所述数据同步模块设置为状态机。

20、可选地,所述数据同步模块包括判定单元以及同步单元;所述判定单元的输入端连接所述时钟信号采样模块的输出信号,用于判定所述慢时钟信号的跳变沿是否在第一时钟周期至第m时钟周期的任一时钟周期内触发;所述同步单元的控制端连接所述判定单元的输出信号,输入端连接所述慢时钟域模块的数据输出端,输出端连接所述快时钟域模块的数据输入端,基于所述判定单元的判定结果控制所述慢时钟域模块的数据同步到所述快时钟域模块。

21、如上所述,本发明的慢时钟域到快时钟域数据同步方法及数据同步系统,具有以下有益效果:

22、1、本发明的慢时钟域到快时钟域数据同步方法及数据同步系统无需使用数据缓存器fifo进行跨时钟域数据信号同步,大大缩短了慢时钟域到快时钟域数据同步的时间,节省了资源,提高了数据同步的效率并防止了亚稳态。

23、2、本发明的慢时钟域到快时钟域数据同步方法及数据同步系统结构简单、方法简便,最快能在三个快时钟周期内实现跨时钟域的数据同步,能在跨时钟域应用领域进行大规模的推广应用。

- 还没有人留言评论。精彩留言会获得点赞!